(19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4077966号 (P4077966)

(45) 発行日 平成20年4月23日(2008.4.23)

(24) 登録日 平成20年2月8日 (2008.2.8)

(51) Int. Cl. FL

HO1L 21/8242 (2006, 01) HO1L 27/108 (2006, 01)

HO1L 21/822 (2006.01) HO1L 27/04 (2006, 01)

621CHO1L 27/10 П

HO1L 27/04

(全 36 頁) 請求項の数 7

(21) 出願番号 特願平10-369686

(22) 出願日 平成10年12月25日 (1998.12.25) (65) 公開番号 特開2000-196017 (P2000-196017A)

(43) 公開日 平成12年7月14日(2000.7.14) 平成16年6月11日 (2004.6.11) 審查請求日

|(73)特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

|(74)代理人 100080001

弁理士 筒井 大和

(72) 発明者 橋本 孝司

> 東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体事業本部内

|(72)発明者 黒田 謙一

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体事業本部内

|(72)発明者 池田 修二

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体事業本部内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57)【特許請求の範囲】

# 【請求項1】

- (a) メモリセルの選択MISFETが形成される第1領域、周辺回路または論理回路 の第1チャネル型の第1MISFETが形成される第2領域および前記周辺回路または論 理回路の第2チャネル型の第2MISFETが形成される第3領域を有する半導体基板の 主面上に分離領域を形成する工程、

- (b)前記分離領域で囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、前 記半導体基板の全面にシリコン膜を形成する工程、

- (c) 少なくとも前記第 1 領域の前記シリコン膜に第 1 導電型の不純物をイオン注入す る工程、

- (d)前記(c)工程の後、前記シリコン膜上に第1絶縁膜を形成する工程、

- (e) ゲート電極パターンにパターニングされた第1フォトレジスト膜を前記第1絶縁 膜上に形成する工程、

- (f)前記第1フォトレジスト膜の存在下で前記第1絶縁膜およびシリコン膜をエッチ ングし、キャップ絶縁膜およびゲート電極を形成し、前記キャップ絶縁膜およびゲート電 極をマスクとして、前記第1領域と前記第2領域にn型の導電型を示す不純物をイオン注 入して、低濃度のn型半導体領域を形成し、また、前記第3領域にp型の導電型を示す不 純物をイオン注入して、低濃度のp型半導体領域を形成する工程、

- (g)前記ゲート電極およびキャップ絶縁膜を覆い、前記第1絶縁膜に対してエッチン グ選択比を有する第2絶縁膜を堆積し、異方性エッチングにより前記第2絶縁膜をエッチ

10

ングして前記ゲート電極およびキャップ絶縁膜の側壁にサイドウォールを形成する工程、

- (h)前記キャップ絶縁膜およびサイドウォールの存在下で前記半導体基板を熱処理し、前記活性領域の表面に前記第 1 絶縁膜に対してエッチング選択比を有する第 3 絶縁膜を形成する工程、

- (i)前記第3絶縁膜およびサイドウォールの存在下で前記キャップ絶縁膜を選択的に除去する工程、

- (j)前記第1領域を覆う第2フォトレジスト膜を形成し、前記第2フォトレジスト膜の存在下でエッチング処理を施し、前記第2および第3領域の前記第3絶縁膜を除去する T程、

- (k)前記(j)工程の後、前記半導体基板の全面に金属膜を堆積する工程、

- (1)前記半導体基板を熱処理し、前記第1、第2および第3領域の前記ゲート電極の表面ならびに前記第2および第3領域の前記活性領域の表面に前記金属膜を構成する金属のシリサイド膜を形成する工程、

- (m)未反応の前記金属膜を除去する工程、

#### を含み、

前記(g)工程と(h)工程の間に、前記キャップ絶縁膜およびサイドウォールの存在下で、前記第2領域にn型の導電型を示す不純物を<u>高濃度に</u>イオン注入し<u>て、高濃度のn型半導体領域を形成し</u>、また、前記第3領域にp型の導電型を示す不純物を<u>高濃度に</u>イオン注入<u>して、高濃度のp型半導体領域を形成</u>する工程を有することを特徴とする半導体装置の製造方法。

#### 【請求項2】

- (a) メモリセルの選択MISFETが形成される第1領域、周辺回路または論理回路の第1チャネル型の第1MISFETが形成される第2領域および前記周辺回路または論理回路の第2チャネル型の第2MISFETが形成される第3領域を有する半導体基板の主面上に分離領域を形成する工程、

- (b)前記分離領域で囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、前記半導体基板の全面にシリコン膜を形成する工程、

- (c)少なくとも前記第1領域の前記シリコン膜に第1導電型の不純物をイオン注入する工程、

- (d)前記(c)工程の後、前記シリコン膜上に第1絶縁膜を形成する工程、

- (e) ゲート電極パターンにパターニングされた第1フォトレジスト膜を前記第1絶縁膜上に形成する工程、

- (f)前記第1フォトレジスト膜の存在下で前記第1絶縁膜およびシリコン膜をエッチングし、キャップ絶縁膜およびゲート電極を形成し、前記キャップ絶縁膜およびゲート電極をマスクとして、前記第1領域と前記第2領域にn型の導電型を示す不純物をイオン注入して、低濃度のn型半導体領域を形成し、また、前記第3領域にp型の導電型を示す不純物をイオン注入して、低濃度のp型半導体領域を形成する工程、

- (g)前記ゲート電極およびキャップ絶縁膜を覆い、前記第1絶縁膜に対してエッチング選択比を有する第2絶縁膜を堆積し、異方性エッチングにより前記第2絶縁膜をエッチングして前記ゲート電極およびキャップ絶縁膜の側壁にサイドウォールを形成する工程、

- (h)前記キャップ絶縁膜およびサイドウォールの存在下で前記半導体基板を熱処理し、前記活性領域の表面に前記第1絶縁膜に対してエッチング選択比を有する第3絶縁膜を 形成する工程、

- (i)前記第3絶縁膜およびサイドウォールの存在下で前記キャップ絶縁膜を選択的に除去する工程、

- (j)前記第1領域を覆う第2フォトレジスト膜を形成し、前記第2フォトレジスト膜の存在下でエッチング処理を施し、前記第2および第3領域の前記第3絶縁膜を除去する工程、

- ( k ) 前記( j ) 工程の後、前記半導体基板の全面に金属膜を堆積する工程、

- (1)前記半導体基板を熱処理し、前記第1、第2および第3領域の前記ゲート電極の

10

20

40

30

表面ならびに前記第2および第3領域の前記活性領域の表面に前記金属膜を構成する金属のシリサイド膜を形成する工程、

(m)未反応の前記金属膜を除去する工程、

# を含み、

前記(h)工程と(j)工程の間に、前記キャップ絶縁膜<u>および</u>サイドウォー<u>ルの</u>存在下で、前記第2領域にn型の導電型を示す不純物を<u>高濃度に</u>イオン注入し<u>て、高濃度のn型半導体領域を形成し</u>、また、前記第3領域にp型の導電型を示す不純物を<u>高濃度に</u>イオン注入<u>して、高濃度のp型半導体領域を形成</u>する工程を有することを特徴とする半導体装置の製造方法。

# 【請求項3】

10

- (a)第3MISFETが形成される第1領域、論理回路の第1チャネル型の第1MI SFETが形成される第2領域および前記論理回路の第2チャネル型の第2MISFET が形成される第3領域を有する半導体基板の主面上に分離領域を形成する工程、

- (b)前記分離領域で囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、前記半導体基板の全面にシリコン膜を形成する工程、

- (c)少なくとも前記第1領域の前記シリコン膜に第1導電型の不純物をイオン注入する工程、

- (d)前記(c)工程の後、前記シリコン膜上に第1絶縁膜を形成する工程、

- (e)ゲート電極パターンにパターニングされた第1フォトレジスト膜を前記第1絶縁膜上に形成する工程、

20

30

40

- (f)前記第1フォトレジスト膜の存在下で前記第1絶縁膜およびシリコン膜をエッチングし、キャップ絶縁膜およびゲート電極を形成し、前記キャップ絶縁膜およびゲート電極をマスクとして、前記第1領域と前記第2領域にn型の導電型を示す不純物をイオン注入して、低濃度のn型半導体領域を形成し、また、前記第3領域にp型の導電型を示す不純物をイオン注入して、低濃度のp型半導体領域を形成する工程、

- (g)前記ゲート電極およびキャップ絶縁膜を覆い、前記第1絶縁膜に対してエッチング選択比を有する第2絶縁膜を堆積し、異方性エッチングにより前記第2絶縁膜をエッチングして前記ゲート電極およびキャップ絶縁膜の側壁にサイドウォールを形成する工程、

- (h)前記(g)工程の後、前記キャップ絶縁膜およびサイドウォールの存在下で、前記第2領域にn型の導電型を示す不純物を<u>高濃度に</u>イオン注入して、高濃度のn型半導体 <u>領域を形成し</u>、また、前記第3領域にp型の導電型を示す不純物を<u>高濃度に</u>イオン注入して、高濃度のp型半導体領域を形成する工程、

- (i)前記(h)工程の後、前記キャップ絶縁膜およびサイドウォールの存在下で前記 半導体基板を熱処理し、前記活性領域の表面に前記第1絶縁膜に対してエッチング選択比 を有する第3絶縁膜を形成する工程、

- (j)前記第3絶縁膜およびサイドウォールの存在下で前記キャップ絶縁膜を選択的に除去する工程、

- (k)前記第1領域を覆う第2フォトレジスト膜を形成し、前記第2フォトレジスト膜の存在下でエッチング処理を施し、前記第2および第3領域の前記第3絶縁膜を除去する工程、

- (1)前記(k)工程の後、半導体基板の全面に金属膜を堆積する工程、

- (m)<u>前記</u>半導体基板を熱処理し、前記第1、第2および第3領域の前記ゲート電極の表面ならびに前記第2および第3領域の前記活性領域の表面に前記金属膜を構成する金属のシリサイド膜を形成する工程、

- (n)未反応の前記金属膜を除去する工程、

を含むことを特徴とする半導体装置の製造方法。

#### 【請求項4】

請求項1~3の何れか一項に記載の半導体装置の製造方法であって、

前記(b)工程におけるシリコン膜はアモルファスシリコン膜であり、前記アモルファスシリコン膜への前記不純物の導入後に熱処理を施し、前記シリコン膜を結晶化すること

を特徴とする半導体装置の製造方法。

# 【請求項5】

- (a) メモリセルの選択MISFETが形成される第1領域、周辺回路または論理回路の第1チャネル型の第1MISFETが形成される第2領域および前記周辺回路または論理回路の第2チャネル型の第2MISFETが形成される第3領域を有する半導体基板の主面上に分離領域を形成する工程、

- (b)前記分離領域で囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、前記半導体基板の全面に第1シリコン膜を堆積する工程、

- (c)前記第1および第2領域の前記第1シリコン膜に第1導電型の不純物をイオン注入し、前記第3領域の前記第1シリコン膜に第2導電型の不純物をイオン注入する工程、

- (d)前記(c)工程の後、前記第1シリコン膜上に、第1導電型の不純物を含む第2シリコン膜を形成する工程、

- (e)前記第2シリコン膜上に第1絶縁膜を堆積する工程、

- (f)ゲート電極のパターンにパターニングされた第1フォトレジスト膜を前記第1絶縁膜上に形成する工程、

- (g)前記第1フォトレジスト膜の存在下で前記第1絶縁膜、第1および第2シリコン膜をエッチングし、前記第1絶縁膜からなるキャップ絶縁膜および前記第1および第2シリコン膜からなるゲート電極を形成し、前記キャップ絶縁膜およびゲート電極をマスクとして、前記第1領域と前記第2領域に第1導電型の不純物をイオン注入して、低濃度の第1導電型半導体領域を形成し、また、前記第3領域に第2導電型の不純物をイオン注入して、低濃度の第2導電型半導体領域を形成する工程、

- (h)前記ゲート電極およびキャップ絶縁膜を覆い、前記第1絶縁膜に対してエッチング選択比を有する第2絶縁膜を堆積し、異方性エッチングにより前記第2絶縁膜をエッチングして前記ゲート電極およびキャップ絶縁膜の側壁にサイドウォールを形成する工程、

- (i)前記キャップ絶縁膜およびサイドウォールの存在下で前記半導体基板を熱処理し、前記分離領域に囲まれた活性領域の表面に前記第1絶縁膜に対してエッチング選択比を有する第3絶縁膜を形成する工程、

- (j)前記第3絶縁膜およびサイドウォールの存在下で前記キャップ絶縁膜を選択的に除去する工程、

- (k)前記ゲート電極、サイドウォールおよび第3絶縁膜の存在下で、前記第2領域に第1導電型の不純物を<u>高濃度に</u>イオン注入し<u>て、高濃度の第1導電型半導体領域を形成し</u>、また、前記第3領域に第2導電型の不純物を<u>高濃度に</u>イオン注入<u>して、高濃度の第2</u>導電型半導体領域を形成する工程、

- (1)前記第1領域を覆う第2フォトレジスト膜を形成し、前記第2フォトレジスト膜の存在下でエッチング処理を施し、前記第2および第3領域の前記第3絶縁膜を除去する工程、

- (m)前記(1)工程の後、前記半導体基板の全面に金属膜を堆積する工程、

- (n)前記半導体基板を熱処理し、前記第1、第2および第3領域の前記ゲート電極の表面ならびに前記第2および第3領域の前記活性領域の表面に前記金属膜を構成する金属のシリサイド膜を形成する工程、

- (o)未反応の前記金属膜を選択的に除去する工程、

を含むことを特徴とする半導体装置の製造方法。

# 【請求項6】

請求項5記載の半導体装置の製造方法であって、

前記(b)工程における第1シリコン膜はアモルファスシリコン膜であり、前記アモルファスシリコン膜への前記不純物の導入後であって前記第2シリコン膜の形成前に熱処理を施し、前記第1シリコン膜を結晶化することを特徴とする半導体装置の製造方法。

# 【請求項7】

請求項1~3、5の何れか一項に記載の半導体装置の製造方法であって、

前記第1絶縁膜はシリコン窒化膜であり、前記第2および第3絶縁膜はシリコン酸化膜

20

10

30

•

40

であることを特徴とする半導体装置の製造方法。

【発明の詳細な説明】

#### [0001]

# 【発明の属する技術分野】

本発明は、半導体装置およびその製造技術に関し、特に、汎用の大容量 DRAM (Dynamic Random Access Memory) あるいは DRAMと高性能なロジック回路とをワンチップに混載した半導体装置に適用して有効な技術に関するものである。

## [0002]

# 【従来の技術】

高性能なロジック回路を実現するためには、それを構成するMISFET (Metal Insula tor Semiconductor Field Effect Transistor )の高性能化、高速化が必要である。また、微細化されたMISFETにおいてはサブスレッショルドリークを低減する必要もある。このため、微細化されたロジック回路用のMISFETでは、いわゆるデュアルゲート構造およびサリサイド技術が採用されている。

#### [0003]

デュアルゲート構造は、たとえば、平成10年8月20日、株式会社プレスジャーナル発行、「月刊 Semiconductor World」、1998年9月号、p76~p81に記載されているように、pチャネル型MISFET(PMIS)のゲート電極としてp<sup>+</sup> ポリシリコンを用い、nチャネル型MISFET(NMIS)のゲート電極としてn<sup>+</sup> ポリシリコンを用いる構造である。このような構造とすることにより、微細化に有利な表面チャネル型のMISFETでCMIS構造を構成でき、サブスレッショルドリークを低減できる。なお、ゲート電極材料とチャネル不純物のプロファイルとの関係については、たとえば、昭和61年2月10日、株式会社培風館発行、「超高速MOSデバイス」、p26~p28に詳しく記載されている。

# [0004]

また、サリサイド技術は、前記「超高速MOSデバイス」、p154~p157に記載されているように、ゲート電極であるポリシリコンの表面とソース・ドレイン領域(不純物半導体領域あるいは不純物拡散層)の表面を同時にシリサイド化する技術であり、ゲート電極とソース・ドレイン領域の低抵抗化を図って、MISFETの応答性能を向上できる

# [00005]

一方、DRAMのメモリセルは、たとえば特開平7-7084号公報に記載されているように、半導体基板の主面上にマトリクス状に配置された複数のワード線と複数のビット線との交点に配置され、1個のメモリセル選択用のMISFET(以下選択MISFETという)とこれに直列に接続された1個の情報蓄積用のキャパシタとで構成されている。選択MISFETは、周囲を素子分離領域で囲まれた活性領域に形成されており、主としてゲート酸化膜、ワード線と一体に構成されたゲート電極およびソース、ドレインを構成する一対の半導体領域で構成されている。ビット線は、選択MISFETの上部に配置され、その延在方向に隣接する2個の選択MISFETによって共有されるソース、ドレインの一方と電気的に接続されている。キャパシタは、同じく選択MISFETの上部に配置され、また、ビット線上部に配置されるいわゆるキャパシタ・オーバー・ビットライン(Capacitor Over Bitline)構造で構成される。キャパシタは上記ソース、ドレインの他方と電気的に接続されている。

# [0006]

一般にDRAMメモリセルの選択MISFETでは、リフレッシュ特性向上の観点からリーク電流の低減が重視される。このため、リーク電流増加の要因となるソース・ドレイン領域表面のシリサイド化は行われない。一方、メモリセルの大容量化に伴うワード線長さの増加、微細化・薄膜化に伴なうゲート電極(ワード線)断面積の低減から、所定の応答性能を確保するためにはゲート電極の抵抗率の低減は不可欠である。このため、一般のDRAMでは、ワード線(ゲート電極)材料としてチタン、タングステン等のシリサイド膜

20

10

30

40

と多結晶シリコン膜との積層膜、あるいは、タングステン等の金属膜、ブロッキング膜および多結晶シリコン膜の積層膜が採用される。これらシリサイド膜あるいはメタル膜により抵抗率の低減を図っている。

### [0007]

【発明が解決しようとする課題】

ところが、ロジック回路とDRAMを1チップに混載するようないわゆるシステムLSIに従来技術を適用すれば、以下のような問題が生じる。

# [00008]

すなわち、DRAMのメモリセル形成領域に、ロジック回路用のMISFET形成プロセスで採用されているサリサイドプロセスを適用すると、メモリセルの選択MISFETのソース・ドレイン領域の表面をもシリサイド化してしまい、選択MISFETのリーク電流を増加する要因となる。これはDRAMのリフレッシュ特性を低下させる恐れがあり好ましくない。逆にサリサイドプロセスを適用せずDRAMのリフレッシュ特性を優先すると、MISFETのゲート電極の抵抗が大きくなり半導体装置の性能を阻害する。

## [0009]

一方、ロジック回路領域に形成されるMISFETに、DRAMで採用されているゲート電極構造つまりシリサイド膜あるいはメタル膜と多結晶シリコン膜との積層構造を採用すると、ゲート電極の抵抗値の問題は回避でき、また、選択MISFETの耐リーク電流は維持されるが、構造上ゲート電極上にシリコン窒化膜等のキャップ絶縁膜を備える必要がある。このような場合、ロジック回路領域での配線形成プロセスにおいてゲート電極と上層配線とを接続する接続孔の開口プロセスがキャップ絶縁膜の存在により変更せざるを得ず、レイアウトルールの変更、設計変更等の必要を生じて好ましくない。

## [0010]

勿論、ロジック回路とDRAMを1チップに混載するような場合でも、各々に最適なMISFET形成プロセスを領域を分けて適用する選択はある。しかし、このような場合には 製造工程が増加し、コスト上昇の観点から採用することは難しい。

#### [0011]

また、ロジック回路とDRAMとを1チップに混載する場合のその他の問題点が存在する。すなわち、ゲート電極表面にシリサイド膜が形成され、そのシリサイド膜形成後に高い温度の熱工程が介在する場合には、シリサイド膜内の金属原子がゲート絶縁膜に拡散し、ゲート絶縁膜の耐圧を低下させるという問題が存在する。従来のロジック回路プロセスにおいては、MISFETの形成後、層間絶縁膜および配線形成等の工程が存在したが、これらの工程では特に高い温度の加熱プロセスは存在していなかった。このため、シリサイド膜内の金属原子のゲート絶縁膜への拡散という問題は生じなかった。ところが、ロジック回路とDRAMとを混載するプロセスでは、MISFETの形成後にメモリセルのキャパシタ形成工程が存在し、このキャパシタ形成工程におけるキャパシタ絶縁膜の形成工程では高い温度の熱処理を必要とする。特に酸化タンタル膜等高誘電率の金属酸化膜を適用する場合には高い温度の結晶化工程が介在する。このような熱処理により前記のような金属原子の拡散が生じる可能性があり、MISFETのゲート絶縁膜の耐圧低下の要因となる可能性がある。

# [0012]

本発明の目的は、ロジック回路あるいはDRAMの周辺回路のMISFETの高い性能を維持しつつ、DRAMメモリセルのMISFETのリーク電流を低減し、良好なDRAMのリフレッシュ特性を実現できる技術を提供することにある。

#### [0013]

また、本発明の目的は、ロジック回路あるいはDRAMの周辺回路のMISFETとメモリセルの選択MISFETとに要求される相反する要求を低コストで実現できる技術を提供することにある。

# [0014]

また、本発明の目的は、ロジック回路あるいはDRAMの周辺回路のMISFETとメモ

10

20

30

40

リセルの選択MISFETが1チップに混載されている場合にも良好な信頼性を実現できる技術を提供することにある。

#### [0015]

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### [0016]

【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

# [0017]

(1) 本発明の半導体装置の製造方法は、(a) メモリセルの選択MISFETが形成さ れる第1領域、周辺回路または論理回路の第1チャネル型の第1MISFETが形成され る第2領域および周辺回路または論理回路の第2チャネル型の第2MISFETが形成さ れる第3領域を有する半導体基板の主面上に分離領域を形成する工程、(b)分離領域で 囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、半導体基板の全面にシリコ ン膜を形成する工程、(c)少なくとも第1領域のシリコン膜に第1導電型の不純物をイ オン注入する工程、( d ) シリコン膜上に第 1 絶縁膜を形成する工程、( e ) ゲート電極 パターンにパターニングされた第1フォトレジスト膜を第1絶縁膜上に形成する工程、( f) 第1フォトレジスト膜の存在下で第1絶縁膜およびシリコン膜をエッチングし、キャ ップ絶縁膜およびゲート電極を形成する工程、(g)ゲート電極およびキャップ絶縁膜を 覆い、第1絶縁膜に対してエッチング選択比を有する第2絶縁膜を堆積し、異方性エッチ ングにより第2絶縁膜をエッチングしてゲート電極およびキャップ絶縁膜の側壁にサイド ウォールを形成する工程、(h)キャップ絶縁膜およびサイドウォールの存在下で半導体 基板を熱処理し、活性領域の表面に第1絶縁膜に対してエッチング選択比を有する第3絶 縁膜を形成する工程、(i)第3絶縁膜およびサイドウォールの存在下でキャップ絶縁膜 を選択的に除去する工程、( j ) 第1領域を覆う第2フォトレジスト膜を形成し、第2フ ォトレジスト膜の存在下でエッチング処理を施し、第2および第3領域の第3絶縁膜を除 去する工程、(k)半導体基板の全面に金属膜を堆積する工程、(1)半導体基板を熱処 理し、第1、第2および第3領域のゲート電極の表面ならびに第2および第3領域の活性 領域の表面に金属膜を構成する金属のシリサイド膜を形成する工程、(m)未反応の金属 膜を除去する工程、を含むものである。

# [0018]

(2)本発明の半導体装置の製造方法は、前記項(1)記載の半導体装置の製造方法であって、(g)工程と(h)工程の間に、キャップ絶縁膜およびサイドウォールの存在下で、第2領域にn型の導電型を示す不純物を高濃度にイオン注入し、また、第3領域にp型の導電型を示す不純物を高濃度にイオン注入する工程を有するものである。

# [0019]

(3) 本発明の半導体装置の製造方法は、前記項(1) 記載の半導体装置の製造方法であって、(h) 工程と(j) 工程の間に、キャップ絶縁膜またはゲート電極、サイドウォールおよび第3 絶縁膜の存在下で、第2 領域にn型の導電型を示す不純物を高濃度にイオン注入し、また、第3 領域にp型の導電型を示す不純物を高濃度にイオン注入する工程を有するものである。

# [0020]

(4) 本発明の半導体装置の製造方法は、前記項(1) ~ (3) 記載の半導体装置の製造方法であって、(c) 工程において、同時に第2領域のシリコン膜にn型の導電型を示す不純物をイオン注入し、(c) 工程に前後して、第3領域のシリコン膜にp型の導電型を示す不純物をイオン注入する工程を有するものである。

#### [0021]

(5) 本発明の半導体装置の製造方法は、前記項(3) 記載の半導体装置の製造方法であって、イオン注入により、第2領域のゲート電極にn型の導電型を示す不純物を導入し、

10

20

30

40

または、第3領域のゲート電極にp型の導電型を示す不純物を導入するものである。

# [0022]

(6)本発明の半導体装置の製造方法は、前記項(1)~(5)の何れか一項に記載の半導体装置の製造方法であって、(b)工程におけるシリコン膜はアモルファスシリコン膜であり、アモルファスシリコン膜への不純物の導入後に熱処理を施し、シリコン膜を結晶化するものである。

#### [0023]

(7)本発明の半導体装置の製造方法は、(a)メモリセルの選択MISFETが形成さ れる第1領域、周辺回路または論理回路の第1チャネル型の第1MISFETが形成され る第2領域および周辺回路または論理回路の第2チャネル型の第2MISFETが形成さ れる第3領域を有する半導体基板の主面上に分離領域を形成する工程、(b)分離領域で 囲まれた半導体基板主面の活性領域にゲート絶縁膜を形成し、半導体基板の全面に第1シ リコン膜を堆積する工程、(c)第1および第2領域の第1シリコン膜に第1導電型の不 純物をイオン注入し、第3領域の第1シリコン膜に第2導電型の不純物をイオン注入する 工程、(d)第1シリコン膜上に、第1導電型の不純物を含む第2シリコン膜を形成する 工程、(e)第2シリコン膜上に第1絶縁膜を堆積する工程、(f)ゲート電極のパター ンにパターニングされた第1フォトレジスト膜を第1絶縁膜上に形成する工程、(g)第 1 フォトレジスト膜の存在下で第 1 絶縁膜、第 1 および第 2 シリコン膜をエッチングし、 第1絶縁膜からなるキャップ絶縁膜および第1および第2シリコン膜からなるゲート電極 を形成する工程、(h)ゲート電極およびキャップ絶縁膜を覆い、第1絶縁膜に対してエ ッチング選択比を有する第2絶縁膜を堆積し、異方性エッチングにより第2絶縁膜をエッ チングしてゲート電極およびキャップ絶縁膜の側壁にサイドウォールを形成する工程、( i)キャップ絶縁膜およびサイドウォールの存在下で半導体基板を熱処理し、分離領域に 囲まれた活性領域の表面に第1絶縁膜に対してエッチング選択比を有する第3絶縁膜を形 成する工程、( j ) 第 3 絶縁膜およびサイドウォールの存在下でキャップ絶縁膜を選択的 に除去する工程、(k)ゲート電極、サイドウォールおよび第3絶縁膜の存在下で、第2 領域に第1導電型の不純物を高濃度にイオン注入し、また、第3領域に第2導電型の不純 物を高濃度にイオン注入する工程、(1)第1領域を覆う第2フォトレジスト膜を形成し 、第2フォトレジスト膜の存在下でエッチング処理を施し、第2および第3領域の第3絶 縁膜を除去する工程、(m)半導体基板の全面に金属膜を堆積する工程、(n)半導体基 板を熱処理し、第1、第2および第3領域のゲート電極の表面ならびに第2および第3領 域の活性領域の表面に金属膜を構成する金属のシリサイド膜を形成する工程、(o)未反 応の金属膜を選択的に除去する工程、を含むものである。

## [0024]

(8) 本発明の半導体装置の製造方法は、前記項(7) 記載の半導体装置の製造方法であって、(b) 工程における第1シリコン膜はアモルファスシリコン膜であり、アモルファスシリコン膜への不純物の導入後であって第2シリコン膜の形成前に熱処理を施し、第1シリコン膜を結晶化するものである。

# [0025]

(9) 本発明の半導体装置の製造方法は、前記項(7) または(8) 記載の半導体装置の製造方法であって、第1シリコン膜の形成後に、第1シリコン膜の表面に自然酸化膜を形成するものである。

# [0026]

(10)本発明の半導体装置の製造方法は、(a)半導体基板の主面上にゲート絶縁膜および多結晶または非晶質のシリコン膜を順次形成する工程、(b)シリコン膜上に第1絶縁膜を堆積する工程、(c)第1絶縁膜上にゲート電極パターンにパターニングされたフォトレジスト膜を形成し、フォトレジスト膜の存在下で第1絶縁膜およびシリコン膜をエッチングし、ゲート電極およびゲート電極上のキャップ絶縁膜を形成する工程、(d)半導体基板の全面に第1絶縁膜に対してエッチング選択比を有する第2絶縁膜を堆積し、第2絶縁膜を異方性エッチングすることによりキャップ絶縁膜およびゲート電極の側壁にサ

10

20

30

40

イドウォールを形成する工程、(e)キャップ絶縁膜およびサイドウォールの存在下で半導体基板に熱処理を施し、分離領域に囲まれた活性領域の表面に第 1 絶縁膜に対してエッチング選択比を有する第 3 絶縁膜を形成する工程、(f)第 3 絶縁膜およびサイドウォールの存在下でキャップ絶縁膜を選択的に除去する工程、(g)半導体基板の全面に金属膜を堆積する工程、(h)半導体基板を熱処理し、ゲート電極の表面に金属膜を構成する金属のシリサイド膜を形成する工程、(i)未反応の金属膜を除去する工程、を含むものである。

## [0027]

(11) 本発明の半導体装置の製造方法は、前記項(1)~(10)の何れか一項に記載の半導体装置の製造方法であって、第1絶縁膜はシリコン窒化膜であり、第2および第3 絶縁膜はシリコン酸化膜であるものである。

[0028]

(12)本発明の半導体装置の製造方法は、(a)半導体基板の主面上にゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板の主面に不純物半導体領域を形成する工程、(b)ゲート電極および不純物半導体領域を覆う絶縁膜を堆積する工程、または、ゲート電極および不純物半導体領域の表面上に選択的に絶縁膜を形成する工程、(c)少なくともゲート電極の一部の領域上に開口を有するフォトレジスト膜を形成し、フォトレジスト膜の存在下でゲート電極上の絶縁膜の全部または一部をエッチングする工程、(d)フォトレジスト膜を除去し、半導体基板の全面に金属膜を堆積する工程、(e)半導体基板を熱処理し、ゲート電極の表面の全部または一部に金属膜を構成する金属のシリサイド膜を形成する工程、(f)未反応の金属膜を選択的に除去する工程、を含むものである。

## [0029]

(13)本発明の半導体装置の製造方法は、前記項(1)~(12)の何れか一項に記載の半導体装置の製造方法であって、金属膜がコバルト膜である。

## [0030]

(14) 本発明の半導体装置の製造方法は、前記項(1)~(9)の何れか一項に記載の半導体装置の製造方法であって、さらに、(a)選択MISFETならびに第1および第2MISFETを覆う第1層間絶縁膜を形成し、選択MISFETの一方のソース・ドレイン領域に接続する第1プラグを第1層間絶縁膜に形成する工程、(b)第1層間絶縁膜上に、第1プラグに接続するビット線を形成する工程、(c)ビット線を覆う第2層間絶縁膜を形成し、選択MISFETの他方のソース・ドレイン領域に接続する第2プラグを第1および第2層間絶縁膜に形成する工程、(d)第2層間絶縁膜上に、第2プラグに接続するメモリセルのキャパシタ下部電極を形成する工程、を有するものである。

[0031]

(15)本発明の半導体装置の製造方法は、前記項(14)記載の半導体装置の製造方法であって、(a)工程の第1プラグの形成に前後して、第1および第2MISFETのソース・ドレイン領域に接続する第3プラグを第1層間絶縁膜に形成する工程を有し、第1層間絶縁膜の表面と第1および第3プラグの表面とは、ほぼ同一平面内に形成されるものである。

[0032]

(16) 本発明の半導体装置の製造方法は、前記項(15) 記載の半導体装置の製造方法であって、第3プラグに接続される配線がビット線と同時に形成され、配線およびビット線は、他の絶縁膜を介することなく第1層間絶縁膜上に形成されるものである。

#### [0033]

(17)本発明の半導体装置の製造方法は、前記項(1)~(9)の何れか一項に記載の 半導体装置の製造方法であって、さらに、(a)多結晶シリコン膜からなるキャパシタ下 部電極を形成する工程、(b)キャパシタ下部電極上にシリコン窒化膜からなるキャパシ タ絶縁膜を形成する工程、を有するものである。

# [0034]

50

10

20

30

(18) 本発明の半導体装置の製造方法は、前記項(17) 記載の半導体装置の製造方法であって、さらに、キャパシタ絶縁膜上に窒化チタン膜からなるプレート電極を形成する 工程を有するものである。

### [0035]

(19) 本発明の半導体装置は、シリコン酸化膜からなる分離領域をその主面に有する半導体基板と、分離領域で囲まれた活性領域上にゲート絶縁膜を介して形成されたゲート電極、ゲート電極両側の活性領域に形成された一対の半導体領域を有する第1MISFETを含む半導体装置であって、第1MISFETのゲート電極の上部にはシリサイド膜が形成され、半導体領域の表面にはシリコン酸化膜が形成されているものである。

#### [0036]

(20)本発明の半導体装置は、前記項(19)記載の半導体装置であって、第1MIS FETのシリコン酸化膜は、活性領域上にのみ選択的に形成されているものである。

#### [0037]

(21)本発明の半導体装置は、前記項(19)または(20)記載の半導体装置であって、シリサイド膜はコバルトシリサイド膜である。

#### [0038]

(22)本発明の半導体装置は、前記項(19)~(21)の何れか一項に記載の半導体 装置であって、ゲート電極は2層以上の多結晶シリコン膜で構成されるものである。

#### [0039]

(23)本発明の半導体装置は、前記項(22)記載の半導体装置であって、積層された 多結晶シリコン膜間には自然酸化膜が形成されているものである。

#### [0040]

(24)本発明の半導体装置は、前記項(19)~(23)の何れか一項に記載の半導体 装置であって、第1MISFETの他に第2MISFETを同一半導体基板内に有し、第 2MISFETのゲート電極の上部および半導体領域の表面にはシリサイド膜が形成され ているものである。

## [0041]

(25)本発明の半導体装置は、前記項(24)記載の半導体装置であって、第2MIS FETはnチャネルMISFETおよびpチャネルMISFETで構成される相補型MI SFET回路を構成し、nチャネルMISFETのゲート電極はn型にドープされ、pチャネルMISFETのゲート電極はp型にドープされているものである。

# [0042]

(26)本発明の半導体装置は、前記項(25)記載の半導体装置であって、第1MIS FETはDRAMのメモリセルを構成する選択MISFETであり、第2MISFETは DRAMの周辺回路または論理回路を構成するMISFETであるものである。

#### [0043]

(27) 本発明の半導体装置は、前記項(26) 記載の半導体装置であって、第1MIS FETの一方の半導体領域とメモリセルのビット線とを接続する第1プラグが第1層間絶 縁膜に形成され、第1層間絶縁膜の表面に接してビット線が形成されているものである。

## [0044]

(28) 本発明の半導体装置は、前記項(27) 記載の半導体装置であって、ビット線上に第2層間絶縁膜が形成され、第1 および第2層間絶縁膜に、第1 M I S F E T の他方の半導体装置とメモリセルのキャパシタ株電極とを接続する第2プラグが形成されているものである。

#### [0045]

(29)本発明の半導体装置は、前記項(26)記載の半導体装置であって、メモリセルのキャパシタ絶縁膜がシリコン窒化膜からなるものである。

## [0046]

(30)本発明の半導体装置は、前記項(29)記載の半導体装置であって、メモリセルのプレート電極が窒化チタン膜からなるものである。

10

20

30

40

## [0047]

# 【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

# [0048]

(実施の形態1)

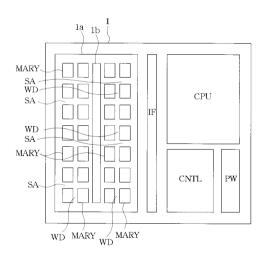

図1は、実施の形態1の半導体装置のチップ全体を示した平面図である。本実施の形態の半導体装置は、DRAMとCPU等に代表されるロジック回路とを1チップに混載したいわゆるシステムLSIである。

[0049]

半導体基板1の主面上には、たとえばメモリ素子であるDRAM、演算装置であるCPU、CPUの制御回路CNTL、インターフェース回路IF、電源回路PW等が形成されている。DRAMが形成されるDRAM領域1aには、メモリセルがアレイ状に配置されたメモリアレイMARY、センスアンプSA、ワード線ドライバWD、DRAMの制御回路、入出力回路等が含まれる。センスアンプSA、ワード線ドライバWD等は、直接周辺回路としてメモリアレイMARYの周辺に形成され、DRAMの制御回路、入出力回路等は間接周辺回路領域1bに形成される。CPU、制御回路CNTL、インターフェース回路IF、電源回路PW等は、ロジック回路の例示である。なお、本実施の形態では、ロジック回路の一例としてCPU等を例示しているが、その他の機能を有する論理回路が形成されていてもよい。また、ここに例示したロジック回路が半導体装置の機能上必要でない場合にこれを含まなくてもよいことはいうまでもない。

[0050]

なお、本明細書では、半導体基板1の領域を以下のように分けて説明する。つまり、メモリアレイMARYの形成されている領域(第1領域)とその他の領域(第2および第3領域)とに分け、説明の便宜上DRAMの周辺回路であるセンスアンプSA、ワード線ドライバWD、制御回路、入出力回路等をロジック回路に含めて考える。すなわちメモリアレイMARYの形成される第1領域以外の領域をロジック回路形成領域とし、ロジック回路形成領域には、nチャネルMISFETが形成されるnMISFET領域(第2領域)とpチャネルMISFETが形成されるpMISFET領域(第3領域)とが含まれる。

[0051]

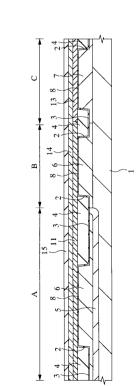

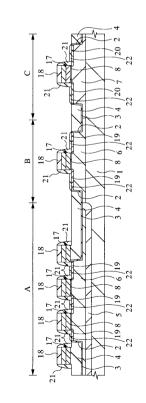

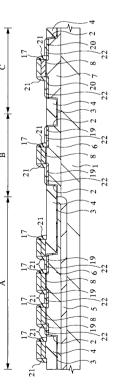

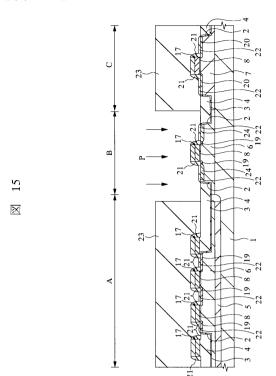

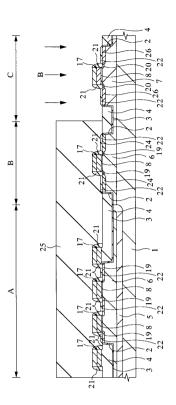

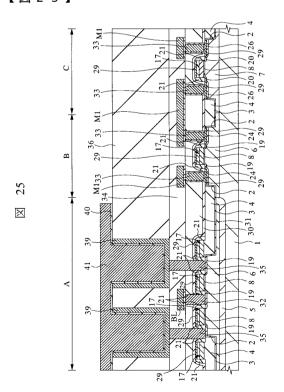

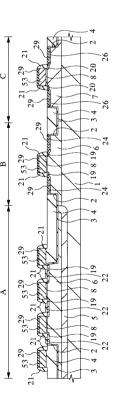

次に、本実施の形態のDRAMの製造方法を図面を用いて工程順に説明する。図2~図25および図27は、実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

[0052]

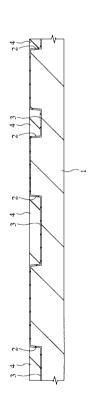

まず、図2に示すように、p型で比抵抗が10 cm程度の単結晶シリコンからなる半導体基板1を用意し、たとえば850 程度でウェット酸化して形成した膜厚10nm程度の薄いシリコン酸化膜(図示せず)およびたとえばCVD(Chemical Vapor Deposition )法で形成した膜厚140nm程度のシリコン窒化膜(図示せず)を半導体基板1上に堆積する。ここでは単結晶シリコンの半導体基板1を例示するが、表面に単結晶シリコン層を有するSOI(Silicon On Insulator)基板、あるいは、表面に多結晶シリコン膜を有するガラス、セラミックス等の誘電体基板であってもよい。

[0053]

次に、フォトレジスト膜(図示せず)をマスクにして、溝 2 が形成される領域の前記シリコン窒化膜およびシリコン酸化膜をパターニングし、このシリコン窒化膜をマスクとして半導体基板 1 をドライエッチングすることにより、素子分離領域の半導体基板 1 に深さ 3 0 0 ~ 4 0 0 nm程度の溝 2 を形成する。

[0054]

次に、前記フォトレジスト膜を除去した後、前記のエッチングによって溝 2 の内壁に生じたダメージ層を除去するために、たとえば 8 5 0 ~ 9 0 0 程度のウェット酸化による薄

10

20

30

40

い(膜厚10nm程度の)シリコン酸化膜3を溝2の内壁に形成し、たとえばオゾン( $O_3$ )とテトラエトキシシラン(TEOS)とをソースガスに用いたプラズマCVD法で堆積されたシリコン酸化膜(図示せず)を300~400nm程度の膜厚で堆積する。このシリコン酸化膜は、1000 程度でドライ酸化によりシンタリング(焼き締め)を行なってもよい。

# [0055]

次に、このシリコン酸化膜を C M P 法により研磨して溝 2 以外の領域のシリコン酸化膜を除去し、溝 2 の内部にシリコン酸化膜 4 を残して素子分離領域を形成する。なお、この C M P 法による研磨の前に、溝 2 の領域にシリコン窒化膜を形成して、溝 2 領域のシリコン酸化膜が過剰に深く研磨されるディッシングを防止することができる。

# [0056]

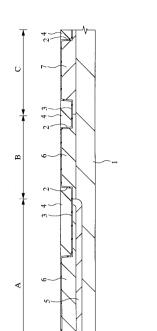

次に、図3に示すように、半導体基板1の表面に残存しているシリコン酸化膜およびシリコン窒化膜をたとえば熱リン酸を用いたウェットエッチングで除去した後、メモリセルを形成する第1領域A(メモリアレイMARY)の半導体基板1にn型不純物、たとえばP(リン)をイオン打ち込みしてn型半導体領域5を形成する。次に、第1領域Aと、ロジック回路(DRAMの周辺回路を含む)のnMISFETが形成される第2領域Bとにp型不純物、たとえばB(ホウ素)をイオン打ち込みしてp型ウエル6を形成し、ロジック回路(DRAMの周辺回路を含む)のpMISFETが形成される第3領域Cにn型不純物、たとえばP(リン)をイオン打ち込みしてn型ウエル7を形成する。n型半導体領域5は、入出力回路などから半導体基板1を通じてメモリアレイのp型ウエル6にノイズが侵入するのを防止するために形成される。

# [0057]

次に、図4に示すように、半導体基板1の表面をたとえばHF(フッ酸)系の洗浄液を使って洗浄した後、半導体基板1を850 程度でウェット酸化してp型ウエル6およびn型ウエル7の各表面に膜厚7nm程度の清浄なゲート酸化膜8を形成する。さらに、シリコン膜9を堆積する。シリコン膜9は後にゲート電極の一部となるものであり、たとえばCVD法により堆積できる。シリコン膜9は、アズデポ状態では非晶質(アモルファス)状態である。なお、特に限定はされないが、ゲート酸化膜8を形成した後、半導体基板1をNO(酸化窒素)雰囲気中またはN2O(亜酸化窒素)雰囲気中で熱処理することによって、ゲート酸化膜8と半導体基板1との界面に窒素を偏析させる酸窒化処理を施してもよい。これにより半導体基板1とゲート酸化膜8との熱膨張係数差に起因する界面の歪によるホットキャリアの発生を抑制できる。

## [0058]

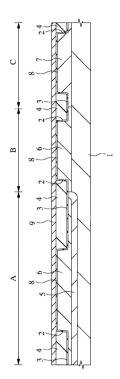

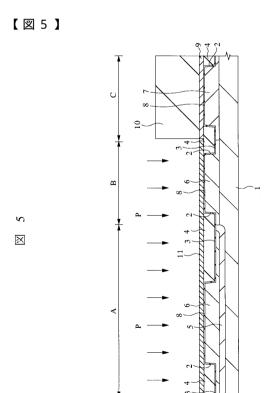

次に、図5に示すように、シリコン膜9上に、第3領域Cを覆うフォトレジスト膜10を形成し、第1領域Aおよび第2領域Bのシリコン膜9にn型不純物、たとえばリンをイオン注入する。これによりn型シリコン膜11を形成する。フォトレジスト膜10を除去した後、図6に示すように、第1領域Aおよび第2領域B覆うフォトレジスト膜12を形成し、第3領域Cのシリコン膜9にp型不純物、たとえばボロンをイオン注入する。これによりp型シリコン膜13を形成する。さらに、n型およびp型シリコン膜11、13に、たとえばRTA(Rapid Thermal Anneal)処理を施し、これを結晶化する。

# [0059]

n型シリコン膜11は、nMISFETのゲート電極の一部となるものであり、p型シリコン膜13は、pMISFETのゲート電極の一部となるものである。すなわち、本実施の形態の半導体装置はいわゆるデュアルゲート構造を有するものである。このようにデュアルゲート構造を採用することにより、表面チャネル型のMISFETでCMIS(Complementary Metal Insulator Semiconductor)構造を構成することができ、微細化に有利になる。

# [0060]

次に、図 7 に示すように、シリコン膜 1 4 をたとえば C V D 法により堆積し、全面に n 型 不純物、たとえばリンをイオン注入する。シリコン膜 1 4 は、 n 型および p 型シリコン膜 10

20

30

40

20

30

40

50

1 1、13と同様に後にゲート電極の一部となるものであり、アズデポ状態では非晶質(アモルファス)状態である。 n型不純物を全面にイオン注入するのは、後に説明するように、第1領域Aには後の工程で高濃度のn型不純物が注入されないことから、シリコン膜14がイントリンシックになることを防止する必要があるためである。なお、シリコン膜14は、アズデポ状態でn型不純物がドープされたシリコン膜として堆積されてもよい。また、イオン注入の後にシリコン膜14をRTA等によりアニール処理をし、結晶化させてもよいが必須ではない。すなわち、後の熱工程により自然に結晶化されるため、この段階で結晶化させる必要はない。

# [0061]

このようにゲート電極となる多結晶シリコン膜を2層で構成することにより、以下のような利点がある。

#### [0062]

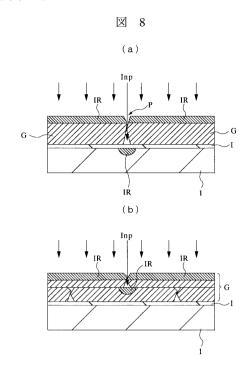

第1に、後に説明するように、ソース・ドレイン領域を構成する高濃度不純物半導体領域を形成するためのイオン注入の際に、ゲート電極(n型およびp型シリコン膜11、13とシリコン膜14)の存在下でイオン注入が行われるが、この不純物のチャネル領域への注入を防ぐことができる。つまり、仮にゲート電極が単一の多結晶シリコン膜で構成されている場合には、図8(a)に示すように、ゲート電極Gの表面から底部(ゲート絶縁膜Iの直上)まで結晶粒界のパスPが貫通する場合が生じる。このように貫通するパスPが存在する状況で不純物のイオン注入を行えば、ゲート電極Gの表面に不純物領域IRが形成される他、不純物Inpが半導体基板1に達して半導体基板1の主面にも不純物領域IRが形成される。通常ゲート電極Gの下部はMISFETのチャネル領域であるから、このような基板主面上の不純物領域IRはMISFETのしきい値電圧を変動させる等その性能を著しく阻害する。

#### [0063]

一方本実施の形態では、図8(b)に示すように、ゲート電極Gを多結晶シリコン膜の2層構成としている。このように2層構成とした場合には、上層の多結晶シリコン膜の粒界は、下層の多結晶シリコン膜に阻まれてゲート電極Gの膜厚方向に貫通することがない。つまり、シリコン膜11、13の形成後これをアニールして下層の多結晶シリコン膜を形成した後に、改めてシリコン膜14を形成するため、上層多結晶シリコン膜の粒界と下層多結晶シリコン膜の粒界とはその位置が一致する確率は極めて少ない。このため、ゲート電極Gを通して結晶粒界が貫通することはほとんどない。このような状況でイオン注入を行えば、上層多結晶シリコン膜の粒界を通して不純物Inpが下部に注入されても、貫通した不純物Inpは下層多結晶シリコン膜の表面で止まり、半導体基板1の主面に達することがない。この結果MISFETの信頼性を低下させることがない。

# [0064]

第2に、ゲート電極を多結晶シリコン膜の2層構成とすることにより、ゲート電極に蓄えられる内部応力を低減できる利点がある。すなわち、仮に単一層でゲート電極を構成した場合には、必要な膜厚を単一層で実現する必要がある。熱処理による結晶化あるいはその後の熱工程による結晶化が行われた後のゲート電極とゲート絶縁膜との界面に蓄積された熱応力は、厚い膜厚の非晶質シリコン膜から多結晶シリコン膜を形成した場合、薄い膜厚の場合と比較して大きくなる。本実施の形態では、薄い膜厚の非晶質シリコン膜から多結晶シリコン膜を形成するため、熱応力が小さく、それら薄い多結晶シリコン膜を積層していることから、各層毎に応力が緩和され、総合的な応力は低くすることができる。このため、ゲート絶縁膜の絶縁耐圧等を高め、MISFETの信頼性を高くすることができる。

#### [0065]

第3に、後に説明するように、ゲート電極の表面にはシリサイド膜が形成される。このシリサイド膜の存在下で熱工程、たとえばメモリセルを構成するキャパシタの絶縁膜の形成等が行われた場合、シリサイドを構成する金属が拡散することが考えられる。このような拡散金属がゲート絶縁膜に達した場合には、ゲート絶縁膜の耐圧を低下させ、MISFETの信頼性を低下させる恐れがある。しかし、本実施の形態では、ゲート電極を2層構成

とするため、上層多結晶シリコン膜(シリコン膜14)から下層多結晶シリコン膜(シリコン膜11、13)の界面で拡散が阻害され、金属のゲート絶縁膜への拡散を抑制できる。このような抑制は、拡散が主に結晶粒界に沿って生じることから、ゲート電極の膜厚方向での結晶粒界の貫通を阻害している結果の帰結と考えることも可能である。

# [0066]

特に、上層多結晶シリコン膜と下層多結晶シリコン膜との界面にシリコン酸化膜等が形成されている場合には、金属の拡散が有効に抑制できる。すなわち、このシリコン酸化膜に拡散金属がトラップされ、下層多結晶シリコン膜(シリコン膜11、13)に拡散し難くなるからである。このようなシリコン酸化膜は、あまりに厚すぎるとゲート電極の電気的特性を損なうため、自然酸化膜程度の膜厚のシリコン酸化膜が好ましい。このような自然酸化膜(シリコン酸化膜)は、シリコン膜11、13の形成後に、たとえば基板を大気雰囲気に暴露することにより形成することができる。その後、シリコン膜14を上記の通り形成すればよい。なお、自然酸化膜に限らず、積極的に薄いシリコン酸化膜を形成してもよいことはいうまでもない。また、大気雰囲気の暴露ではなく、反応室中での酸素等酸性ガスに暴露する方法でもかまわない。

#### [0067]

なお、上記した方法では、シリコン膜11、13をまず非晶質シリコン膜として堆積し、その後RTA等でアニール処理しているが、アズデポ状態で多結晶シリコン膜となるように被膜堆積を行ってもよい。また、アニール処理はRTAに限らずハーネス等炉内での半導体基板1の熱処理を施してもよい。

#### [0068]

次に、図9に示すように、半導体基板1の全面にシリコン窒化膜15(第1絶縁膜)を形成する。シリコン窒化膜15はCVD法またはスパッタ法により形成でき、後に説明する活性領域表面の酸化処理の際に、シリコン膜14(ゲート電極)表面の酸化を抑制する作用をする。

## [0069]

次に、図10に示すように、ゲート電極パターンにパターニングされたフォトレジスト膜16をシリコン窒化膜15上に形成し、このフォトレジスト膜16の存在下でエッチング処理を施す。すなわち、フォトレジスト膜16をマスクとしてシリコン窒化膜15、シリコン膜14およびシリコン膜11、13をエッチングする。このようにしてシリコン膜14およびシリコン膜11、13からなるゲート電極17とゲート電極17上のキャップ絶縁膜18を形成する。なお、フォトレジスト膜16をマスクとするエッチングによりシリコン窒化膜15をパターニングし、フォトレジスト膜16を除去した後に、パターニングされたシリコン窒化膜15をマスクとしてシリコン膜14およびシリコン膜11、13をエッチングしてもよい。

#### [0070]

第1領域A(メモリセル形成領域)のゲート電極17は、選択MISFETの一部を構成し、活性領域以外の領域ではワード線WLとして使用される。このゲート電極17(ワード線WL)の幅、すなわちゲート長は、選択MISFETの短チャネル効果を抑制して、しきい値電圧を一定値以上に確保できる許容範囲内の最小寸法で構成される。また、隣接するゲート電極17(ワード線WL)同士の間隔は、フォトリソグラフィの解像限界で決まる最小寸法で構成される。第2領域Bのゲート電極17は、DRAMの周辺回路を含むロジック回路のnチャネル型MISFETの一部を構成する。

# [0071]

ゲート電極 1 7 は、前記したとおり、 n 型または p 型の不純物がドープされたシリコン膜 1 1、13と、 n 型の不純物がドープされたシリコン膜 1 4 との積層膜で構成される。第 1 領域 A および第 2 領域 B においては n 型のシリコン膜 1 1 と n 型のシリコン膜 1 4 の積層膜であり、第 3 領域 C においては p 型のシリコン膜 1 3 と n 型のシリコン膜 1 4 の積層

10

20

30

40

膜である。この段階では前記の通りの積層構成であるが、後に説明するように第 2 領域 B および第 3 領域 C においてはさらに高濃度の不純物がドープされ、特に第 3 領域 C では、上層のシリコン膜 1 4 の不純物構成が n 型から p 型に転換される。

#### [0072]

なお、シリコン膜 1 1 、 1 3 とシリコン膜 1 4 の膜厚は各々 1 0 0 n m 程度とすることができる。

#### [0073]

次に、フォトレジスト膜16を除去した後、フッ酸などのエッチング液を使って、半導体 基板1の表面に残ったドライエッチング残渣やフォトレジスト残渣などを除去する。

#### [0074]

次に、図11に示すように、第1領域 A および第2領域 B に n 型不純物、たとえば P (リン)をイオン打ち込みしてゲート電極17の両側の p 型ウエル 6 に n 型半導体領域19を形成する。さらに、第3領域 C に p 型不純物、たとえば B (ホウ素)をイオン打ち込みしてゲート電極17の両側の n 型ウエル7に p 型半導体領域20を形成する。

#### [0075]

次に、図12に示すように、半導体基板1上にCVD法で膜厚50~100nm程度のシリコン酸化膜(図示せず)を堆積した後、このシリコン酸化膜を異方性エッチングすることにより、ゲート電極17およびキャップ絶縁膜18の側壁にサイドウォール21を形成する。

# [0076]

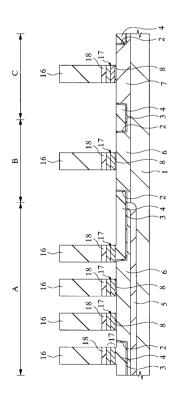

次に、図13に示すように、半導体基板1の表面を酸化処理する。この酸化処理では、表面に露出されたシリコン部分が選択的に酸化されてシリコン酸化膜22が形成される。つまり、ゲート電極17の上面にはキャップ絶縁膜18が、側面にはサイドウォール21が形成されているため、ゲート電極17の上面および側面は酸化されず、また、活性領域以外には分離領域であるシリコン酸化膜4が形成されているため、ゲート電極17およびサイドウォール21をその表面に有しない活性領域、つまりn 型半導体領域19および中型半導体領域20の表面が酸化される。このようなシリコン酸化膜22は、次に説明するキャップ絶縁膜18の除去の際のブロッキング膜として、また、後に説明するサイリサイドプロセスの際の所定領域のブロッキング膜として機能する。なお、シリコン酸化膜2の膜厚は、後の洗浄工程での削れ量を考慮し、後に説明するシリサイド用の金属膜のとの反応をブロッキングするに十分な膜厚で、できるだけ薄く形成することが好ましい。

# [0077]

次に、図14に示すように、キャップ絶縁膜18を除去する。キャップ絶縁膜18はシリコン窒化膜からなり、またそれ以外の領域は、シリコン酸化膜22で覆われているか、もしくは分離領域であるシリコン酸化膜4であるため、シリコン酸化膜に対してシリコン窒化膜が選択的にエッチングされる条件でエッチングを行うことにより、キャップ絶縁膜18のみを選択的に除去できる。エッチングは、たとえば熱リン酸によるウェットエッチングを施すことができる。また、シリコン窒化膜のエッチング速度がシリコン酸化膜のエッチング速度よりも高い条件でのドライエッチングを施すこともできる。

## [0078]

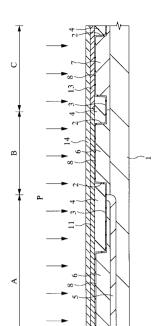

次に、図15に示すように、第1領域 A および第3領域 C を覆うフォトレジスト膜 2 3を形成し、このフォトレジスト膜 2 3をマスクとして第2領域 B に n 型不純物、たとえば P (リン)または A s (ヒ素)を高濃度にイオン注入する。これにより高濃度の n  $^+$  型半導体領域 2 4 を形成する。 n  $^+$  型半導体領域 2 4 と n  $^-$  型半導体領域 1 9 とは n チャネル型 M I S F E T のソース・ドレイン領域として機能し、いわゆる L D D (Light Iy Doped Dr ain )を構成する。このとき、同時にゲート電極 1 7 の上層  $^-$  お記録 B におけるゲート電極 1 7 は、 n 型  $^-$  数結晶のシリコン膜 1 1 (下層)と高濃度 n 型  $^-$  数結晶のシリコン膜 1 4 との積層構成となる。

# [0079]

10

20

30

次に、図16に示すように、第1領域 A および第2領域 B を覆うフォトレジスト膜25を 形成し、このフォトレジスト膜25をマスクとして第3領域 C に p 型不純物、たとえば B (ボロン)またはを高濃度にイオン注入する。これにより高濃度の p \* 型半導体領域26 を形成する。 p \* 型半導体領域26と p \* 型半導体領域20とは p チャネル型 M I S F E Tのソース・ドレイン領域として機能し、いわゆるLDDを構成する。このとき、同時に ゲート電極17の上層多結晶シリコン膜(シリコン膜14)に p 型不純物が高濃度にドー プされ、第3領域 C におけるゲート電極17の上層多結晶シリコン膜は、 n 型から p 型に 転換される。従って第3領域 C におけるゲート電極17は、 p 型多結晶のシリコン膜13 (下層)と高濃度 p 型多結晶のシリコン膜14との積層構成となる。

#### [0800]

なお、 n \* 型半導体領域 2 4 と p \* 型半導体領域 2 6 とを形成するためのイオン注入は、シリコン酸化膜 2 2 の存在下で行われる。このため、イオン注入によるノックオンにより、 n \* 型半導体領域 2 4 と p \* 型半導体領域 2 6 に若干の酸素原子が導入される。この酸素原子は、後に説明するシリサイド膜が n \* 型半導体領域 2 4 と p \* 型半導体領域 2 6 に若干の酸素原子が導入される。この酸素原子は、後に説明するシリサイド膜を構成する金属がコバルト(Co)の場合には自動く。すなわち、 n \* 型半導体領域 2 4 および p \* 型半導体領域 2 6 中の酸素は、各のしまるが形成されたときに同時にシリサイド膜内に取り込まれるが、この酸素原子はシリサイド膜内の物質移動を阻害する要因として働く。このため、チタンリサイドのように結晶相によって抵抗率が異なり、低抵抗化のために熱処理等を施してサイドの場合には結晶相変化させなくても低抵抗であることから相変化する必要がある場合には酸素原子の存在は相変化を阻害し不利に働くが、コバルトシリサイドの物質移動を阻害することがその後の熱処理によるシリサイドの場合には結晶相変化させなくても低抵抗であることから相変化する必要がけて、むしろコバルトシリサイドの物質移動を阻害することがその後の熱処理によるシリナイド膜の深化を抑制でき、n \* 型半導体領域 2 4 および p \* 型半導体領域 2 6 (ソース・ドレイン領域)の導電率の確保の点からむしろ好ましい。

#### [0081]

また、上記イオン注入の際に、ゲート電極17が2層の多結晶シリコン膜で構成されているため、注入イオンがゲート電極17下のチャネル領域に達しないことは前記した通りである。

# [0082]

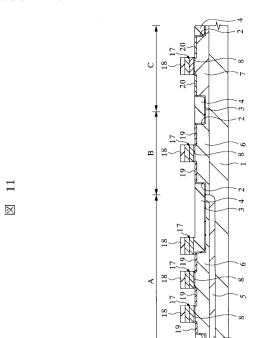

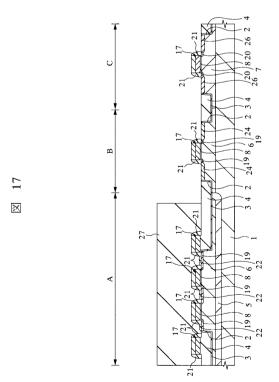

次に、図17に示すように、第1領域 A を覆うフォトレジスト膜 2 7を形成し、第2領域 B と第3領域 C のシリコン酸化膜 2 2を除去する。このように第1領域 A のシリコン酸化膜 2 2を残存させるのは、次に説明するサリサイド工程において第1領域 A の n ・型半導体領域 1 9表面をシリサイド化させないためである。

## [0083]

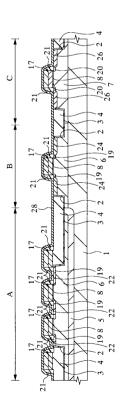

次に、たとえばフッ酸(HF)系水溶液による前洗浄を行った後に、図18に示すように、金属膜28を半導体基板1の全面にたとえばスパッタ法またはCVD法により堆積する。金属膜28は、たとえばコバルト(Co)膜とし、膜厚は約10nmとする。

## [0084]

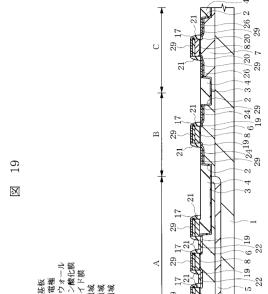

次に、図19に示すように、金属膜28とシリコンとのシリサイド化反応を生じさせるためのアニール処理を行い、金属シリサイド膜29(コバルトシリサイド膜)を形成する。その後未反応の金属膜28を選択的に除去する。未反応金属膜の選択的な除去は、たとえば塩酸(HC1)および過酸化水素水(H $_2$  O $_2$  )の混合液を用いたエッチングにより行うことができる。

# [0085]

シリサイド化反応は、金属膜28とシリコンが接触している部分で生じることから、シリコン酸化膜で覆われていない部分、つまりゲート電極17の上面、第2領域Bおよび第3領域Cのn<sup>+</sup>型半導体領域24およびp<sup>+</sup>型半導体領域26の上面で発生する。従ってシリコン酸化膜22で覆われている第1領域A(メモリセル形成領域)のn<sup>-</sup>型半導体領域19上にはシリサイド膜は形成されない。

# [0086]

10

20

20

20

30

40

50

このように、第1領域 A (メモリセル形成領域)の n ・型半導体領域 1 9 上にシリサイド膜が形成されないことにより、メモリセル選択用の選択 M I S F E T のリーク電流を低減できる。これによりメモリセルのリフレッシュ特性を良好に維持できる。また、第2領域 B および第3領域 C におけるゲート電極 1 7 表面とソース・ドレイン領域表面の両方を同時にシリサイド化するいわゆるサイリサイド技術を適用できるため工程を簡略化できるとともに、第1領域 A 、第2領域 B 、第3領域 C の全ての領域においてゲート電極 1 7 の表面をシリサイド化することができ、簡易な工程でゲート電極 1 7 を低抵抗化でき、半導体装置の性能を高く維持することができる。

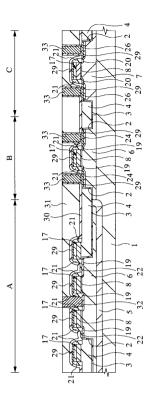

# [0087]

次に、図20に示すように、自己整合用のシリコン窒化膜30および層間絶縁膜31を形成し、さらに第1領域Aに多結晶シリコン膜からなるプラグ32を、第2領域Bおよび第3領域Cに金属膜からなるプラグ33を形成する。

#### [0088]

シリコン窒化膜30は、たとえばCVD法により堆積できる。層間絶縁膜31の形成は、半導体基板1上に膜厚300m程度のSOG(SpinOnGlass)膜をスピン塗布した後、半導体基板1を熱処理してこれをシンタリング(焼き締め)し、SOG膜の上部に膜厚600m程度のシリコン酸化膜を堆積した後、このシリコン酸化膜をCMP法で研磨してその表面を平坦化することにより形成できる。さらに、CMP法で研磨されたときに生じた表面の微細な傷を補修するため、このシリコン酸化膜の上部に膜厚100m程度のシリコン酸化膜を堆積してもよい。シリコン酸化膜は、たとえばオゾン(O3)とテトラエトキシシラン(TEOS)とをソースガスに用いたプラズマCVD法で堆積する。

#### [0089]

プラグ32の形成は、プラグ32が形成される領域に開口を有するフォトレジスト膜をマスクとして、層間絶縁膜31に接続孔を形成し、その後、この接続孔を埋め込むn型不純物(たとえばP(リン))がドープされた多結晶シリコン膜をたとえばCVD法により堆積し、接続孔以外の領域の多結晶シリコン膜を除去して形成できる。多結晶シリコン膜の除去にはCMP法、またはエッチバック法を用いることができる。なお、接続孔の開口には、シリコン窒化膜30を用いた2段階エッチング法を用いることができる。つまり、層間絶縁膜31であるシリコン酸化膜がエッチングされやすい条件で行う第1段階のエッチングの後に、シリコン窒化膜がエッチングされやすい第2段階のエッチングを適用できる。このようにエッチングを2段階で行うことにより、半導体基板1の表面(特に分離領域であるシリコン酸化膜4)の過剰なエッチングが抑制できる。

## [0090]

なお、この段階では、後に説明するビット線に接続するプラグ32を形成し、キャパシタに接続するためのプラグの形成は行わない。このように、キャパシタに接続するプラグを後に形成することにより、層間絶縁膜を1層省略することができる。これは、工程を簡略化するのみならず、メモリセル領域の標高が省略する絶縁膜の膜厚分だけ低く形成できることとなる。つまり、仮にこの段階でビット線に接続するプラグ32とともにキャパシタに接続するプラグをも形成すると、両プラグの電気的絶縁性を実現するために絶縁膜を形成し、その絶縁膜上にビット線接続孔を介してプラグ32に接続されるビット線を形成することが必要になる。すなわちプラグ32とキャパシタに接続するプラグとを絶縁する絶縁膜が不可欠となる。ところが、本実施の形態では、このような絶縁膜は必要でなく、工程簡略化および素子の低層化を実現できる。

# [0091]

プラグ33の形成は、プラグ33が形成される領域に開口を有するフォトレジスト膜をマスクとして、層間絶縁膜31に接続孔を形成し、その後、この接続孔を埋め込む窒化チタン膜およびタングステン膜をたとえばスパッタ法あるいはCVD法により堆積し、接続孔以外の領域の窒化チタン膜およびタングステン膜を除去して形成できる。窒化チタン膜は半導体基板1(シリサイド膜29)とタングステン膜との反応を抑制するバリア層として機能する。窒化チタン膜およびタングステン膜の除去にはCMP法を用いることができる

。なお、接続孔の開口には、プラグ32の場合と同様に2段階エッチング法を用いることができる。

# [0092]

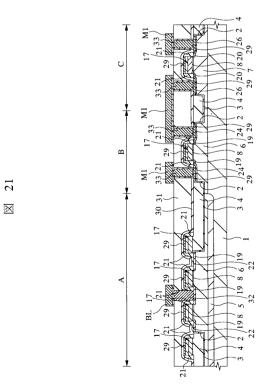

次に、図21に示すように、第1領域Aにビット線BLを、第2領域Bおよび第3領域Cに第1層配線M1を形成する。ビット線BLおよび第1層配線M1は同一の工程で形成される。ビット線BLおよび第1層配線M1は、まずシリコン酸化膜31の上部に膜厚50nm程度の窒化チタン膜をたとえばスパッタリング法で堆積し、さらにその上部に膜厚150nm程度のタングステン膜をたとえばCVD法で堆積した後、フォトレジスト膜をマスクにしてこれらの膜をパターニングすることにより形成する。窒化チタン膜は、タングステン膜と多結晶シリコンからなるプラグ32との間の反応を抑制するために形成する。ビット線BLは、隣接するビット線BLとの間に形成される寄生容量をできるだけ低減して情報の読み出し速度および書き込み速度を向上させるために、その間隔がその幅よりも長くなるように形成する。ビット線BLの間隔はたとえば0.24μm程度とする。

## [0093]

次に、図22に示すように、層間絶縁膜34を形成し、さらに、選択MISFETとキャパシタとを接続するプラグ35を形成する。

#### [0094]

層間絶縁膜34の一部には、膜厚300m程度のSOG膜を用いることができる。SOG膜は、BPSG膜に比べてリフロー性が高く、微細な配線間のギャップフィル性に優れているので、微細化されたビット線BL同士の隙間を良好に埋め込むことができる。また、SOG膜上にたとえばオゾン(O₃)とテトラエトキシシラン(TEOS)とをソースガスに用いたプラズマCVD法で堆積したシリコン酸化膜を形成し、これをCMP法により平坦化して層間絶縁膜34とすることができる。これにより、ビット線BL同士の微細な隙間のギャップフィル性が向上すると共に、ビット線BLおよび第1層配線M1上の絶縁膜の平坦化を実現できる。なお、CMP法で研磨されたときに生じた前記シリコン酸化膜の表面の微細な傷を補修するためにさらにシリコン酸化膜を形成してもよい。

#### [0095]

プラグ35は、プラグ32と同様に形成できる。なお、プラグ32が形成される接続孔は、層間絶縁膜34、31に開口されるが、前記したとおり、ビット線BLとプラグ32との間に絶縁膜が形成されていないため、この接続孔の深さを低減でき、工程の難易度を下げることができる。

# [0096]

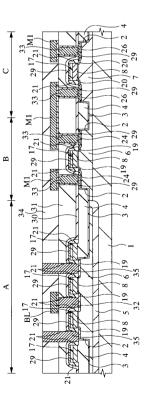

次に、図23に示すように、絶縁膜36を堆積し、プラグ35に達する溝37を絶縁膜36に形成する。その後、溝37の内壁を覆う多結晶シリコン膜38を半導体基板1の全面に堆積する。

# [0097]

絶縁膜36は、たとえばシリコン酸化膜とし、キャパシタの容量を考慮してその膜厚を約1μmとする。シリコン酸化膜はたとえば C V D 法により形成できる。溝37は、フォトレジスト膜をマスクとしてエッチングにより形成し、多結晶シリコン膜38は、たとえば C V D 法により形成する。多結晶シリコン膜38の膜厚は約70 n m とする。

#### [0098]

なお、絶縁膜36の堆積前に薄いシリコン窒化膜を堆積してもよい。このシリコン窒化膜により溝37の形成を2段階のエッチングを用いて行うことができ、過剰にエッチングすることなくプラグ35表面の露出を均一性よく行うことができる。

# [0099]

次に、レジスト膜(図示せず)等で溝37内を充填し、溝37の内部以外の絶縁膜36上の多結晶シリコン膜38をたとえばエッチバック法で除去する。これにより溝37内に多結晶シリコン膜38からなるキャパシタの下部電極39を形成する。その後、溝37内を充填したレジスト膜等を除去する。なお、下部電極39の内面に、容量増加のための表面

10

20

30

40

粗化処理を施してもよい。表面粗化は、粒状シリコン結晶の成長により行うことができる

## [0100]

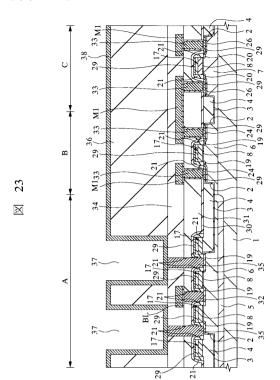

次に、たとえばホスフィン(PH3)ガスを用いたリン処理を行う、これにより下部電極39にリンをドープする。また、不純物(リン)の活性化を750 4分の熱処理により行う。その後シリコン窒化膜40を堆積する(図24)。シリコン窒化膜40はキャパシタ絶縁膜として機能し、たとえばランプ加熱式の枚葉処理装置によるCVD法(たとえば730 、10分の処理条件)により形成できる。シリコン窒化膜40の膜厚は約9nmとする。

# [0101]

なお、キャパシタ絶縁膜としては結晶化酸化タンタル膜( $Ta_2O_5$ )等の高誘電率金属酸化膜を用いることもできるが、本実施の形態ではシリコン窒化膜 40 が適当である。すなわち、シリコン窒化膜の形成温度は、730 程度であり、800 以上の処理温度を必要とする結晶化酸化タンタル膜よりも低温で形成できる。このような低温化は、本実施の形態のようにロジック回路を混載した半導体装置に好ましい。つまり、ロジック回路の場合、本実施の形態で既に説明したように、サリサイドプロセスを用いてゲート電極おびソース・ドレイン領域にシリサイド層(シリサイド膜 29)が形成される。このシリサイド膜 29)が存在する状況で 800 以上の熱工程に曝すと、シリサイド中のコバルトの拡散あるいは深い領域へのシリサイドの成長が問題となる場合がある。これはシリサイド膜 29 の耐熱性の低さとして観測され、ロジック部のMISFETの信頼性、性能の低下の原因となる。ところが、本実施の形態のようにキャパシタ絶縁膜として低温化形成が可能なシリコン窒化膜 40 を用いれば、シリサイド膜 29 の耐熱性が問題となることが少ない。

#### [0102]

また、本実施の形態のようにデュアルゲート構造の場合にも、キャパシタ絶縁膜としてシリコン窒化膜40を用いる効果が大きい。すなわち、デュアルゲート構造の場合にはゲート電極17としてボロン等p型不純物がドープされた多結晶シリコン膜を用いるが、高温プロセスが介在した場合にはこのボロンの拡散が問題となる場合がある。すなわち、ボロンのゲート絶縁膜あるいはチャネル領域への拡散によりMISFETのしきい値電圧がシフトする原因となる。ところが、本実施の形態では低温化が可能なシリコン窒化膜40を用いるため、ボロンの拡散を抑制でき、前記のような問題の発生を少なくすることができる。

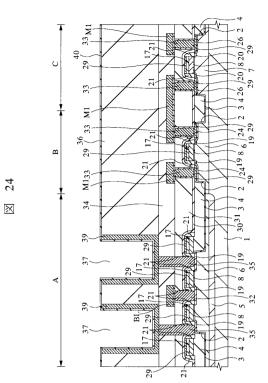

## [0103]

次に、図25に示すように、溝37を埋め込む窒化チタン膜をシリコン窒化膜40上に堆積する。窒化チタン膜は、たとえばCVD法およびスパッタ法により堆積する。すなわち、CVD法により約500 の成膜条件で窒化チタン膜を膜厚約30nmで堆積し、その後スパッタ法により窒化チタン膜を約80nmの膜厚で堆積する。このように、窒化チタン膜は500 以下の低温で形成できるため、前記したような高温プロセスの問題が発生しない。その後、主に第1領域Aを覆うフォトレジスト膜をマスクとして窒化チタン膜およびシリコン窒化膜40をエッチングし、プレート電極41(キャパシタ上部電極)を形成する。

#### [0104]

なお、プレート電極 4 1 は、窒化チタン膜に代えて多結晶シリコン膜を用いることが可能であるが、本実施の形態では、窒化チタン膜の方が好ましい。すなわち、多結晶シリコン膜をプレート電極に用いる場合は、不純物の活性化処理が必要となり、活性化処理は一般に 7 5 0 程度の熱工程となる。このような熱工程が本実施の形態のようにロジック回路を混載する場合に好ましくないことは前記の通りである。

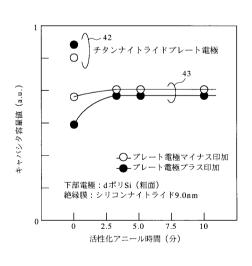

## [0105]

また、図26に示すように、プレート電極41として窒化チタン膜を用いた場合と多結晶シリコン膜を用いた場合とでは、キャパシタの容量値が異なることを本発明者らは見いだ

10

20

30

40

している。図26は、本発明者らの実験検討によるデータを示したグラフであり、プレート電極として窒化チタン膜と多結晶シリコン膜を用いた場合を比較したデータである。図中のデータ群42はプレート電極として窒化チタン膜を用いた場合のデータであり、データ群43はプレート電極として多結晶シリコン膜を用いた場合のデータである。白丸はプレート電極に負電圧を印加した場合の容量値、黒丸はプレート電極に正電圧を印加した場合の容量値である。データ群43(多結晶シリコン膜プレート)の場合は活性化アニール処理の時間についてプロットしている。多結晶シリコン膜プレートの場合は活性化アニール時間が増加するに従い容量値が大きくなっていることがわかる。一方、窒化チタン膜プレートの場合は、活性化アニール処理が必要でないばかりか、多結晶シリコン膜プレートに比較して容量値が大きくなる。

10

20

## [0106]

このような知見に基づき、容量絶縁膜としてシリコン窒化膜を用いる場合には、プレート 電極 4 1 として窒化チタン膜を用いることが有効であることがわかる。

# [ 0 1 0 7 ]

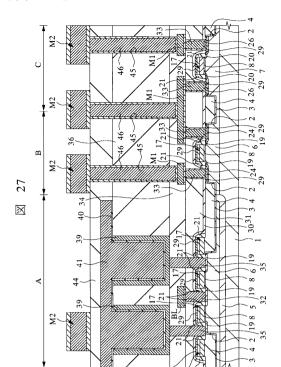

次に、図27に示すように、キャパシタの上部に膜厚40nm程度のシリコン酸化膜44を堆積する。シリコン酸化膜44は、たとえばオゾン(〇3)とテトラエトキシシラン(TEOS)とをソースガスに用いたプラズマCVD法で堆積する。その後、フォトレジスト膜をマスクにしたドライエッチングで第1層配線M1の上部の絶縁膜を除去することにより、スルーホール45を形成する。その後、スルーホール45の内部にプラグ46を形成し、続いてシリコン酸化膜44の上部に第2層配線M2を形成する。プラグ46は、シリコン酸化膜44の上部にスパッタリング法で膜厚100nm程度のTiN膜を堆積し、さらりしてスルーホール45の内部に残すことにより形成する。第2層配線M2は、シリコン酸化膜44の上部にスパッタリング法で膜厚50nm程度のTiN膜、膜厚500m程度のTiN膜、膜厚500m程度のTiN膜、膜厚500m程度のTi尺にしたドライエッチングでこれらの膜をパターニングして形成する。

[0108]

その後、層間絶縁膜を介して第3層配線等の上層配線を形成し、その上部にシリコン酸化膜とシリコン窒化膜とで構成されたパッシベーション膜を堆積するが、その図示は省略する。以上の工程により、本実施の形態の半導体装置が略完成する。

30

# [0109]

なお、第3層配線およびそれに接続するプラグは第2層配線の場合と同様に形成することができ、層間絶縁膜は、たとえば膜厚300nm程度のシリコン酸化膜、膜厚400nm程度のSOG膜および膜厚300nm程度のシリコン酸化膜で構成できる。シリコン酸化膜は、たとえばオゾン(〇 $_3$ )とテトラエトキシシラン(TEOS)とをソースガスに用いたプラズマCVD法で堆積できる。

[0110]

本実施の形態によれば、最小限の工程追加(シリコン酸化膜22の形成)により、第1領域A(メモリセル形成領域)のソース・ドレイン領域にはシリサイド膜を形成することなく、サリサイドプロセスを適用してDRAM周辺回路を含むロジック領域(第2領域Bおよび第3領域C)のソース・ドレイン領域とゲート電極の低抵抗化を実現できる。これによりMISFETの性能を損なうことなくDRAM領域とロジック領域のプロセスを共通化して工程を簡略化することができる。

40

# [0111]

また、ゲート電極17を2層構成とすることにより、イオン注入工程におけるチャネル領域へのイオンの注入を防止し、また、キャパシタ形成工程等の熱工程におけるシリサイド金属のゲート絶縁膜への拡散を防止できる。さらに、ゲート電極の内部応力を抑制してゲート絶縁膜の耐圧を向上できる。

# [0112]

また、DRAMキャパシタの絶縁膜としてシリコン窒化膜を用いることにより、キャパシ

タ絶縁膜の形成工程を低温化し、シリサイド膜の熱劣化を防止し、また、デュアルゲートを構成するp型ゲート電極のボロンの拡散を抑制できる。さらに、シリコン窒化膜からなるキャパシタ絶縁膜と窒化チタン膜からなるプレート電極との組み合わせによりキャパシタの蓄積容量値を増加できる。

# [0113]

また、ビット線 B L に接続するプラグ 3 2 の形成とキャパシタに接続するプラグ 3 5 の形成を別工程とするため、ビット線 B L とプラグ 3 2 との間に絶縁膜を形成する必要がなく、工程を簡略化できるとともにこの絶縁膜の膜厚分だけ素子の標高を低くすることができる。

# [0114]

10

20

30

(実施の形態2)

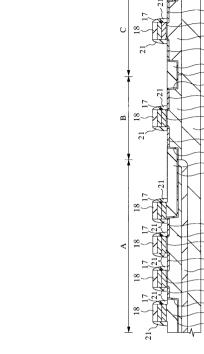

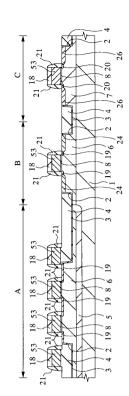

図 2 8 ~ 図 3 4 は、実施の形態 2 の半導体装置の製造工程の一例を工程順に示した断面図である。

# [0115]

本実施の形態の半導体装置の製造方法は、実施の形態 1 における図 4 までの工程と同様である。ただし、本実施の形態では、ゲート電極が単一のシリコン層で構成されるため、実施の形態 1 のシリコン膜 9 よりも膜厚の厚いシリコン膜 5 0 が形成される。

# [0116]

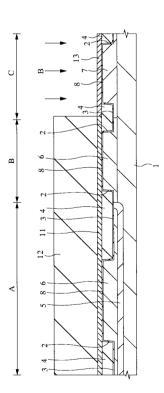

その後、実施の形態1と同様に、図28に示すように、シリコン膜50上に、第3領域Cを覆うフォトレジスト膜10を形成し、第1領域Aおよび第2領域Bのシリコン膜50にn型不純物、たとえばリンをイオン注入する。これによりn型シリコン膜51を形成する。フォトレジスト膜10を除去した後、図29に示すように、第1領域Aおよび第2領域B覆うフォトレジスト膜12を形成し、第3領域Cのシリコン膜50にp型不純物、たとえばボロンをイオン注入する。これによりp型シリコン膜52を形成する。さらに、n型およびp型シリコン膜51、52に、たとえばRTA(Rapid Thermal Anneal)処理を施し、これを結晶化する。

## [0117]

次に、実施の形態1の図9のシリコン窒化膜15と同様にシリコン窒化膜を形成し、実施の形態1の図10の工程と同様にこのシリコン窒化膜およびシリコン膜51、52をパターニングしてゲート電極53およびキャップ絶縁膜18を形成する。さらに、実施の形態1の図11の工程と同様にn・型半導体領域19およびp・型半導体領域20を形成する。続いて、実施の形態1の図12の工程と同様にゲート電極53およびキャップ絶縁膜18の側壁にサイドウォール21を形成する(図30)。

# [0118]

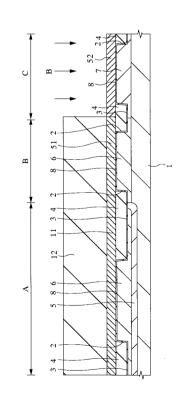

次に、実施の形態1の図13の工程と同様に、半導体基板1の表面を酸化処理してシリコン酸化膜22を形成する(図31)。

# [0119]

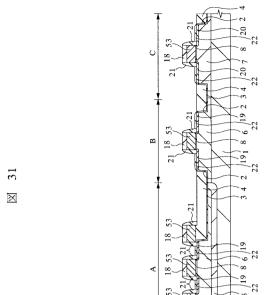

次に、実施の形態 1 の図 1 5 および図 1 6 の工程と同様に、  $n^+$  型半導体領域 2 4 および  $p^+$  型半導体領域 2 6 をイオン注入により形成する(図 3 2)。このイオン注入の際には、ゲート電極 5 3 上にはキャップ絶縁膜 1 8 が形成されているため、注入イオンのチャネル領域(半導体基板 1)への貫通は生じない。

40

#### [0120]

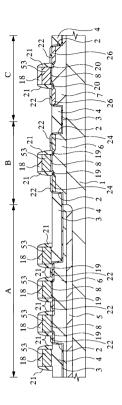

次に、実施の形態1の図14の工程と同様に、キャップ絶縁膜18を除去する(図33)

## [0121]

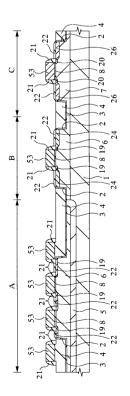

次に、実施の形態1の図17の工程と同様に、第2領域Bと第3領域Cのシリコン酸化膜22を除去し、さらに実施の形態1の図18と同様に、金属膜を半導体基板1の全面にたとえばスパッタ法またはCVD法により堆積する。その後、実施の形態1の図19と同様に、金属膜とシリコンとのシリサイド化反応を生じさせるためのアニール処理を行い、金属シリサイド膜29(コバルトシリサイド膜)を形成する。その後未反応の金属膜を選択

的に除去する(図34)。

# [0122]

その後の工程は実施の形態1と同様である。

#### [0123]

本実施の形態によれば、ゲート電極 5 3 を単層構成にして、工程を簡略化することができる。

#### [0124]

なお、本実施の形態では、シリコン酸化膜22の形成後にn\*型半導体領域24およびp\*型半導体領域26を形成した(図32参照)が、図35に示すように、シリコン酸化膜22の形成前にn\*型半導体領域24およびp\*型半導体領域26を形成してもよい。そしてn\*型半導体領域24およびp\*型半導体領域26の形成後にシリコン酸化膜22を形成し、さらに図33以降の工程を行うことができる。この場合には、シリコン酸化膜22が無い状態で高濃度の不純物イオン注入が行われるため、n\*型半導体領域24およびp\*型半導体領域26内に酸素イオンがノックオンされることがない。従って、シリサイド金属としてチタン等を用い、チタンシリサイド膜等の低抵抗化(相変化)が必要なシリサイド膜を形成する場合に有利である。

## [0125]

(実施の形態3)

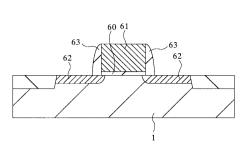

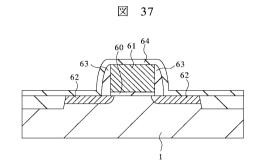

図36~図41は、実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

[0126]

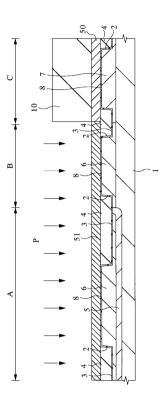

図36に示すように、半導体基板1の主面にゲート絶縁膜60を介したゲート電極61、 ソース・ドレイン領域である半導体領域62、サイドウォール63を有するMISFET を形成する。ゲート電極61は多結晶シリコン膜からなりその表面に絶縁膜等は形成され ていない。

# [0127]

次に、図37に示すように、絶縁膜64たとえばシリコン酸化膜を形成する。絶縁膜64 は、たとえばCVD法による膜堆積で形成することができるが、熱酸化法によりゲート電極61表面および半導体領域62表面にのみ形成してもよい。

[0128]

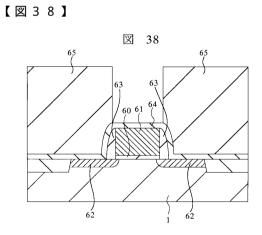

次に、図38に示すように、ゲート電極61の上部に開口を有するフォトレジスト膜65を形成する。フォトレジスト膜65は、ゲート電極61のパターンを若干広げたパターンの反転パターンで形成できる。

[0129]

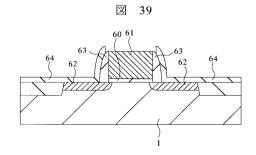

次に、図39に示すように、フォトレジスト膜65をマスクとして絶縁膜64をエッチングし、ゲート電極61の表面を露出する。そしてフォトレジスト膜65を除去する。

[0130]

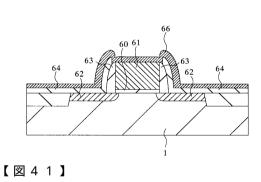

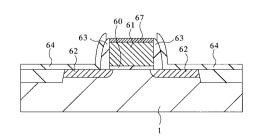

次に、図40に示すように、金属膜66、たとえばコバルト膜を堆積し、熱処理を行って、金属膜66とゲート電極61(多結晶シリコン膜)との反応によりシリサイド膜67(たとえばコバルトシリサイド膜)を形成する。その後図41に示すように、未反応の金属膜66を除去する。

[0131]

本実施の形態では、絶縁膜64により半導体領域62が覆われているため、半導体領域62上にはシリサイド膜が形成されず、一方、ゲート電極61上の絶縁膜64はエッチングにより除去されているため、ゲート電極61上にシリサイド膜67が形成され低抵抗化が図られる。

#### [0132]

このように、本実施の形態の方法を用いてもサリサイド技術を用いてゲート電極 6 1 上にのみシリサイド膜 6 7 を形成することができる。

[0133]

10

20

30

40

なお、微細化されたゲート電極61においてはフォトレジスト膜65のパターニングが困 難になることが考えられるが、本実施の形態では、パターニングがゲート電極61の配線 幅方向(図ではゲート長方向)に半分程度ずれても構わない。このようなずれの発生によ り、ゲート電極61のシリサイド化される領域が狭くなるが、ゲート電極61表面の半分 程度にシリサイド膜67が形成されておればゲート電極61の低抵抗化を図ることに支障 は生じない。これにより、ゲート電極61の低抵抗化を維持しつつフォトレジスト膜65 のパターニング精度を低下することができ、工程の難易度を下げてプロセスマージンを広 げることができる。

# [0134]

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、 本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変 更可能であることは言うまでもない。

#### [0135]

たとえば、実施の形態1、2では、シリコン酸化膜22を形成してMISFETのソース ・ドレイン領域にシリサイド膜を形成しない例としてDRAMメモリセルの選択MISF ETを例示しているが、これに限られず、一般的なMISFET、あるいはロジック回路 内に形成され、特にリーク電流の低減を図る必要のあるMISFETに適用できることは 言うまでもない。

## [0136]

# 【発明の効果】

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明す れば以下のとおりである。

## [0137]

(1)ロジック回路あるいはDRAMの周辺回路のMISFETの高い性能を維持しつつ DRAMメモリセルのMISFETのリーク電流を低減し、良好なDRAMのリフレッ シュ特性を実現できる。

## [0138]

(2)ロジック回路あるいはDRAMの周辺回路のMISFETとメモリセルの選択MI SFETとに要求される相反する要求を低コストで実現できる。

# [0139]

(3)ロジック回路あるいはDRAMの周辺回路のMISFETとメモリセルの選択MI SFETが1チップに混載されている場合にも良好な信頼性を実現できる。

#### 【図面の簡単な説明】

- 【図1】実施の形態1の半導体装置のチップ全体を示した平面図である。

- 【図2】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図3】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図4】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図5】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図6】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。 【図7】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図8】(a)は比較のために示した半導体装置の一部拡大断面図であり、(b)は実施 の形態1の半導体装置の製造工程の一例を工程順に示した一部拡大断面図である。

- 【図9】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図10】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図11】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図12】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図13】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図14】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図15】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

- 【図16】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

20

10

30

40

```

【図17】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図18】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図19】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図20】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図21】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図22】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図23】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図24】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図25】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

10

【図26】本発明者らの実験検討によるデータを示したグラフであり、プレート電極とし

て窒化チタン膜と多結晶シリコン膜を用いた場合を比較したデータである。

【図27】実施の形態1の半導体装置の製造工程の一例を工程順に示した断面図である。

【図28】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図29】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図30】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図31】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図32】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図33】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

【図34】実施の形態2の半導体装置の製造工程の一例を工程順に示した断面図である。

20

【図35】実施の形態2の半導体装置の製造工程の他の例を工程順に示した断面図である

【図36】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【図37】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【図38】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【図39】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【図40】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【図41】実施の形態3の半導体装置の製造工程の一例を工程順に示した断面図である。

【符号の説明】

1 半導体基板

30

1 a DRAM領域

1 b 間接周辺回路領域

2

溝

3

シリコン酸化膜

4

シリコン酸化膜

5

n型半導体領域

6

p型ウエル

7

n型ウエル

ゲート酸化膜

9

シリコン膜

40

10 フォトレジスト膜

シリコン膜(n型シリコン膜)

1 1

1 2

フォトレジスト膜

1 3

シリコン膜(p型シリコン膜)

1 4

シリコン膜

1 5

シリコン窒化膜

1 6

フォトレジスト膜

1 7

ゲート電極

1 8

キャップ絶縁膜

n <sup>-</sup> 型半導体領域

19

p · 型半導体領域

50

```

20

30

40

50

2.1 サイドウォール 22 シリコン酸化膜 2 3 フォトレジスト膜 2 4 n <sup>+</sup> 型半導体領域 2 5 フォトレジスト膜 2 6 p + 型半導体領域 2 7 フォトレジスト膜 2 8 金属膜 2 9 シリサイド膜 30 シリコン窒化膜 3 1 層間絶縁膜(シリコン酸化膜) 3 2 プラグ 3 3 プラグ 3 4 層間絶縁膜 3 5 プラグ 3 6 絶縁膜 3 7 溝 3 8 多結晶シリコン膜 3 9 下部電極 40 シリコン窒化膜 4 1 プレート電極 4 4 シリコン酸化膜 4 5 スルーホール 4 6 プラグ 5 0 シリコン膜 5 1 n型シリコン膜 5 2 p型シリコン膜 5 3 ゲート電極 6 0 ゲート絶縁膜 6 1 ゲート電極 6 2 半導体領域 6 3 サイドウォール 6 4 絶縁膜 65 フォトレジスト膜 6 6 金属膜 67 シリサイド膜 M 1 第 1 層配線 M 2 第 2 層 配 線 第1領域 Α В 第2領域 C 第3領域 BL ビット線 CNTL 制御回路 G ゲート電極 ゲート絶縁膜 IF インターフェース回路 IR 不純物領域 Inp 不純物

MARY メモリアレイ

P パス

PW 電源回路

SA センスアンプ

WD ワード線ドライバ

WL ワード線

# 【図1】

# 図 1

# 【図2】

<u>⊠</u>

【図3】

【図4】

$\ge$

$\boxtimes$

【図6】

$\boxtimes$

【図7】

$\ge$

【図8】

【図9】

【図10】

10

$\boxtimes$

6 ⊠

【図11】

【図12】

$\ge$

【図13】

$\ge$

【図14】

$\bowtie$

【図15】

⊠ 16

【図17】

【図18】

# 【図19】

**⊠** 20

# 【図21】

1: 井様を 17: ゲーー 21: サイー 22: ツリン 29: ツリオ A: 第16 B: 第26 C: 第36

# 【図22】

⊠ 22

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

$\ge$

【図29】

【図30】

30

$\boxtimes$

【図31】

【図33】

【図34】

34

33

$\mathbb{X}$

【図35】

$\ge$

【図36】

図 36

【図37】

【図40】

図 40

【図39】

☑ 41

# フロントページの続き

(72)発明者 吉田 省史

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 豊川 滋也

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

審査官 河口 雅英

(58)調査した分野(Int.CI., DB名)

H01L 27/108

H01L 27/04

H01L 21/822

H01L 21/8242