## (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4628801号 (P4628801)

(45) 発行日 平成23年2月9日(2011.2.9)

(24) 登録日 平成22年11月19日(2010.11.19)

| (51) Int.Cl. |        |           | FΙ   |        |     |

|--------------|--------|-----------|------|--------|-----|

| G02F         | 1/1368 | (2006.01) | GO2F | 1/1368 |     |

| G02F         | 1/1343 | (2006.01) | GO2F | 1/1343 |     |

| GO2F         | 1/1337 | (2006.01) | GO2F | 1/1337 | 505 |

| G02F         | 1/1339 | (2006.01) | GO2F | 1/1339 | 500 |

|              |        |           |      |        |     |

請求項の数 11 (全 24 頁)

最終頁に続く

| (21) 出願番号<br>(22) 出願日 | 特願2005-11519 (P2005-11519)<br>平成17年1月19日 (2005.1.19) | (73) 特許権者 | 章 000005049<br>シャープ株式会社 |

|-----------------------|------------------------------------------------------|-----------|-------------------------|

| (65) 公開番号             | 特開2006-201356 (P2006-201356A)                        |           | 大阪府大阪市阿倍野区長池町22番22号     |

| (43) 公開日              | 平成18年8月3日 (2006.8.3)                                 | (74) 代理人  | 100101214               |

| 審査請求日                 | 平成19年3月2日 (2007.3.2)                                 |           | 弁理士 森岡 正樹               |

|                       |                                                      | (72) 発明者  | 美崎 克紀                   |

|                       |                                                      |           | 神奈川県川崎市中原区上小田中4丁目1番     |

|                       |                                                      |           | 1号 富士通ディスプレイテクノロジーズ     |

|                       |                                                      |           | 株式会社内                   |

|                       |                                                      | (72) 発明者  | 藤川 徹也                   |

|                       |                                                      |           | 神奈川県川崎市中原区上小田中4丁目1番     |

|                       |                                                      |           | 1号 富士通ディスプレイテクノロジーズ     |

|                       |                                                      |           | 株式会社内                   |

|                       |                                                      |           |                         |

|                       |                                                      |           |                         |

## (54) 【発明の名称】液晶表示装置

### (57)【特許請求の範囲】

## 【請求項1】

対向配置された一対の基板と、

前記一対の基板間に封止された液晶と、

一方の前記基板上に形成された第1の画素電極と、前記一方の基板上に形成され、前記第1の画素電極から分離された第2の画素電極とをそれぞれ備えた複数の画素領域と、

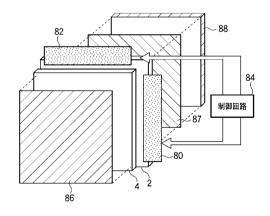

前記画素領域毎に配置され、前記第1の画素電極に電気的に接続されたソース電極を備えたトランジスタと、

他方の前記基板上に形成され、前記液晶を配向規制する線状の配向規制用構造物と、

前記第1の画素電極を通らない電気的接続経路を介して前記ソース電極<u>に電</u>気的に接続され、絶縁膜を介して前記第2の画素電極の少なくとも一部に対向し、基板面に垂直に見て少なくとも一部が前記配向規制用構造物に重なって配置されかつ前記配向規制用構造物に沿って延びる制御容量電極を備え、前記ソース電極と前記第2の画素電極とを容量結合する制御容量部と

を有することを特徴とする液晶表示装置。

## 【請求項2】

請求項1記載の液晶表示装置において、

前記制御容量電極の幅は、前記配向規制用構造物の幅よりも狭いことを特徴とする液晶表示装置。

#### 【請求項3】

請求項1又は2に記載の液晶表示装置において、

前記画素領域端部を遮光する遮光膜をさらに有し、

前記制御容量電極は、基板面に垂直に見て少なくとも一部が前記遮光膜に重なって配置 されていること

を特徴とする液晶表示装置。

#### 【請求項4】

請求項1乃至3のいずれか1項に記載の液晶表示装置において、

前記画素領域は、長さXの短辺と長さ約3Xの長辺とを有する長方形状であり、

前記配向規制用構造物は、一方の前記長辺の両端に位置する2つの前記画素領域角部を それぞれ通り、前記長辺に対し約45°の角度をなす方向であって互いにほぼ垂直な方向 にそれぞれ直線状に延伸する2つの領域を前記画素領域内に有していること

を特徴とする液晶表示装置。

#### 【請求項5】

請求項4記載の液晶表示装置において、

前記制御容量電極は、前記配向規制用構造物の前記2つの領域にそれぞれ沿って延伸す る2つの斜め延伸部と、他方の前記長辺に沿って延伸し、前記2つの斜め延伸部間を接続 する長さ約Xの接続部とを有すること

を特徴とする液晶表示装置。

### 【請求項6】

請求項5記載の液晶表示装置において、

前記配向規制用構造物の幅をYとし、前記接続部の幅をZとしたとき、

前記制御電極の前記第2の画素電極に対する重なり面積Sは、

$S (Y \times (X 2 + X 2) - Y 2 / 2) \times 2 + X \times Z$

の関係を満たすこと

を特徴とする液晶表示装置。

### 【請求項7】

請求項6記載の液晶表示装置において、

前記絶縁膜はシリコン窒化膜からなり、100nm以上300nm以下の膜厚を有する こと

を特徴とする液晶表示装置。

## 【請求項8】

請求項6又は7に記載の液晶表示装置において、

前記配向規制用構造物の幅Yは8um以上12um以下であること

を特徴とする液晶表示装置。

## 【請求項9】

請求項6乃至8のいずれか1項に記載の液晶表示装置において、

前記接続部の幅 Z は 2 μ m 以上 1 5 μ m 以下であること

を特徴とする液晶表示装置。

## 【請求項10】

請求項1乃至9のいずれか1項に記載の液晶表示装置において、

前記一対の基板間の外周部に切れ目なく塗布され、前記液晶を封止するシール材と、

前記一対の基板の双方に接触し、第1のセルギャップを維持する第1のセルギャップ維 持用構造物と、

外部から加圧されたときに前記第1のセルギャップより狭い第2のセルギャップを維持 する第2のセルギャップ維持用構造物とをさらに有すること

を特徴とする液晶表示装置。

#### 【請求項11】

請求項1乃至10のいずれか1項に記載の液晶表示装置において、

前記配向規制用構造物は、前記他方の基板上に形成された共通電極を部分的に除去した スリットであること

10

20

30

40

を特徴とする液晶表示装置。

## 【発明の詳細な説明】

#### 【技術分野】

## [0001]

本発明は、液晶分子の配向方向が相互に異なる複数の配向領域を1画素内に有するMVA(Multi-domain Vertical Alignment)方式の液晶表示装置に関し、特に、画素領域が複数の副画素に分割されている液晶表示装置に関する。

#### 【背景技術】

## [0002]

液晶表示装置は、CRT(Cathode Ray Tube)に比べて薄くて軽量であり、かつ低電圧で駆動できて消費電力が小さいという利点を有している。そのため、液晶表示装置は、ノート型PC(パーソナルコンピュータ)、PDA(携帯情報端末)及び携帯電話など、種々の電子機器に用いられている。特に、各画素(サブ画素)毎にスイッチング素子としてTFT(Thin Film Transistor:薄膜トランジスタ)を設けたアクティブマトリクス型液晶表示装置は、高い駆動能力を有している。アクティブマトリクス型液晶表示装置は、CRTにも匹敵する優れた表示特性が得られるため、デスクトップ型PCやテレビ受像機など従来CRTが用いられていた用途にも広く用いられるようになっている。

#### [0003]

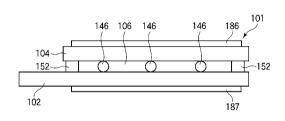

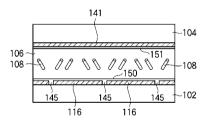

図15は、従来の液晶表示装置の概略の断面構成を示している。図15に示すように、液晶表示装置は、液晶表示パネル101を有している。液晶表示パネル101は、TFTや画素電極が画素毎に形成されたTFT基板102と、カラーフィルタ(CF)や共通電極が形成された対向基板104と、両基板102、104間に封止された液晶106とを有している。TFT基板102は、接続端子が設けられるため対向基板104よりも大きく形成されている。両基板102、104は、外周部に塗布されたシール材152を介して貼り合わされている。両基板102、104間のセルギャップは、例えば球状スペーサ146により維持されている。また、液晶表示パネル101を挟んで外側には、偏光板187、186が配置されている。偏光板187の図中下方には、バックライトユニット(図示せず)が配置されている。

## [0004]

従来は、正の誘電率異方性を有する水平配向型液晶を備え、液晶分子をツイスト配向させるTN(Twisted Nematic)モードの液晶表示装置が広く用いられていた。しかし、TNモードの液晶表示装置は、視野角特性が悪く、画面を斜め方向から見たときにコントラストや色調が大きく変化するという欠点を有している。このため、視野角特性が良好なVA(Vertically Aligned)モードの液晶表示装置及びMVA方式の液晶表示装置が開発され、実用化されている。

## [0005]

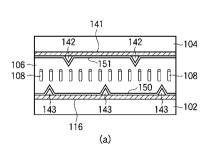

図16(a)、(b)は、MVA方式の液晶表示装置の断面構成を模式的に示している。TFT基板102及び対向基板104の間には、負の誘電率異方性を有する垂直配向型の液晶106が封止されている。TFT基板102の画素電極116上には、液晶106の配向を規制する配向規制用構造物として土手状の線状突起143が形成されている。画素電極116上及び線状突起143上には、例えばポリイミドからなる垂直配向膜150が形成されている。

## [0006]

対向基板104の共通電極141上には、配向規制用構造物として土手状の線状突起142が形成されている。線状突起142は、TFT基板102側の線状突起143に並列して延び、線状突起143に対し半ピッチずれて配置されている。共通電極141上及び線状突起142上には、例えばポリイミドからなる垂直配向膜151が形成されている。

## [0007]

MVA方式の液晶表示装置においては、画素電極116と共通電極141との間に電圧

10

20

30

40

20

30

40

50

を印加しない状態では、図16(a)に示すように、ほとんどの液晶分子108は基板面に対しほぼ垂直に配向する。但し、線状突起142、143近傍の液晶分子108は、線状突起142、143の傾斜面にほぼ垂直な方向に配向する。

#### [00008]

画素電極116と共通電極141との間に所定の電圧を印加すると、電界の影響により液晶分子108は基板面に対し斜めに傾斜する。この場合に、図16(b)に示すように、線状突起142、143の両側では液晶分子108の傾斜方向が異なる。これにより、いわゆる配向分割(マルチドメイン)が実現できる。

## [0009]

図16(b)に示すように、MVA方式の液晶表示装置では、電圧を印加したときの液晶分子108の傾斜方向が線状突起142、143の両側で異なるので、斜め方向への光の漏れが抑制され、優れた視野角特性が得られる。

#### [0010]

上記の例では配向規制用構造物が線状突起142、143の場合について説明したが、電極が部分的に除去されたスリットや、基板表面の窪み(溝)を配向規制用構造物とすることもある。また、図16(a)、(b)ではTFT基板102及び対向基板104の両方に配向規制用構造物を設けた例について説明したが、TFT基板102及び対向基板104のうちのいずれか一方のみに配向規制用構造物を形成してもよい。

#### [0011]

図17は、TFT基板102側の画素電極116のみに、配向規制用構造物としてスリット145を形成した例を示している。スリット145の縁部付近では電界に歪みが生じ、電気力線が基板面に対し斜め方向に延びるので、スリット145の両側で液晶分子108の傾斜方向が異なる。これにより配向分割が実現でき、視野角特性が向上する。

#### [0012]

図18は、TFT基板102側にスリット145が形成され、対向基板104側に線状突起142が形成されたMVA方式の液晶表示装置の1画素の構成を示している。図19は、図18のX-X線で切断したTFT基板102の断面構成を示している。図18及び図19に示すように、TFT基板102には、図中左右方向に延びる複数のゲートバスライン114とがそれぞれ所定のピッチで配置されている。これらのゲートバスライン112及びドレインバスライン114により長方形状の画素領域が画定されている。また、TFT基板102には、ゲートバスライン112に並列して画素領域の中央部を横断する蓄積容量バスライン118が形成されている。ゲートバスライン112及び蓄積容量バスライン118とドレインバスライン114との間には絶縁膜130が形成されている。絶縁膜130によりゲートバスライン114との間には絶縁膜130が形成されている。絶縁膜130によりゲートバスライン114との間には絶縁膜130が形成されている。

## [0013]

画素領域毎に、TFT120、画素電極116及び蓄積容量電極119が形成されている。TFT120は、ゲートバスライン112の一部をゲート電極としている。また、TFT120のドレイン電極121はドレインバスライン114に接続しており、ソース電極122はゲートバスライン112を挟んでドレイン電極121に対向する位置に形成されている。さらに、蓄積容量電極119は、絶縁膜130を挟んで蓄積容量バスライン118に対向する位置に形成されている。

## [0014]

蓄積容量電極119、TFT120及びドレインバスライン114は保護膜131に覆われており、画素電極116は保護膜131の上に配置される。画素電極116はITO(Indium-Tin Oxide)等の透明導電膜からなり、保護膜131に形成されたコンタクトホール125、126を介してTFT120のソース電極122及び蓄積容量電極119にそれぞれ電気的に接続されている。また、画素電極116には、斜め方向に延びる2本のスリット145が蓄積容量バスラインに対してほぼ線対称に形成されて

20

30

40

50

いる。 画素電極 1 1 6 の表面は、例えばポリイミドからなる垂直配向膜(図示せず)により覆われている。

#### [0015]

TFT基板102に対向して配置される対向基板には、遮光膜(BM)、CF樹脂層及び共通電極141が形成されている。共通電極141の上には、ゲートバスライン112及び蓄積容量バスライン118の上方で屈曲する複数の土手状の線状突起142が形成されている。線状突起142は、画素電極116のスリット145に対し半ピッチずれて並列配置されている。

## [0016]

このようなMVA方式の液晶表示装置において、画素電極116と共通電極141との間に所定の電圧を印加すると、図18及び図20に示すように、液晶分子108の配向方向が相互に異なる4つの配向領域 、 、 が形成される。配向領域 ~ は、線状突起142及びスリット145を境界として分割されている。配向領域 ~ の面積が1 画素内で互いにほぼ等しくなるように線状突起142及びスリット145を形成すると、液晶表示装置の視野角特性の方向依存性が小さくなる。

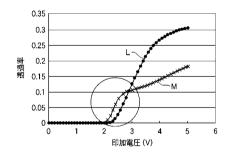

#### [0017]

ところで、従来のMVA方式の液晶表示装置では、画面を斜め方向から見たときに白っぽくなる現象が発生する。図21は、従来のMVA方式の液晶表示装置の印加電圧に対する透過率特性(T-V特性)を示すグラフである。横軸は液晶層に対する印加電圧(V)を表し、縦軸は光の透過率を表している。線Lは表示画面に対し垂直な方向(以下、「正面方向」という)でのT-V特性を示し、線Mは表示画面に対して方位角90°、極角60°の方向(以下、「斜め方向」という)でのT-V特性を示している。ここで、方位角は、表示画面の右方向を基準として反時計回りに計った角度とする。また極角は、表示画面の中心に立てた垂線となす角度とする。

## [0018]

図21に示すように、約3V以上の比較的高い電圧を液晶層に印加したときには、正面方向の透過率が斜め方向の透過率よりも高くなっている。これに対し、閾値電圧より若干高い約2~3Vの電圧を液晶層に印加したとき(円で囲んだ領域)には、斜め方向の透過率が正面方向の透過率より高くなる。この結果、斜め方向から表示画面を見た場合には、実効駆動電圧範囲での輝度差が小さくなってしまう。この現象は色の変化に最も顕著に現れる。すなわち、R、G、Bの3原色の輝度差が小さくなるため、斜め方向から見ると画面全体の色が白っぽくなり、色の再現性が低下してしまうという現象が生じる。この現象は、白茶け(discolor)と呼ばれている。白茶けは、MVA方式の液晶表示装置だけでなく、TNモードの液晶表示装置でも発生する。

## [0019]

特許文献1には、1つの画素を複数の副画素に分割して、それらの副画素を容量結合することが提案されている。このような液晶表示装置では、各副画素の容量比によって電位が分割されるため、各副画素の液晶に相互に異なる電圧を印加することができる。したがって、見かけ上、1つの画素にT・V特性のしきい値が異なる複数の領域が存在することになる。このように1つの画素にT・V特性のしきい値が異なる複数の領域が存在すると、図21の円内に示したような正面方向の透過率よりも斜め方向の透過率が高くなる現象が抑制され、その結果画面が白っぽくなる現象も抑制される。このように1つの画素を容量結合した複数の副画素に分割して表示特性を改善する方法は、容量結合HT(ハーフトーン・グレースケール)法と呼ばれる。

#### [0020]

特許文献 2 には、図 2 2 に示すように、画素電極を 4 つの副画素電極 1 1 6 a ~ 1 1 6 d に分割し、各副画素電極 1 1 6 a ~ 1 1 6 d の下方に絶縁膜を介して制御容量電極 1 1 7 a ~ 1 1 7 d をそれぞれ配置した構成を有する液晶表示装置が開示されている。この液晶表示装置では、制御容量電極 1 1 7 a ~ 1 1 7 d の大きさがそれぞれ異なっており、 T F T 1 2 0 を介して制御容量電極 1 1 7 a ~ 1 1 7 d に表示電圧が印加されるようになっ

ている。また、副画素電極116a~116dの間から光が漏れることを防止するために、副画素電極116a~116dの間にも制御容量電極115が配置されている。

#### [0021]

特許文献 3 にも、 1 つの画素を複数の副画素に分割した液晶表示装置が開示されている。この液晶表示装置では、例えば副画素毎にラビング処理条件を変化させて、副画素の液晶分子のプレチルト角を相互に異ならせている。

これらの従来の技術は、いずれもTNモードの液晶表示装置に関するものである。

## [0022]

図23は、容量結合HT法を用いた従来のMVA方式の液晶表示装置の1画素の構成を示している。図24は、図23のY・Y線で切断した液晶表示装置の断面構成を示している。図23及び図24に示すように、TFT基板102は、ガラス基板110上に形成された複数のゲートバスライン112と、絶縁膜130を介してゲートバスライン112に交差する複数のドレインバスライン114とを有している。ゲートバスライン112のピッチは例えば約300μmであり、ドレインバスライン114のピッチは例えば約100μmである。これらのゲートバスライン112及びドレインバスライン114により長方形状の画素領域が画定されている。また、TFT基板102には、ゲートバスライン112に並列して画素領域の中央部を横断する蓄積容量バスライン118が形成されている。

#### [0023]

TFT基板102には、TFT120、制御容量電極133、134及び画素電極116a~116dが画素領域毎に形成されている。画素電極116a~116dは、スリット145により互いに分割されている。スリット145は斜め方向に延び、蓄積容量バスライン118に対してほぼ線対称に形成されている。

## [0024]

TFT120は、ゲートバスライン112の一部をゲート電極としている。TFT120のドレイン電極121は、ドレインバスライン114に電気的に接続されている。ソース電極122は、ゲートバスライン112上に形成されたチャネル保護膜128を介してドレイン電極121に対向する位置に配置されている。またソース電極122は、制御容量電極133、134に電気的に接続されている。

## [0025]

副画素電極 1 1 6 a ~ 1 1 6 d は I T O 等の透明導電膜からなり、互いに同層に形成されている。これらの副画素電極 1 1 6 a ~ 1 1 6 d を分離するスリット 1 4 5 の幅は例えば 1 0  $\mu$  m である。副画素電極 1 1 6 a はコンタクトホール 1 2 5 を介して制御容量電極 1 3 3 に電気的に接続され、副画素電極 1 1 6 d はコンタクトホール 1 2 7 を介して制御容量電極 1 3 3 に電気的に接続されている。副画素電極 1 1 6 b、 1 1 6 c の一部の領域は、制御容量電極 1 3 3 ( 1 3 4 ) に保護膜 1 3 1 を介して重なっている。副画素電極 1 1 6 b、 1 1 6 c は、当該領域に形成される制御容量を介した容量結合により、制御容量電極 1 3 3、 1 3 4 に間接的に接続されている。絶縁膜 1 3 0 を介して蓄積容量バスライン 1 1 8 に対向する制御容量電極 1 3 4 は、蓄積容量バスライン 1 1 8 を一方の電極として画素毎に形成される蓄積容量の他方の電極としても機能する。副画素電極 1 1 6 a ~ 1 1 6 d は、例えばポリイミドからなる垂直配向膜 1 5 0 に覆われている。

## [0026]

一方、対向基板 1 0 4 上には、 B M 1 4 8 が形成されている。 B M 1 4 8 は例えば C r (クロム)等の金属材料で形成され、 T F T 基板 1 0 2 側のゲートバスライン 1 1 2 、蓄積容量バスライン 1 1 8 、ドレインバスライン 1 1 4 及び T F T 1 2 0 に対向する位置に配置されている。 B M 1 4 8 上には C F 樹脂層 1 4 0 が形成されている。各画素には、 R 、 G 、 B のいずれか 1 色の C F 樹脂層 1 4 0 が配置される。

#### [0027]

CF樹脂層140上には、ITO等の透明導電膜からなる共通電極141が形成されている。共通電極141上には、配向規制用構造物である土手状の線状突起142が形成されている。線状突起142は、図23に示すように、ゲートバスライン112及び蓄積容

10

20

30

40

量バスライン118の上で屈曲しており、TFT基板102のスリット145に対し半ピッチずれて並列配置されている。共通電極141及び線状突起142の表面は、例えばポリイミドからなる垂直配向膜151に覆われている。

#### [0028]

ドレインバスライン 1 1 4 に所定の階調電圧を印加し、ゲートバスライン 1 1 2 に走査信号を供給すると、TFT 1 2 0 がオン状態になる。TFT 1 2 0 がオン状態になると、ソース電極 1 2 2 に電気的に接続されている副画素電極 1 1 6 a、 1 1 6 d及び制御容量電極 1 3 3、 1 3 4 に階調電圧が印加される。また、副画素電極 1 1 6 b、 1 1 6 c は制御容量電極 1 3 3 ( 1 3 4 )と容量結合しているので、副画素電極 1 1 6 b、 1 1 6 c にも所定の電圧が印加される。

### [0029]

ただし図23及び図24に示す構成では、副画素電極116cが副画素電極116bよりも面積が小さく、かつ制御容量電極133(134)との重なり面積が大きいので、副画素電極116cの電圧のほうが副画素電極116bの電圧よりも高くなる。副画素電極116cの電圧をC、副画素電極116dの電圧をDとすると、A=D>C>Bとなる。

### [0030]

このようにして副画素電極116a~116dに電圧が印加されると、液晶分子は線状突起142及びスリット145の延びる方向に対し垂直な方向に傾斜する。このとき、液晶分子の傾斜方向は線状突起142及びスリット145の両側で反対方向となる。副画素電極116a、116dと副画素電極116cとにそれぞれ異なる電圧が印加されるので、見かけ上、1つの画素内にT・V特性の閾値が相互に異なる3つの領域が存在することになる。これにより、画面を斜め方向から見たときに画面が白っぽくなる現象が抑制される。

#### [0031]

【特許文献1】米国特許第4840460号明細書

【特許文献2】特開平5-66412号公報

【特許文献3】特開平6-332009号公報

【発明の開示】

【発明が解決しようとする課題】

### [0032]

ところが、図23及び図24に示した液晶表示装置では、制御容量電極133、134はソース電極122やドレイン電極121と同層の、光を遮光する金属層により形成されるため、画素の開口率が低下し輝度が低下してしまうという問題がある。

また、画素電極116b、116cと制御容量電極133、134との間に形成される保護膜131の膜厚によっては、光の透過率や色視角、コモン電位のシフト量等が悪化し、良好な表示品質が得られないという問題がある。

### [0033]

本発明の目的は、輝度が高く表示品質の良好な液晶表示装置を提供することにある。

### 【課題を解決するための手段】

## [0034]

上記目的は、対向配置された一対の基板と、前記一対の基板間に封止された液晶と、一方の前記基板上に形成された第1の画素電極と、前記一方の基板上に形成され、前記第1の画素電極から分離された第2の画素電極とをそれぞれ備えた複数の画素領域と、前記画素領域毎に配置され、前記第1の画素電極に電気的に接続されたソース電極を備えたトランジスタと、他方の前記基板上に形成され、前記液晶を配向規制する線状の配向規制用構造物と、前記ソース電極に電気的に接続され、絶縁膜を介して前記第2の画素電極の少なくとも一部に対向し、基板面に垂直に見て少なくとも一部が前記配向規制用構造物に重なって配置されかつ前記配向規制用構造物に沿って延びる制御容量電極を備え、前記ソース電極と前記第2の画素電極とを容量結合する制御容量部とを有することを特徴とする液晶

10

20

30

40

表示装置によって達成される。

## 【発明の効果】

#### [0035]

本発明によれば、輝度が高く表示品質の良好な液晶表示装置を実現できる。

【発明を実施するための最良の形態】

#### [0036]

#### 〔第1の実施の形態〕

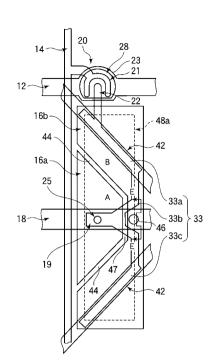

本発明の第1の実施の形態による液晶表示装置について図1乃至図7を用いて説明する。図1は、本実施の形態による液晶表示装置の概略構成を示している。図1に示すように、液晶表示装置は、絶縁膜を介して互いに交差して形成されたゲートバスライン及びドレインバスラインと、画素毎に形成されたTFT及び画素電極とを備えたTFT基板2を有している。また、液晶表示装置は、CFや共通電極が形成されてTFT基板2に対向配置された対向基板4と、両基板2、4間に封止された負の誘電率異方性を有する垂直配向型の液晶6(図1では図示せず)とを備えている。

#### [0037]

TFT基板 2 には、複数のゲートバスラインを駆動するドライバICが実装されたゲートバスライン駆動回路 8 0 と、複数のドレインバスラインを駆動するドライバICが実装されたドレインバスライン駆動回路 8 2 とが接続されている。これらの駆動回路 8 0、8 2 は、制御回路 8 4 から出力された所定の信号に基づいて、走査信号やデータ信号を所定のゲートバスラインあるいはドレインバスラインに出力するようになっている。TFT基板 2 のTFT素子形成面と反対側の面には偏光板 8 7 が配置され、対向基板 4 の共通電極形成面と反対側の面には、偏光板 8 7 とクロスニコルに配置された偏光板 8 6 が配置されている。偏光板 8 7 の TFT基板 2 と反対側の面にはバックライトユニット 8 8 が配置されている。

#### [0038]

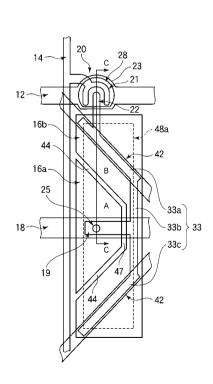

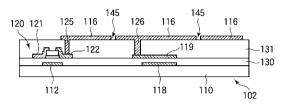

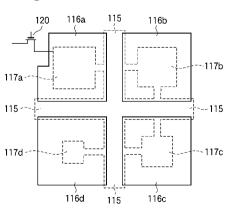

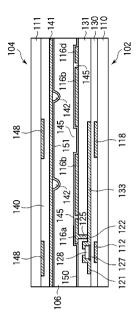

## [0039]

ゲートバスライン 1 2 及びドレインバスライン 1 4 の交差位置近傍には、例えばチャネルエッチ型のTFT 2 0 が形成されている。TFT 2 0 のゲート電極 2 3 は、ゲートバスライン 1 2 に電気的に接続されている。ゲート電極 2 3 上には動作半導体層 2 8 が形成されている。動作半導体層 2 8 上には、棒状のソース電極 2 2 と、所定の間隙を介してソース電極 2 2 を囲む C 字状のドレイン電極 2 1 とが形成されている。ドレイン電極 2 1 はドレインバスライン 1 4 に電気的に接続されている。

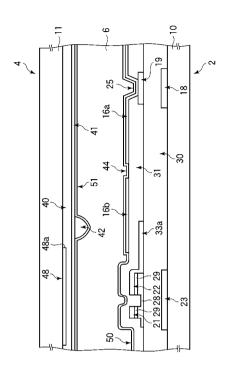

#### [0040]

TFT20上の基板全面には、例えばシリコン窒化膜(SiN膜)からなる保護膜31が形成されている。保護膜31上には、ゲートバスライン12及びドレインバスライン14の交差部毎に、画素電極16a、16bが形成されている。画素電極16a、16bの形成された長方形状の領域が画素領域になっている。画素領域は、画素電極16aの形成された副画素Aと、画素電極16bの形成された副画素Bとに分割されている。副画素Aは例えば台形状の形状を有し、画素領域の中央部左寄りに配置されている。副画素Bは、画素領域のうち副画素Aの領域を除いた図2中上部、下部及び中央部右側端部に配置されている。副画素A、Bの配置は、蓄積容量バスライン18に対し1画素内でそれぞれほぼ

10

20

30

40

線対称になっている。画素電極16a、16bは、例えば共にITO等の透明導電膜からなり互いに同層に形成されている。

#### [0041]

画素電極16a、16bは、台形状の画素電極16aの3辺を略「く」の字状に囲むスリット44、47、44によって互いに分離されている。スリット44は画素領域端部に対し斜めに延び、スリット47は画素領域右側端部に沿って延びている。スリット44、47の幅は例えば10μmである。スリット44は、液晶の配向を規制する配向規制用構造物としても機能する。

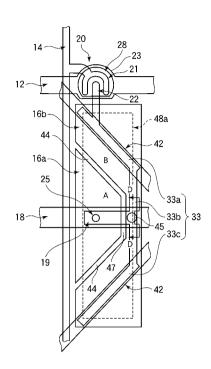

## [0042]

副画素 B には、制御容量電極 3 3 が形成されている。制御容量電極 3 3 はソース電極 2 2 に電気的に接続され、例えばソース電極 2 2 と同層に形成されている。制御容量電極 3 3 は、スリット 4 4 にそれぞれ並列し、画素領域端部に対し斜めに延びる斜め延伸部 3 3 a、 3 3 c と、画素領域の図 2 中右側の長辺に沿って延び、斜め延伸部 3 3 a、 3 3 c 間を接続する接続部 3 3 bとを有している。制御容量電極 3 3 は、保護膜(絶縁膜)3 1 を介して画素電極 1 6 bの一部の領域に重なって配置されている。保護膜 3 1 を介して対向する当該領域の画素電極 1 6 b と制御容量電極 3 3 との間には、制御容量 C c が制御容量部として形成される。

#### [0043]

蓄積容量バスライン 1 8 上には、絶縁膜 3 0 を介して蓄積容量電極 1 9 が画素毎に形成されている。絶縁膜 3 0 を介して対向する蓄積容量バスライン 1 8 と蓄積容量電極 1 9 との間には、蓄積容量 C s が形成される。蓄積容量電極 1 9 は、保護膜 3 1 を開口したコンタクトホール 2 5 を介し、画素電極 1 6 a に電気的に接続されている。また蓄積容量電極 1 9 は、制御容量電極 3 3 及びソース電極 2 2 に電気的に接続されている。

#### [0044]

副画素 A の画素電極 1 6 a は、蓄積容量電極 1 9 及び制御容量電極 3 3 を介してTFT 2 0 のソース電極 2 2 に電気的に接続されている。一方、副画素 B の画素電極 1 6 b は電気的にフローティング状態になっている。画素電極 1 6 b は、制御容量 C c を介した容量結合により、ソース電極 2 2 に間接的に接続されている。画素電極 1 6 a 、 1 6 b 及び保護膜 3 1 は、例えばポリイミドからなる垂直配向膜 5 0 に覆われている。

## [0045]

一方、対向基板 4 は、ガラス基板 1 1上に形成され、画素領域端部を遮光する B M 4 8 を有している。 B M 4 8 は例えば C r 等の金属材料で形成され、 T F T 基板 2 側のゲートバスライン 1 2、ドレインバスライン 1 4 及び T F T 2 0 に対向する位置に配置されている。 B M 4 8 の開口部 4 8 a は、両基板 2、 4 の貼合せずれ等を考慮して、画素電極 1 6 a、 1 6 b の形成された画素領域より狭くなっている。 B M 4 8 上には C F 樹脂層 4 0 が形成されている。各画素には、 R、 G、 B のいずれか 1 色の C F 樹脂層 4 0 が配置される

### [0046]

CF樹脂層40上には、ITO等の透明導電膜からなる共通電極41が形成されている。液晶層を介して対向する副画素Aの画素電極16aと共通電極41との間には液晶容量C1c1が形成され、副画素Bの画素電極16bと共通電極41との間には液晶容量C1c2が形成される。共通電極41上には、配向規制用構造物である土手状の線状突起42が形成されている。線状突起42は、感光性樹脂等を用いて形成されている。線状突起42は、ゲートバスライン12及び蓄積容量バスライン18の上で屈曲しており、TFT基板2のスリット44に並列して配置されている。線状突起42の幅は8~12μm程度(例えば10μm)であり、高さは1~1.6μm程度である。共通電極41及び線状突起42の表面は、例えばポリイミドからなる垂直配向膜51に覆われている。なお、対向基板4上の配向規制用構造物としては、共通電極41を部分的に除去したスリットを線状突起42に代えて形成してもよい。

## [0047]

50

30

20

10

20

30

40

50

TFT20がオン状態になって画素電極16aに所定の電圧が印加され、副画素Aの液晶層に電圧Vp×1が印加されるとする。このとき、液晶容量Clc2と制御容量Ccとの容量比に従って電位が分割されるため、副画素Bの画素電極16bには画素電極16aとは異なる電圧が印加される。副画素Bの液晶層に印加される電圧Vp×2は、

V p x 2 = ( C c / ( C l c 2 + C c ) ) x V p x 1

となる。ここで、0<(Cc/(Clc2+Cc))<1であるため、Vp×1=Vp×2=0以外では電圧Vp×2は電圧Vp×1より大きさが小さくなる(Vp×2=0) Vp×2=0 Vp×1=0 Vp×2=0 Vp×1=0 Vp×2=0 Vp×1=0 Vp×2=0 Vp×1=0 Vp×2=0 Vp×1=0 Vp×2=0 Vp×1=0 Vp×2=0 Vp×2=0

#### [0048]

ここで、TFT基板 2 に形成された制御容量電極 3 3 の斜め延伸部 3 3 a、 3 3 c の少なくとも一部は、対向基板 4 に形成された線状突起 4 2 に沿って延び、かつ基板面に垂直に見て線状突起 4 2 に重なって配置されている。斜め延伸部 3 3 a、 3 3 c (及び接続部 3 3 b)の幅は線状突起 4 2 の幅より細くなっている。本例では、斜め延伸部 3 3 a、 3 c は基板面に垂直に見て線状突起 4 2 両側端部より内側に配置され、斜め延伸部 3 3 a、 3 3 c のほぼ全域が線状突起 4 2 に重なっている。また、制御容量電極 3 3 の少なくとも一部は、基板面に垂直に見て B M 4 8 に重なって配置されている。例えば、接続部 3 3 b のうち面積比 6 0 %以上の領域が B M 4 8 に重なっている。

#### [0049]

画素内における線状突起42の形成領域は、他の領域に比べて光透過率が低くなっている。本実施の形態では、制御容量電極33の少なくとも一部を線状突起42に重なるように配置することによって、実質的な画素の開口率が向上し、従来に比べてより一層明るい表示が可能になる。同様に、制御容量電極33の少なくとも一部を、光を遮光するBM48に重なるように配置することによって、画素の開口率が向上し、従来に比べてより一層明るい表示が可能になる。

## [0050]

副画素 A、 Bの電圧比 V p x 2 / V p x 1 (= C c / (C 1 c 2 + C c ))は、容量比 C c / C 1 c 2 が大きくなるほど大きく(1に近く)なり、容量比 C c / C 1 c 2 が小さくなるほど大きく(1に近く)なり、容量比 C c / C 1 c 2 が小さくなるほど小さく(0に近く)なる。したがって、制御容量 C c を調整することにより、電圧比 V p x 2 / V p x 1を変化させることができる。制御容量 C c は、制御容量電極 3 3 と画素電極 1 6 b との重なり面積、保護膜 3 1 の膜厚、及び保護膜 3 1 の形成材料の誘電率により決まる。ただし、本実施の形態では保護膜 3 1 の形成材料として S i N が用いられているため、誘電率はほぼ一定である。

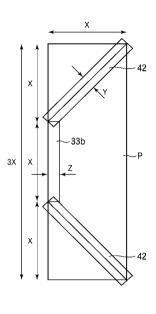

## [0051]

図4は、画素電極16a、16b(及びスリット44、47)の形成された画素領域Pと線状突起42と制御容量電極33の接続部33bとをTFT基板2側から見た構成を模式的に示している。図4に示すように、画素領域Pは、長さXの短辺と長さ3Xの長辺とを有する長方形状である。長さXは50~100μm程度であり、例えば65μmである。画素領域P内の線状突起42は、画素領域Pの図中右側の長辺の両端に位置する2つの角部をそれぞれ通り、当該長辺に対し45°の角度をなす方向であって互いにほぼ垂直な方向にそれぞれ直線状に延伸する2つの領域を有している。線状突起42の幅はY(例えば10μm)である。上記の2つの領域にそれぞれ沿って延伸する制御容量電極33の斜め延伸部33a、33c(図4では図示せず)と線状突起42との重なり幅は、例えば7μmである。制御容量電極33の接続部33bは、画素領域Pの図中左側の長辺に沿って延伸している。接続部33bの長さは画素領域Pの短辺の長さと同じXであり、接続部33bの幅はZ(2~15μm程度(例えば5μm))である。本実施の形態では、画素領域P内での制御容量電極33の面積(すなわち制御容量電極33と画素電極16bとの重

20

30

40

なり面積) Sが式(1)の関係を満たしている。

$S (Y \times (X^2 + X^2) - Y^2 / 2) \times 2 + X \times Z \cdots (1)$

### [0052]

例えば X=65 (  $\mu$  m ) 、 Y=10 (  $\mu$  m ) 、 Z=5 (  $\mu$  m ) の場合には、面積 S をおよそ Z=100  $\mu$  m  $^2$  以下にする。本例では面積 S を Z=5 (  $\mu$  m ) の場合には、面積 Z=5 を Z=5 ( Z=5 ( Z=5 ( Z=5 ) の Z=5 と Z=5 ( Z=5 ) の Z=5 と Z=5 と

## [0053]

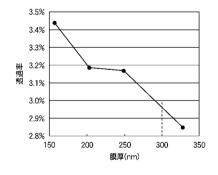

図 5 は、面積 S が 1 1 4 6 . 0 7  $\mu$  m  $^2$  の場合における保護膜 3 1 の膜厚と所定電圧印加時の画素の光透過率との関係を示すグラフである。横軸は膜厚(n m)を表し、縦軸は透過率を表している。図 5 に示すように、保護膜 3 1 の膜厚が厚くなるほど光透過率が減少している。保護膜 3 1 の膜厚をおよそ 3 0 0 n m以下にすることにより、面積 S が式(1)を満たす範囲内で変動することを考慮しても 3 . 0 %以上の光透過率が得られ、輝度の高い液晶表示装置を実現できることが分かる。

#### [0054]

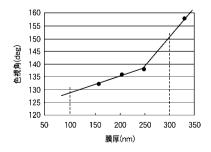

図 6 は、面積 S が 1 1 4 6 . 0 7  $\mu$  m  $^2$  の場合における保護膜 3 1 の膜厚と色視角 ( u ' v ' < 0 . 0 4 ) との関係を示すグラフである。横軸は膜厚 ( n m ) を表し、縦軸は色視角 ( d e g ) を表している。図 6 に示すように、保護膜 3 1 の膜厚が薄くなるほど色視角が減少している。保護膜 3 1 の膜厚をおよそ 1 0 0 n m以上にすることにより、面積 S が式 ( 1 ) を満たす範囲内で変動することを考慮しても、 1 3 0 ° 以上の色視角が得られ、白茶けの生じない液晶表示装置を実現できることが分かる。図 5 及び図 6 に示すグラフから、保護膜 3 1 の膜厚をおよそ 1 0 0 n m以上 3 0 0 n m以下 ( 例えば 2 0 0 n m ) にすることにより、輝度が高く白茶けの生じない表示品質の良好な液晶表示装置が得られることが分かる。なお、本例では制御容量 C c は 3 0 5 ~ 4 0 5 f F 程度 ( 例えば 3 5 5 . 2 f F ) であった。また、保護膜 3 1 の膜厚を 2 0 0 n m とした場合に良好な表示品質の得られる面積 S の範囲は、 9 8 0 ~ 1 3 2 5  $\mu$  m  $^2$  程度であった。

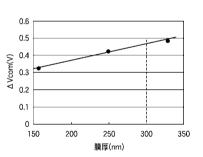

#### [0055]

図 7 は、面積 S が 1 1 4 6 . 0 7  $\mu$  m  $^2$  の場合における保護膜 3 1 の膜厚とコモン電位のシフト量 V c o m との関係を示すグラフである。横軸は膜厚 ( n m ) を表し、縦軸は 1 2 0 分間白を表示させた場合の 2 2 3 階調でのコモン電位のシフト量 V c o m ( V ) を表している。図 7 に示すように、保護膜 3 1 の膜厚が厚くなるほどシフト量 V c o m が大きくなっている。上記のように保護膜 3 1 の膜厚を 3 0 0 n m ( 1 0 0 n m 以上 ) に することによって、コモン電位のシフト量 V c o m がおよそ 0 . 4 7 V 以下に抑えられ、焼付き等が生じ難く良好な表示品質が得られることが分かる。

## [0056]

次に、本実施の形態による液晶表示装置の製造方法について図2及び図3を参照して説明する。まずTFT基板2の製造方法について説明する。

ガラス基板10上に、例えばPVD(Physical Vapor Deposition)法によりCrからなる金属膜、又はAl(アルミニウム)とTi(チタン)との積層構造を有する金属膜を形成する。その後、フォトリソグラフィ法を用いてこの金属膜をパターニングして、ゲートバスライン12、ゲート電極23及び蓄積容量バスライン18を形成する。なお、ガラス基板10からの不純物の拡散を防止するために、ガラス基板10の表面を絶縁膜で覆ってから金属膜を形成してもよい。

#### [0057]

次に、ゲートバスライン12、ゲート電極23及び蓄積容量バスライン18上の基板全面に、例えばCVD(Chemical Vapor Deposition)法により酸化シリコン又は窒化シリコンを堆積させて、ゲートバスライン12及び蓄積容量バスライン18を覆う絶縁膜30を形成する。

## [0058]

次に、絶縁膜30上の全面に、例えばCVD法等を用いて厚さ80~200nmのアモルファスシリコン(a‐Si)膜(又はポリシリコン(p‐Si)膜)と、n型不純物が高濃度に導入されたa‐Si膜(n‐a‐Si膜)とを順次形成する。その後、フォトリソグラフィ法によりn‐a‐Si膜とa‐Si膜(又はp‐Si膜)をパターニングして島状化し、TFT20のオーミックコンタクト層29及び動作半導体層28を形成する。

[0059]

次に、オーミックコンタクト層29上の基板全面に、例えばTi-Al-Tiの積層構造を有する金属膜を形成する。そして、フォトリソグラフィ法により金属膜、オーミックコンタクト層29及び動作半導体層28をパターニングして、TFT20の動作半導体層28の形状を確定するとともに、ドレインバスライン14、ソース電極22、ドレイン電極21、制御容量電極33及び蓄積容量電極19を形成する。

[0060]

[0061]

次に、ドレインバスライン14等の上の基板全面に、例えばCVD法により窒化シリコンを200nm堆積させて保護膜31を形成する。そして、フォトリソグラフィ法により保護膜31の所定位置に、蓄積容量電極19に通じるコンタクトホール25を形成する。

次いで、保護膜31上の全面に、スパッタ法等によりITO膜を形成する。その後、フォトリソグラフィ法によりITO膜をパターニングして、画素電極16a、16bを形成する。画素電極16aは、コンタクトホール25を介して蓄積容量電極19に電気的に接続される。次に、画素電極16a、16b上の基板全面にポリイミドを塗布して垂直配向膜50を形成する。このようにしてTFT基板2が完成する。

[ 0 0 6 2 ]

次に、対向基板 4 の製造方法について説明する。まず、ガラス基板 1 1 上の全面に、例えば C r 等の金属膜を形成する。この金属膜をパターニングして、TFT基板 2 側のゲートバスライン 1 2 、ドレインバスライン 1 4 及びTFT 2 0 に対応する位置に B M 4 8 を形成する。

[0063]

次に、例えば赤色感光樹脂、緑色感光樹脂及び青色感光樹脂を用いて、R、G、BのCF樹脂層40を各画素領域に順次形成する。画素毎に赤色、緑色及び青色のいずれか1色のCF樹脂層40が配置されるようにする。

[0064]

次に、CF樹脂層 4 0 上にITO膜をスパッタ法により形成し、共通電極 4 1 を形成する。次に、例えばフォトレジストを用いて、共通電極 4 1 上に誘電体からなる土手状の線状突起 4 2 を形成する。次いで、共通電極 4 1 上及び線状突起 4 2 上の全面にポリイミドを塗布して、垂直配向膜 5 0 を形成する。このようにして対向基板 4 が完成する。

[0065]

以上の工程を経て作製されたTFT基板 2 と対向基板 4 とを、例えば球状スペーサを挟んで貼り合わせる。次に、TFT基板 2 と対向基板 4 との間に、負の誘電率異方性を有する垂直配向型の液晶 6 を注入して封止する。このようにして、本実施の形態による液晶表示装置が完成する。以上のように、本実施の形態によれば、輝度が高く表示品質の良好な液晶表示装置が得られる。

[0066]

[第2の実施の形態]

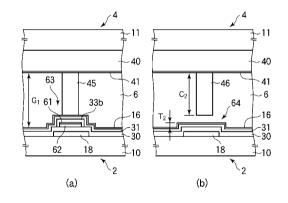

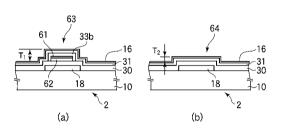

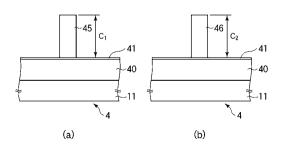

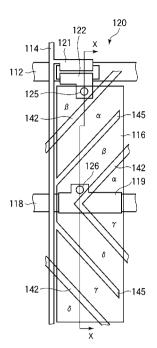

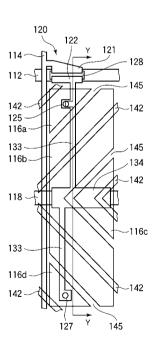

次に、本発明の第2の実施の形態による液晶表示装置について図8乃至図14を用いて説明する。図8は本実施の形態による液晶表示装置のB画素(青色のCF樹脂層が形成された画素)の構成を示し、図9は本実施の形態による液晶表示装置のR画素又はG画素(赤色又は緑色のCF樹脂層が形成された画素)の構成を示している。図10(a)は図8のD-D線で切断した液晶表示装置の断面構成を示し、図10(b)は図9のE-E線で切断した液晶表示装置の断面構成を示している。図11はTFT基板2と貼り合わせる前の対向基板4の断面構成を示している。図11(a)は図10(a)と同位置で切断した

10

20

30

40

20

30

40

50

対向基板4の断面構成を示し、図11(b)は図10(b)と同位置で切断した対向基板4の断面構成を示している。図12は対向基板4と貼り合わせる前のTFT基板2の断面構成を示している。図12(a)は図10(a)と同位置で切断したTFT基板2の断面構成を示し、図12(b)は図10(b)と同位置で切断したTFT基板2の断面構成を示している。

## [0067]

図8乃至図12(a)、(b)に示すように、本実施の形態においては、B画素とR画素及びG画素とではTFT基板2側の構成が互いに異なっている。TFT基板2のB画素は、図2とほぼ同様の構成を有している。B画素の対向基板4側には、接続部33bと蓄積容量電極19とがT字状に交わる領域に、例えばアクリル樹脂系ネガ型感光性レジストからなる柱状スペーサ45が形成されている。柱状スペーサ45の形成領域と画素開口部とのTFT基板2側の構成を比較すると、柱状スペーサ45の形成領域は、TFT20のゲート電極23と同層に形成された蓄積容量バスライン18と、動作半導体層28と同層に形成されたa-Si層62と、オーミックコンタクト層29と同層に形成されたn・a-Si層61と、ソース電極22及びドレイン電極21と同層に形成された接続部33b(蓄積容量電極19)とを有している。これにより、柱状スペーサ45の形成領域には、高さT1の凸部63が形成される。柱状スペーサ45及び凸部63は、第1のセルギャップ維持用構造物を構成する。第1のセルギャップ維持用構造物は、対向基板4及びTFT基板2の双方に接触し、セルギャップG1を維持している。

## [0068]

R画素及びG画素の対向基板 4 には、柱状スペーサ 4 5 と同一層の柱状スペーサ 4 6 が形成されている。B画素の構成と異なり、R画素及びG画素の接続部 3 3 b 及び蓄積容量電極 1 9 は、柱状スペーサ 4 6 の形成領域を迂回するように配置されている。したがって、柱状スペーサ 4 6 の形成領域は蓄積容量バスライン 1 8 を有しているが、柱状スペーサ 4 5 の形成領域と比較すると、a - Si層 6 2、n  $^+$  a - Si層 6 1 及び接続部 3 3 b を有していない。これにより、柱状スペーサ 4 6 の形成領域には、a - Si層 6 2、n  $^+$  a - Si層 6 1 及び接続部 3 3 b の各膜厚の総和分だけ凸部 6 3 より低い高さ T 2 の凸部 6 4 が形成される(T 1 > T 2)。本例では、高さ T 1 と高さ T 2 との差(T 1 - T 2)は例えば 0 . 5 0  $\mu$  mである。柱状スペーサ 4 6 及び凸部 6 4 は、第 2 のセルギャップ維持用構造物を構成する。基板貼合せ前には、柱状スペーサ 4 5 の共通電極 4 1 からの高さ C 1 と柱状スペーサ 4 6 の共通電極 4 1 からの高さ C 2 とはほぼ同一であり(C 1 = C 2)、例えば共に 3 . 2  $\mu$  mである。

#### [0069]

本実施の形態による液晶表示装置は滴下注入(ODF)法を用いて作製されており、基板 2、 4間の外周部には液晶を封止するために切れ目なく塗布されたシール材が形成されている。ODF法を用いて作製される液晶表示装置のセルギャップG1は、滴下される液晶量により決まる。本実施の形態では、基板 2、 4間のセルギャップG1が(T1+C1) < G 1 < (T2+C2)の関係を満たすような液晶量が滴下される。したがって、柱状スペーサ 4 5 と凸部 6 3 は互いに接触し、(G 1 - (T2 + C 2))(例えば 0 . 2 5  $\mu$  m)だけ圧縮される。一方、柱状スペーサ 4 6 と凸部 6 4 とは互いに接触せず、(G 1 - (T1 + C 1))(例えば 0 . 2 5  $\mu$  m)の間隙を介して対向する。すなわち、柱状スペーサ 4 5 及び凸部 6 3 を備えた第 1 のセルギャップ維持用構造物は、常時セルギャップ G 1 を維持し、柱状スペーサ 4 6 及び凸部 6 4 を備えた第 2 のセルギャップ維持用構造物は、外部から加圧されたときにセルギャップ G 1 より狭いセルギャップ G 2 (図示せず)を維持するようになっている。

## [0070]

柱状スペーサ 4 5 の上底面積(第 1 のセルギャップ維持用構造物の支持面積) S 1 と柱状スペーサ 4 6 の上底面積(第 2 のセルギャップ維持用構造物の支持面積) S 2 とはほぼ同一であり(S 1 = S 2)、例えば共に 3 0 0  $\mu$  m  $^2$  である。柱状スペーサ 4 5 は 5 つの B 画素に 1 つ配置され、柱状スペーサ 4 6 は全 R 画素及び全 G 画素に配置されている。 し

20

30

40

50

たがって、第1のセルギャップ維持用構造物の面積密度 D 1 は、第2のセルギャップ維持用構造物の面積密度 D 2 の 1 / 1 0 になっている( D 1 : D 2 = 1 : 1 0 )。なお、柱状スペーサ 4 5 が形成されない B 画素の T F T 基板 2 側の構成は、 R 画素及び G 画素の T F T 基板 2 側の構成と同様であってもよい。

## [0071]

例えば製造ばらつきにより柱状スペーサ 4 5 が 0 . 1 5  $\mu$  m低く形成された場合であっても、基板貼合せ後には柱状スペーサ 4 5 (及び凸部 6 3 ) は 0 . 1 0  $\mu$  mだけ圧縮されることになる。したがって、作製した液晶表示パネルは重力むらの発生しない内部圧力を有する。一方、柱状スペーサ 4 6 が 0 . 1 5  $\mu$  m高く形成された場合であっても、基板貼合せ後には柱状スペーサ 4 6 と凸部 6 4 の間には 0 . 1 0  $\mu$  mの間隙が存在するため、常温時に互いに接触しないことになる。したがって、低温下での気泡の発生を防止できる。

#### [0072]

また、液晶表示パネルの基板 2 、 4 間に外部から高い圧力が加えられたときには、第 1 のセルギャップ維持用構造物に加えて第 2 のセルギャップ維持用構造物もセルギャップを維持する。したがって、セルギャップむらが生じず、外部からの加圧に対する高い耐性が得られる。

### [0073]

本実施の形態によれば第1の実施の形態と同様の効果が得られるだけでなく、外部から圧力が加えられていないときには低い面積密度 D 1 で形成された第1のセルギャップ維持用構造物だけがセルギャップ G 1 を維持しているため、低温下での気泡の発生を防止できる。一方、外部から圧力が加えられたときには高い面積密度(D 1 + D 2 )で形成された第1及び第2のセルギャップ維持用構造物がセルギャップ G 2 を維持するため、セルギャップむらを抑制できる。また、本実施の形態によれば、O D F 法を用いて作製される液晶表示装置において、広い製造マージン及び高い耐加圧性という相反する 2 つの効果を同時に実現できる。

## [0074]

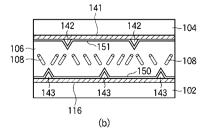

次に、本実施の形態による液晶表示装置の製造方法について簡単に説明する。図13は、対向基板4の製造工程を示している。まず、図13(a)に示すように、ガラス基板11等の絶縁性基板上にCr金属又は樹脂ブラックを用いてBM48を形成する。次に、図13(b)に示すように、顔料分散型感光性着色樹脂等を用いてCF樹脂層40R、40G、40Bを順次形成する。次に、図13(c)に示すように、ITO等の透明導電膜をスパッタリングして共通電極41を形成する。次に、図13(d)に示すように、例えばノボラック樹脂系ポジ型感光性レジストを基板全面に塗布し、フォトリソグラフィ法を用いて所定の配置パターンの線状突起42を形成する。次に、図13(e)に示すように、例えばアクリル樹脂系ネガ型感光性レジストを基板全面に塗布し、フォトリソグラフィ法を用いて所定の位置に所定の上底面積を有する柱状スペーサ45、46を形成する。柱状スペーサ45は例えば5つのB画素に1つの配置密度で配置され、柱状スペーサ46は全R画素及び全G画素に1つずつの配置密度で配置される。以上の工程を経て、対向基板4が作製される。

### [0075]

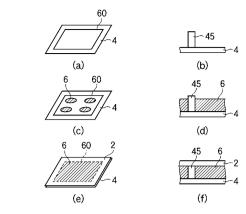

図14は、ODF法を用いた液晶表示パネルの製造工程を示す図である。図14(a)、(c)、(e)は各工程での対向基板4の状態を示す斜視図であり、図14(b)、(d)、(f)は各工程での柱状スペーサ45(又は46)近傍の状態を示す概略断面図である。まず対向基板4及び別工程で作製されたTFT基板2の表面に配向膜を形成し、図14(a)、(b)に示すように、例えば対向基板4の外周部の全周に、光硬化型のシール材60を切れ目なく塗布する。次に、図14(c)、(d)に示すように、対向基板4上に所定量の液晶6を滴下する。なお図14(d)では、滴下された状態の液晶6ではなく、後述する工程で充填された状態の液晶6を示している。次に、図14(e)、(f)に示すように、対向基板4とTFT基板2とを真空中で貼り合わせ、大気圧に戻すことにより液晶6を基板2、4間に充填する。このとき、セルギャップは液晶6の滴下量により

制御され、柱状スペーサ45はTFT基板2に接触して所定の変位量だけ圧縮される。シール材60を硬化させた後、パネル切断、偏光板貼付け等の工程を経て液晶表示パネルが完成する。その後、モジュール工程等を経て液晶表示装置が完成する。

#### [0076]

本発明は、上記実施の形態に限らず種々の変形が可能である。

例えば、上記実施の形態では透過型の液晶表示装置を例に挙げたが、本発明はこれに限らず、反射型や半透過型等の他の液晶表示装置にも適用できる。

### [0077]

また上記実施の形態では、2つの副画素を備えた画素領域を有する液晶表示装置を例に 挙げたが、本発明はこれに限らず、3つ又はそれ以上の副画素を備えた画素領域を有する 液晶表示装置にも適用できる。

[0078]

さらに上記実施の形態では、チャネルエッチ型のTFTを備えた液晶表示装置を例に挙げたが、本発明はこれに限らず、チャネル保護膜型のTFTを備えた液晶表示装置にも適用できる。

#### [0079]

以上説明した実施の形態による液晶表示装置は、以下のようにまとめられる。

### (付記1)

対向配置された一対の基板と、

前記一対の基板間に封止された液晶と、

一方の前記基板上に形成された第1の画素電極と、前記一方の基板上に形成され、前記第1の画素電極から分離された第2の画素電極とをそれぞれ備えた複数の画素領域と、

前記画素領域毎に配置され、前記第1の画素電極に電気的に接続されたソース電極を備 えたトランジスタと、

他方の前記基板上に形成され、前記液晶を配向規制する線状の配向規制用構造物と、

前記ソース電極に電気的に接続され、絶縁膜を介して前記第2の画素電極の少なくとも一部に対向し、基板面に垂直に見て少なくとも一部が前記配向規制用構造物に重なって配置されかつ前記配向規制用構造物に沿って延びる制御容量電極を備え、前記ソース電極と前記第2の画素電極とを容量結合する制御容量部と

を有することを特徴とする液晶表示装置。

### (付記2)

付記1記載の液晶表示装置において、

前記制御容量電極の幅は、前記配向規制用構造物の幅よりも狭いこと

を特徴とする液晶表示装置。

### (付記3)

付記1又は2に記載の液晶表示装置において、

前記画素領域端部を遮光する遮光膜をさらに有し、

前記制御容量電極は、基板面に垂直に見て少なくとも一部が前記遮光膜に重なって配置されていること

を特徴とする液晶表示装置。

## (付記4)

付記1乃至3のいずれか1項に記載の液晶表示装置において、

前記画素領域は、長さXの短辺と長さ約3Xの長辺とを有する長方形状であり、

前記配向規制用構造物は、一方の前記長辺の両端に位置する2つの前記画素領域角部を それぞれ通り、前記長辺に対し約45°の角度をなす方向であって互いにほぼ垂直な方向 にそれぞれ直線状に延伸する2つの領域を前記画素領域内に有していること

を特徴とする液晶表示装置。

## (付記5)

付記4記載の液晶表示装置において、

前記制御容量電極は、前記配向規制用構造物の前記2つの領域にそれぞれ沿って延伸す

20

10

30

30

40

る 2 つの斜め延伸部と、他方の前記長辺に沿って延伸し、前記 2 つの斜め延伸部間を接続する長さ約 X の接続部とを有すること

を特徴とする液晶表示装置。

(付記6)

付記5記載の液晶表示装置において、

前記配向規制用構造物の幅をYとし、前記接続部の幅をZとしたとき、

前記制御電極の前記第2の画素電極に対する重なり面積Sは、

$S (Y \times (X^2 + X^2) - Y^2 / 2) \times 2 + X \times Z$

の関係を満たすこと

を特徴とする液晶表示装置。

(付記7)

付記6記載の液晶表示装置において、

前記絶縁膜はシリコン窒化膜からなり、100nm以上300nm以下の膜厚を有すること

を特徴とする液晶表示装置。

(付記8)

付記6又は7に記載の液晶表示装置において、

前記配向規制用構造物の幅Υは8μm以上12μm以下であること

を特徴とする液晶表示装置。

(付記9)

付記6乃至8のいずれか1項に記載の液晶表示装置において、

前記接続部の幅 Z は 2 μ m 以上 1 5 μ m 以下であること

を特徴とする液晶表示装置。

(付記10)

付記1乃至9のいずれか1項に記載の液晶表示装置において、

前記一対の基板間の外周部に切れ目なく塗布され、前記液晶を封止するシール材と、

前記一対の基板の双方に接触し、第1のセルギャップを維持する第1のセルギャップ維持用構造物と、

外部から加圧されたときに前記第1のセルギャップより狭い第2のセルギャップを維持する第2のセルギャップ維持用構造物とをさらに有すること

を特徴とする液晶表示装置。

(付記11)

付記10記載の液晶表示装置において、

前記第1のセルギャップ維持用構造物は、前記トランジスタのゲート電極と同層に形成された第1層と、前記ソース電極と同層に形成された第2層とを共に有し、

前記第2のセルギャップ維持用構造物は、前記第1層又は前記第2層のいずれか一方を 有すること

を特徴とする液晶表示装置。

【図面の簡単な説明】

[0800]

【図1】本発明の第1の実施の形態による液晶表示装置の概略構成を示す図である。

【図2】本発明の第1の実施の形態による液晶表示装置の1画素の構成を示す図である。

【図3】本発明の第1の実施の形態による液晶表示装置の構成を示す断面図である。

【図4】画素領域Pと線状突起42と制御容量電極33の接続部33bとを模式的に示す図である。

【図5】保護膜31の膜厚と画素の光透過率との関係を示すグラフである。

【図6】保護膜31の膜厚と色視角との関係を示すグラフである。

【図7】保護膜31の膜厚とコモン電位のシフト量 Vcomとの関係を示すグラフである。

【図8】本発明の第2の実施の形態による液晶表示装置のB画素の構成を示す図である。

10

20

30

30

40

- 【図9】本発明の第2の実施の形態による液晶表示装置のR画素又はG画素の構成を示す 図である。

- 【図10】本発明の第2の実施の形態による液晶表示装置の断面構成を示す図である。

- 【図11】TFT基板2と貼り合わせる前の対向基板4の構成を示す断面図である。

- 【図12】対向基板4と貼り合わせる前のTFT基板2の構成を示す断面図である。

- 【図13】対向基板4の製造工程を示す図である。

- 【図14】ODF法を用いた液晶表示パネルの製造工程を示す図である。

- 【図15】従来の液晶表示装置の概略の断面構成を示す図である。

- 【図16】MVA方式の液晶表示装置の断面構成を模式的に示す図である。

- 【図17】MVA方式の液晶表示装置の断面構成の他の例を模式的に示す図である。

- 【図18】MVA方式の液晶表示装置の1画素の構成を示す図である。

- 【図19】MVA方式の液晶表示装置の断面構成を示す図である。

- 【図20】MVA方式の液晶表示装置の液晶分子の配向方向を模式的に示す図である。

- 【図21】MVA方式の液晶表示装置のT-V特性を示すグラフである。

- 【図22】特許文献2に開示された液晶表示装置の構成を示す図である。

- 【図23】容量結合HT法を用いた従来のMVA方式の液晶表示装置の1画素の構成を示 す図である。

- 【図24】容量結合HT法を用いた従来のMVA方式の液晶表示装置の断面構成を示す図 である。

【符号の説明】

- [0081]

- 2 TFT基板

- 4 対向基板

- 6 液晶

- 10、11 ガラス基板

- 12 ゲートバスライン

- 14 ドレインバスライン

- 16a、16b 画素電極

- 18 蓄積容量バスライン

- 19 蓄積容量電極

- 20 TFT

- 2 1 ドレイン電極

- 2 2 ソース電極

- 23 ゲート電極

- 2 5 コンタクトホール

- 28 動作半導体層

- 29 オーミックコンタクト層

- 3 0 絶縁膜

- 3 1 保護膜

- 3 3 制御容量電極

- 33a、33c 斜め延伸部

- 3 3 b 接続部

- 40、40R、40G、40B CF樹脂層

- 41 共通電極

- 42 線状突起

- 44、47 スリット

- 45、46 柱状スペーサ

- 4 8 ВМ

- 4 8 a 開口部

- 50、51 垂直配向膜

20

10

30

40

- 6 0 シール材

- 6 1 n <sup>+</sup> a S i 層

- 6 2 a S i 層

- 6 3 、 6 4 凸部

- 80 ゲートバスライン駆動回路

- 82 ドレインバスライン駆動回路

- 8 4 制御回路

- 86、87 偏光板

- 88 バックライトユニット

【図1】

【図2】

【図3】 【図4】

【図5】

【図7】

【図6】

[図8]

【図10】

【図12】

【図11】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図23】

【図22】

【図24】

## フロントページの続き

(72)発明者 田口 善久

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 長岡 謙一

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

(72)発明者 澤崎 学

神奈川県川崎市中原区上小田中4丁目1番1号 富士通ディスプレイテクノロジーズ株式会社内

## 審査官 藤田 都志行

(56)参考文献 特開2005-004212(JP,A)

特開2005-055896(JP,A)

(58)調査した分野(Int.CI., DB名)

G 0 2 F 1 / 1 3 6 8

G02F 1/1343

G02F 1/1337

G02F 1/1339