### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-146102 (P2011-146102A)

(43) 公開日 平成23年7月28日(2011.7.28)

(51) Int. Cl.

FL

テーマコード (参考)

G 1 1 C 11/4096

G 1 1 C 11/34 354R 5MO24

(2006, 01) G 1 1 C 11/401 (2006, 01)

G 1 1 C 11/34 371K

> 審査請求 未請求 請求項の数 21 OL (全 45 頁)

(21) 出願番号 (22) 出願日

特願2010-7239 (P2010-7239) 平成22年1月15日(2010.1.15) (71) 出願人 500174247

エルピーダメモリ株式会社

東京都中央区八重洲2-2-1

(74)代理人 100080816

弁理士 加藤 朝道

(72) 発明者 俣野 達哉

東京都中央区八重洲2-2-1 エルピー

ダメモリ株式会社内

Fターム(参考) 5M024 AA22 AA23 BB17 DD07 DD19

FF02 HH09 LL03 LL06 PP01

PP02 PP03 PP07

(54) 【発明の名称】半導体装置及びデータ処理システム

## (57)【要約】

【課題】複数の信号を並列に、かつ、最小限の数の伝送 線を用いて、低消費電力でノイズの影響を受けずに高速 に伝送する半導体装置を提供する。

【解決手段】複数の第1のドライバと複数のレシーバと の間で小振幅信号を伝送する第1の伝送線と、複数のレ シーバに共通に接続される基準信号を伝送する第2の伝 送線と、第1のドライバが小振幅信号を出力するインピ ーダンスより高インピーダンスで基準信号を出力する第 2のドライバとを備え、第2の伝送線を第1のドライバ の電源に接続された小振幅信号が有する第1と第2の電 位に対応する複数の電源線の間に配置し、複数の第1の 伝送線は、それぞれ第1と第2の電源線の間に配置され ることなく、互いに隣接して配置される。

【選択図】図3

#### 【特許請求の範囲】

### 【請求項1】

それぞれが、第1の動作電圧で動作し、小振幅なシングルエンドの入力信号を受け、前記入力信号をセンシングするセンシング機能を有する複数の第1のレシーバと、

それぞれが、前記第1の動作電圧よりも低い第2の動作電圧で動作し、前記小振幅な第 1の差電圧を有する前記入力信号を第1のインピーダンス値で出力する複数の第1のドライバと、

それぞれが、前記第1のドライバと前記第1のレシーバの距離を示す第1の長さを有し、前記入力信号を伝送する複数の第1の伝送線と、

前記複数の第1のレシーバがそれぞれ受ける共通な一つの基準信号と、

前記第2の動作電圧で動作し、前記基準信号を前記第1のインピーダンス値よりも高い第2のインピーダンス値で出力する第2のドライバと、

少なくとも前記第1の長さを有し、前記基準信号を伝送する第2の伝送線と、

前記第2の動作電圧に関連し、前記入力信号が有するハイ側電位とロウ側電位をそれぞれ生成し、前記複数の第1のドライバに供給し、それぞれ少なくとも前記第1の長さを有する第1と第2の電源線へ出力する第1と第2の内部電源生成回路と、を備え、

前記第2の伝送線は、前記第1と第2の電源線の間に前記複数の第1の伝送線を含むことなく配置され、

前記複数の第1の伝送線は、それぞれ前記第1と第2の電源線の間に配置されることなく、互いに隣接して配置される、ことを特徴とする半導体装置。

#### 【請求項2】

前記入力信号は、第1の論理レベルに対応する第1の電位と第2の論理レベルに対応する第2の電位で示される前記第1の差電圧を有し、

前記第1のレシーバが出力する電圧は、前記第1の差電圧よりも大きな前記第1の動作電圧に関連する第2の差電圧である、ことを特徴とする請求項1記載の半導体装置。

#### 【請求項3】

前記第1のレシーバは、前記入力信号と前記基準信号とがそれぞれ第1と第2の差動入力端子に接続される差動回路を含み、

前記第1のドライバは、互いに異なる導電型である第1と第2のトラジスタが直列に接続されるインバータである、ことを特徴とする請求項1又は2に記載の半導体装置。

#### 【請求項4】

前記第2のドライバは、前記第2の伝送線に接続された抵抗素子を少なくとも含む、ことを特徴とする請求項3記載の半導体装置。

## 【請求項5】

更に、互いに排他制御である複数の制御信号を備え、

前記複数の制御信号によってそれぞれ制御される複数の前記第1のドライバが、一つの前記第1のレシーバに対応する一つの前記第1の伝送線に選択的に接続される、ことを特徴とする請求項1記載の半導体装置。

## 【請求項6】

第1の領域に含まれる第1のノードと第2の領域に含まれる第2のノードとをそれぞれ 有する複数の第1の伝送線と、

前記第1の領域に含まれる第3のノードと前記第2の領域に含まれる第4のノードとを 有する一つの第2の伝送線と、

第1の電位と第2の電位との間で遷移する小振幅信号を第1のインピーダンスで生成し、それぞれ対応して接続する前記複数の第1の伝送線の第1と第2のノードのいずれか一方に出力し、前記第1と第2の領域のいずれか一方に配置される複数の第1のドライバと

前記第1の電位と第2の電位との中間電位の基準電圧信号を前記第1のインピーダンスより高い第2のインピーダンスで生成し、接続する前記第2の伝送線の前記複数の第1のドライバが出力する領域と同一の領域の前記第3と第4のいずれか一方のノードに出力し

10

20

30

40

、前記複数の第1のドライバと同一の領域に配置される第2のドライバと、

前記一つの第2の伝送線の前記複数の第1のドライバが出力する領域と反対側である領域の前記第3と第4のいずれか他方のノードに接続すると共に、前記複数の第1の伝送線の前記反対側である領域の前記第1と第2のノードのいずれか他方にそれぞれ対応して接続し、前記基準電圧信号と前記小振幅信号をそれぞれ受け、前記複数の第1のドライバと反対側に配置される複数の第1のレシーバと、

前記第1の電位を有し、第5のノードが前記第1の領域、第6のノードが前記第2の領域に含まれる第1の電源線と、

前記第2の電位を有し、第7のノードが前記第1の領域、第8のノードが前記第2の領域に含まれる第2の電源線と、を備え、

前記第2の伝送線は、それぞれ第1の方向に延在して配置される前記第1と第2の電源線との間に前記複数の第1の伝送線を含むことなく前記第1の方向に延在して配置され、

前記複数の第1の伝送線は、それぞれ前記第1と第2の電源線の間に配置されることなく、互いに隣接して前記第1の方向に延在して配置される、ことを特徴とする半導体装置

#### 【請求項7】

前記第1の電位と前記第2の電位を生成し、前記第2のドライバ及び前記複数の第1のドライバに供給する内部電源生成回路をさらに備える、ことを特徴とする請求項6記載の半導体装置。

## 【請求項8】

更に、前記第2の伝送線にそれぞれ隣接して前記第1の方向に延在する前記第1と第2の電源線と、前記第1と第2の電源線にそれぞれ対応する複数のその他の配線と、の間に、それぞれ前記半導体装置の活性化によっても不変な固定電位に接続された前記第1の方向に延在する複数の配線を更に備える、ことを特徴とする請求項6又は7記載の半導体装置。

#### 【請求項9】

前記複数のその他の配線は、前記複数の第 1 の伝送線である、ことを特徴とする請求項 8 記載の半導体装置。

## 【請求項10】

前記第1の電位は、前記第2の電位より高電位であり、

前記複数の第1のドライバは、それぞれ、

電源が前記第1の電位と第2の電位とに接続され、第1の信号に応答して前記小振幅信号を出力するメインドライバと、

電源が、前記第1の電位以上の電位である第3の電位と、前記2の電位以下の電位である第4の電位と、に接続され、前記第1の信号の論理レベルが変化しうるタイミングにおいて前記第1の信号に応答して出力し、前記第1の信号の論理レベルが変化しないタイミングでは出力ハイインピーダンスとなる補助ドライバと、を含む、ことを特徴とする請求項6乃至9いずれか1項記載の半導体装置。

## 【請求項11】

前記補助ドライバには、前記第1の信号に応答して出力するか、出力ハイインピーダンスとするかを制御する第2の信号が入力される、ことを特徴とする請求項10記載の半導体装置。

## 【請求項12】

前記小振幅信号は、前記第1の電位を第1の論理レベル、前記第2の電位を第2の論理レベルとするデジタル信号であって、

前記複数の第1のレシーバは、それぞれ、前記基準電圧信号の電圧レベルを基準に前記小振幅信号の論理レベルを判定する、ことを特徴とする請求項6乃至11いずれか1項記載の半導体装置。

### 【請求項13】

前記複数の第1のレシーバは、それぞれ、前記小振幅信号と前記基準電圧信号とを差動

10

20

30

40

入力とする差動回路を含み、

前記第1のドライバは、前記第1の電位に接続された第1導電型の出力トランジスタと、前記第2の電位に接続された第2導電型の出力トランジスタと、を含み、

前記第2のドライバは、前記第1の電位と第2の電位とを分圧する抵抗素子を含む、ことを特徴とする請求項6万至12Nずれか1項記載の半導体装置。

### 【請求項14】

前記第1の電源線及び第2の電源線は、前記第2伝送線の全長に渡って前記第2伝送線に隣接して配線されている、ことを特徴とする請求項6乃至13いずれか1項記載の半導体装置。

## 【請求項15】

前記第2伝送線と他の配線との配線間容量は、前記第1の電源線との配線間容量、及び第2の電源線との配線間容量が最も大きくなるように配線されている、ことを特徴とする請求項6乃至14いずれか1項記載の半導体装置。

#### 【請求項16】

前記複数の第1のドライバがそれぞれ出力する小振幅信号を第1の小振幅信号としたときに、それぞれ、前記複数の第1のレシーバ側に配置され、それぞれ前記第1の電位と前記第2の電位との間で遷移する第2の小振幅信号を低インピーダンスで前記複数の第1の伝送線に出力する複数の第3のドライバと、

前記複数の第1のドライバ側に配置され、前記第1の伝送線及び第2の伝送線に接続された複数の第2のレシーバと、

前記複数の第1のレシーバ側に配置され、前記第2の伝送線へ第1の基準電圧信号と同電位の第2の基準電圧信号を前記第3のドライバより高インピーダンスで出力する第4のドライバと、をさらに備え、

前記第1の電源線及び第2の電源線は、前記第2の伝送線を両側から挟んで、前記第4のドライバ近傍から前記複数の第2のレシーバ近傍まで配線され、

前記複数の第3のトライバ及び第4のドライバを出力ハイインピーダンスとして、前記複数の第1のドライバからそれぞれ前記第1の小振幅信号を前記第1の伝送線に出力し、前記第2のドライバから前記第1の基準電圧信号を前記第2の伝送線に出力し、前記複数の第1のレシーバがそれぞれ前記第1の小振幅信号及び前記第1の基準電圧信号を受信する第1の動作モードと、

前記複数の第1のドライバ及び第2のドライバを出力ハイインピーダンスとして、前記複数の第3のドライバからそれぞれ前記第2の小振幅信号を前記第1の伝送線に出力し、前記第4のドライバから前記第2の基準電圧信号を前記第2の伝送線に出力し、前記複数の第2のレシーバがそれぞれ前記第2の小振幅信号及び前記第2の基準電圧信号を受信する第2の動作モードと、

を有する、ことを特徴とする請求項6乃至15いずれか1項記載の半導体装置。

#### 【請求項17】

前記内部電源生成回路は、前記複数の第1のドライバ側に設けられ、前記第1の電位と前記第2の電位を生成する第1の前記内部電源生成回路と、前記複数の第1のレシーバ側に設けられ、前記第1の電位と前記第2の電位を生成する第2の前記内部電源生成回路と、を含み、

前記第1の電源線及び第2の電源線は、前記第1の動作モードにおいて前記第2の内部電源生成回路から電気的に切り離されて前記第1の内部電源生成回路に電気的に接続され、前記第2の動作モードにおいて前記第1の内部電源生成回路から電気的に切り離されて前記第2の内部電源生成回路に電気的に接続される、ことを特徴とする請求項16記載の半導体装置。

#### 【請求項18】

前記複数の第1のレシーバと、前記複数の第3のドライバと、前記第4のドライバと、を第1ブロックとして、

前記複数の第2のレシーバと、前記複数の第1のドライバと、前記第2のドライバと、

10

20

30

40

を第2ブロックとしたときに、

前記複数の第1の伝送線及び第2の伝送線に接続され、前記第1ブロックとの間でデータの伝送を行う前記第2ブロックを複数備え、

前記複数の第2ブロックから前記第1ブロックへデータの伝送を行うときに、前記複数の第2ブロックのうち、選択された1つの第2ブロックに含まれる前記複数の第1のドライバ及び第2のドライバのみが導通し、選択されない第2のブロックに含まれる前記複数の第1のドライバ及び第2のドライバは出力ハイインピーダンスとなる、ことを特徴とする請求項16又は17記載の半導体装置。

### 【請求項19】

前記半導体装置が半導体記憶装置であって、

前記複数の第2ブロックにそれぞれ対応して設けられた複数のメモリセルアレイと、

前記第1ブロックに対応して設けられたデータ入出力端子と、をさらに備え、

ライト時には、前記データ入出力端子から入力したライトデータを前記第1ブロックから前記複数の第1の伝送線を介して複数の第2のブロックのうち、選択された第2のブロックに伝送し、さらに前記選択された第2のブロックから対応するメモリセルアレイヘライトし、

リード時には、選択されたメモリセルアレイから対応する第2のブロックにデータを読み出し、さらに、その読み出したデータを前記複数の第1の伝送線を介して前記第1のブロックに転送し、前記第1のブロックから前記データ入出力端子へ出力する、ことを特徴とする請求項18記載の半導体装置。

#### 【請求項20】

前記第1ブロックは、前記複数の第1の伝送線から並列に入力したリードデータを直列データに変換して前記データ入出力端子から出力する並直列変換回路と、前記データ入出力端子から直列に入力したライトデータを並列データに変換して前記複数の第1の伝送線へ出力する直並列変換回路と、を備る、ことを特徴とする請求項19記載の半導体装置。

#### 【請求項21】

第1の半導体装置と、

第2の半導体装置と、

前記第1と前記第2の半導体装置との間を接続するシステムバスと、を備え、

前記第1の半導体装置は、

複数の第1の伝送線と、

一つの第2の伝送線と、

第1の電位と第2の電位との間で遷移する小振幅信号を第1のインピーダンスで生成し、それぞれ対応して接続する前記複数の第1の伝送線の一端に出力する第1の領域に配置された複数の第1のドライバと、

前記第1の電位と第2の電位との中間電位の基準電圧信号を前記第1のインピーダンスより高い第2のインピーダンスで生成し、接続する前記第2の伝送線の一端に出力する前記第1の領域に配置された第2のドライバと、

前記一つの第2の伝送線の他端に接続すると共に、前記複数の第1の伝送線の他端にそれぞれ対応して接続し、前記基準電圧信号と前記小振幅信号をそれぞれ受ける第2の領域に配置された複数の第1のレシーバと、

前記第1の電位を有し、一端が前記第1の領域、他端が前記第2の領域に含まれる第1 の電源線と、

前記第2の電位を有し、一端が前記第1の領域、他端が前記第2の領域に含まれる第2の電源線と、を備え、

前記第2の伝送線は、前記第1と第2の電源線との間に前記複数の第1の伝送線を含むことなく配置され、

前記複数の第1の伝送線は、それぞれ前記第1と第2の電源線の間に配置されることなく、互いに隣接して配置され、

前記第2の半導体装置は、前記第1の半導体装置からの要求に応答して、前記データ記

10

20

30

40

憶部に格納されたデータを前記複数の第1のドライバと、前記複数の第1の伝送線と、前記複数の第1のレシーバと、を介して前記システムバスに出力する、ことを特徴とするデータ処理システム。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、半導体装置及びデータ処理システムに関する。特に、内部に複数ビットのデータを並列に伝送する複数の伝送線を備えた半導体装置、及びその半導体装置を用いるデータ処理システムに関する。

【背景技術】

[0002]

半導体記憶装置などの半導体装置では、内部回路と外部接続端子との間で並列に複数ビットのデータの伝送が行われる。このデータ伝送では、高速に、かつ、低消費電力で、かつ、ノイズにより誤動作することなく、かつ、できるだけ配線等の本数を増やさずにデータを伝送することが要求される。このデータの伝送の方法としては、シングルエンドの信号を用いる方法と、差動信号を用いる方法が考えられる。シングルエンドの信号を用いた場合には、ノイズによる誤動作を避けるため、振幅を大きくする必要があり、充放電による消費電力が増加すると共に、データの伝送が遅くなる。これに対して差動信号をデータの伝送に用いれば、ノイズの影響が受けにくくなるため、伝送信号を小振幅にすることが可能となり、高速なデータの伝送も可能である。しかし、差動信号を伝送に用いた場合には、1ビットのデータの伝送に2本の配線が必要となり、並列にデータを転送するビット数が多い場合には、配線面積が大きくなる。

[0003]

特許文献 1 には、光ディスク装置のピックアップから提供されるRF信号に混入するノイズを除去するため、RF信号を伝送する信号線とリファレンス電圧を伝送する信号を接近して配線し、信号線とリファレンス信号を差動アンプに差動信号として入力している。特許文献 1 によれば、信号線とリファレンス電圧信号を接近して配線することにより、ノイズが混入しても差動アンプに同相で入力するので互いに打ち消しあうことが記載されている。

【先行技術文献】

【特許文献】

[0004]

【特許文献 1 】特開 2 0 0 2 - 0 7 4 6 6 3 号公報

【発明の概要】

【発明が解決しようとする課題】

[0005]

以下の分析は本発明により与えられる。信号線に対し、差動アンプのリファレンス電位を信号線駆動ドライバとは遠い別の場所で発生させた場合、信号線に対し発生する基板などからのコモンノイズ及び信号線駆動時に発生する電源ノイズの影響を受けないため、信号線の変動分がそのまま差動アンプの信号損失分となってしまう。

[0006]

また、信号線とリファレンス信号を並列に走らせて同相のコモンノイズがのるようにした場合、電源ノイズも同相で発生させるためには、信号線ドライバとリファレンス信号ドライバを同じ場所からの同一電源で駆動しかつ信号線ドライバとリファレンス信号ドライバの出力インピーダンスを等しくする必要がある。信号線ドライバとリファレンス信号ドライバの出力インピーダンスが異なる場合には、信号線とリファレンス線を近接して配置しても同相ノイズの影響の受け方が互いに異なるため、同相ノイズを十分に除去することはできない。そのため、信号を高速に伝送するためには、信号線ドライバの出力インピーダンスを小さくする必要がある。しかし、リファレンス信号ドライバの出力インピーダンスを小さくすると、消費電力

10

20

30

40

20

30

40

50

が増大する。たとえば、信号線ドライバをCMOSで構成すれば、信号の変化がない限り、電流が流れないようにできる。しかし、リファレンス信号を常時、低インピータダンスで中間電位を出力するためには、常時電流をリファレンス信号ドライバに流す必要が生じる。

## 【課題を解決するための手段】

### [0007]

#### [ 0 0 0 8 ]

本発明の第2の側面による半導体装置は、第1の領域に含まれる第1のノードと第2の 領域に含まれる第2のノードとをそれぞれ有する複数の第1の伝送線と、前記第1の領域 に含まれる第3のノードと前記第2の領域に含まれる第4のノードとを有する一つの第2 の 伝 送 線 と 、 第 1 の 電 位 と 第 2 の 電 位 と の 間 で 遷 移 す る 小 振 幅 信 号 を 第 1 の イ ン ピ ー ダ ン スで生成しそれぞれ対応して接続する前記複数の第1の伝送線の第1と第2のノードのい ず れ か 一 方 に 出 力 し 前 記 第 1 と 第 2 の 領 域 の い ず れ か 一 方 に 配 置 さ れ る 複 数 の 第 1 の ド ラ イバと、前記第1の電位と第2の電位との中間電位の基準電圧信号を前記第1のインピー ダンスより高い第2のインピーダンスで生成し接続する前記第2の伝送線の前記複数の第 1 のドライバが出力する領域と同一の領域の前記第 3 と第 4 のいずれか一方のノードに出 力 し 前 記 複 数 の 第 1 の ド ラ イ バ と 同 一 の 領 域 に 配 置 さ れ る 第 2 の ド ラ イ バ と 、 前 記 一 つ の 第 2 の 伝 送 線 の 前 記 複 数 の 第 1 の ド ラ イ バ が 出 力 す る 領 域 と 反 対 側 で あ る 領 域 の 前 記 第 3 と第4のいずれか他方のノードに接続すると共に前記複数の第1の伝送線の前記反対側で ある領域の前記第 1 と第 2 のノードのいずれか他方にそれぞれ対応して接続し前記基準電 圧信号と前記小振幅信号をそれぞれ受け前記複数の第1のドライバと反対側に配置される 複 数 の 第 1 の レ シ ー バ と 、 前 記 第 1 の 電 位 を 有 し 、 第 5 の ノ ー ド が 前 記 第 1 の 領 域 、 第 6 のノードが前記第2の領域に含まれる第1の電源線と、前記第2の電位を有し、第7のノ ードが前記第1の領域、第8のノードが前記第2の領域に含まれる第2の電源線と、を備 え、前記第 2 の 伝 送 線 は、 そ れ ぞ れ 第 1 の 方 向 に 延 在 し て 配 置 さ れ る 前 記 第 1 と 第 2 の 電 源 線 と の 間 に 前 記 複 数 の 第 1 の 伝 送 線 を 含 む こ と な く 前 記 第 1 の 方 向 に 延 在 し て 配 置 さ れ 、 前 記 複 数 の 第 1 の 伝 送 線 は 、 そ れ ぞ れ 前 記 第 1 と 第 2 の 電 源 線 の 間 に 配 置 さ れ る こ と な く、 互 い に 隣 接 し て 前 記 第 1 の 方 向 に 延 在 し て 配 置 さ れ る 。

# [0009]

本発明の第3の側面によるデータ処理システムは、第1の半導体装置と、第2の半導体装置と、前記第1と前記第2の半導体装置との間を接続するシステムバスと、を備え、前記第1の半導体装置は、複数の第1の伝送線と、一つの第2の伝送線と、第1の電位と第2の電位との間で遷移する小振幅信号を第1のインピーダンスで生成しそれぞれ対応して接続する前記複数の第1の伝送線の一端に出力する第1の領域に配置された複数の第1のドライバと、前記第1の電位と第2の電位との中間電位の基準電圧信号を前記第1のイン

ピーダンスより高い第2のインピーダンスで生成し、接続する前記第2の伝送線の一端に出力する前記第1の領域に配置された第2のドライバと、前記一つの第2の伝送線の他端に接続すると共に、前記複数の第1の伝送線の他端にそれぞれ対応して接続し、前記基準電圧信号と前記小振幅信号をそれぞれ受ける第2の領域に配置された複数の第1のレシーバと、前記第1の電位を有し、一端が前記第1の領域、他端が前記第2の領域に含まれる第2の電源線と、を備え、前記第2の伝送線は、前記第1と第2の電源線との電流に前記第1の伝送線を含むことなく配置され、前記第1の伝送線は、前記第1の伝送線を含むことなく、互いに隣接して配置され、前記第1と第2の電源線の間に配置されることなく、互いに隣接して配置され、前記第1の半導体装置からの要求に応答して、前記データ記憶部にの半導体装置は、前記第1の半導体装置からの要求に応答して、前記データ記憶部の第1のレシーバと、を介して前記システムバスに出力する。

10

20

30

40

#### 【発明の効果】

## [0010]

本発明によれば、第1の電源線、及び/又は、第2の電源線の電位が変動すると、第2の伝送線の電位が第1の電源線、及び/又は、第2の電源線の電位の変動につれて、変動するため、第2のドライバのインピーダンスが高くとも電源ノイズの影響を受けにくい。

#### [0011]

したがって、伝送信号の振幅を小さくすることができ、並列に伝送するビット数の増加による配線の数の増加を抑制しつつ、高速な信号の伝送や低消費電力化も実現できる。

【図面の簡単な説明】

[0012]

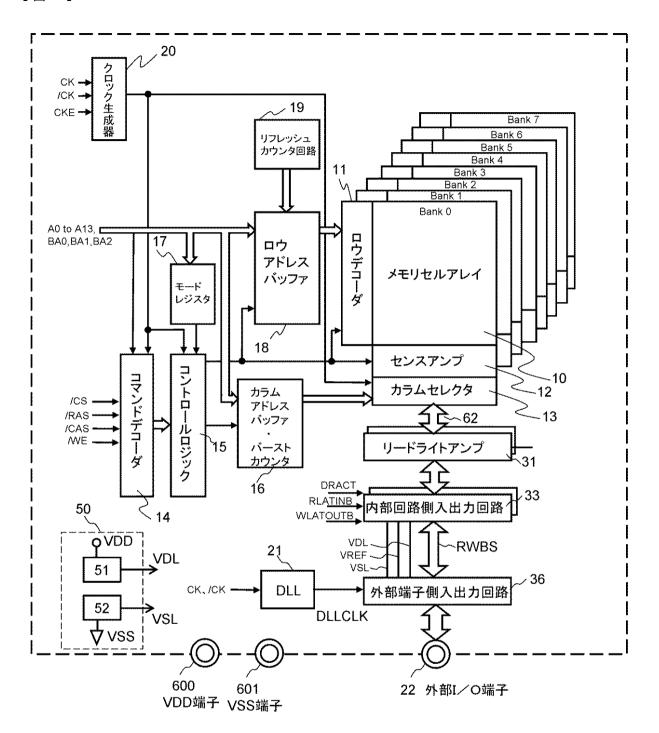

- 【図1】本発明の実施例1による半導体装置全体のブロック図である。

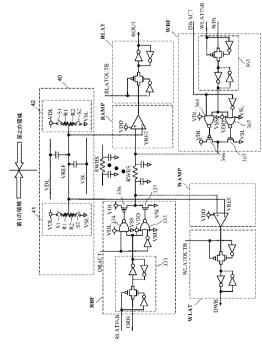

- 【 図 2 】実施例 1 による半導体装置におけるメモリセルアレイとデータ入出力端子とのインタフェース部分全体のブロック図である。

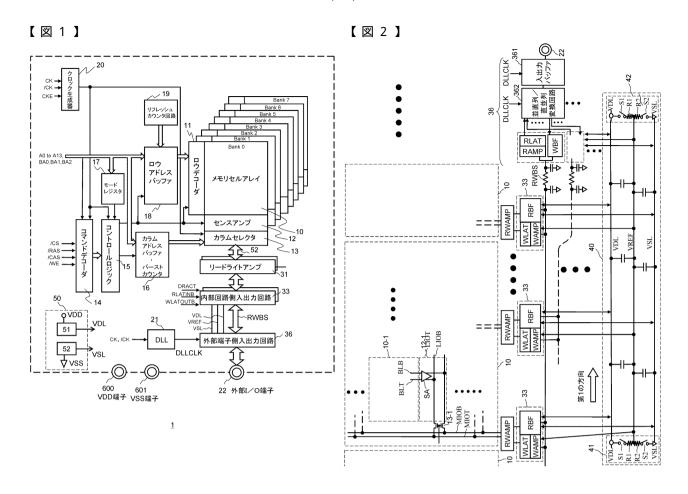

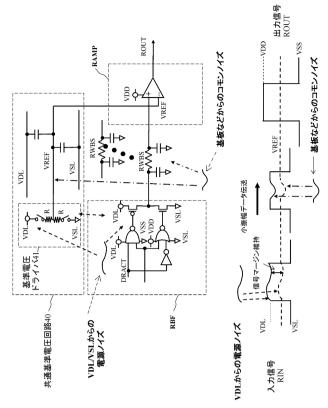

- 【図3】実施例1による半導体装置における内部回路側と外部端子側のデータ伝送回路の回路ブロック図である。

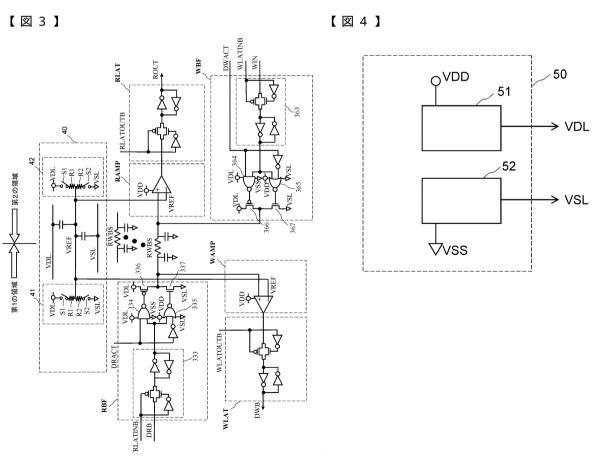

- 【図4】実施例1における内部電源生成回路のブロック図である。

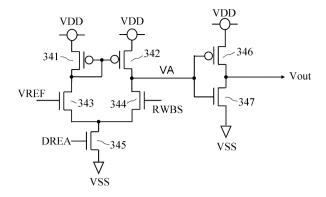

- 【図5】実施例1におけるデータレシーバの回路ブロック図である。

- 【図6】実施例1において好ましいレイアウト配置を説明する図面である。

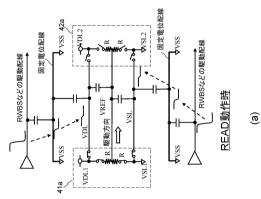

- 【図7】実施例1において、(a)は内部回路側から外部端子側にデータを出力(リード動作)するときのドライバ回路の状態を説明する図であり、(b)は外部端子側から内部回路側にデータを入力(ライト動作)するときのドライバ回路の状態を説明する図である

- 【図8】実施例1において、(a)はリード動作時の基準電圧ドライバの状態を説明する図であり、(b)はライト動作時の基準電圧ドライバの状態を説明する図である。

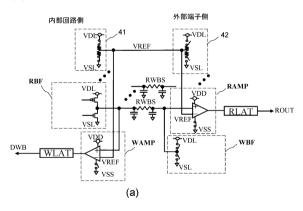

- 【図9】実施例2において、(a)はリード動作時の基準電圧ドライバの状態を説明する図であり、(b)はライト動作時の基準電圧ドライバの状態を説明する図である。

- 【図10】実施例3において、(a)リード動作時の内部電源線及び基準電圧伝送線の状態と、(a)ライト動作時の内部電源線及び基準電圧伝送線の状態と、を説明する図である。

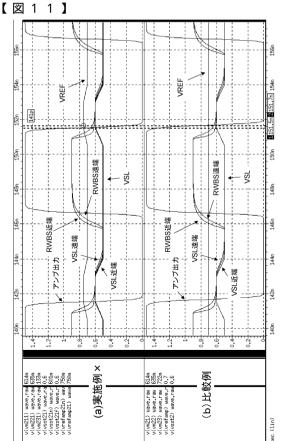

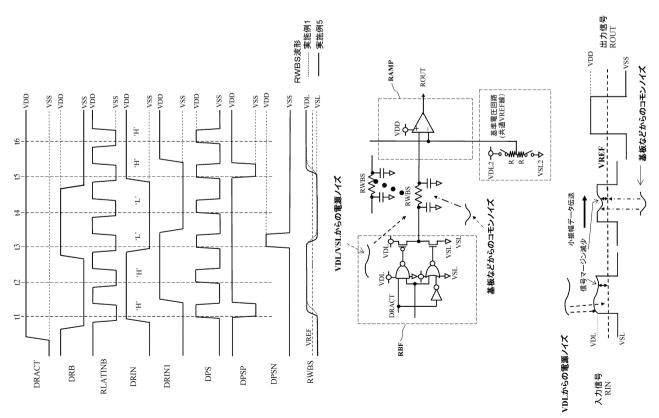

- 【図11】内部電源VSLが変動した場合の(a)実施例2における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。

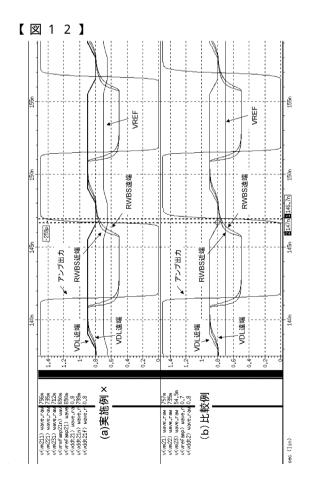

- 【図12】内部電源VDLが変動した場合の(a)実施例2における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。

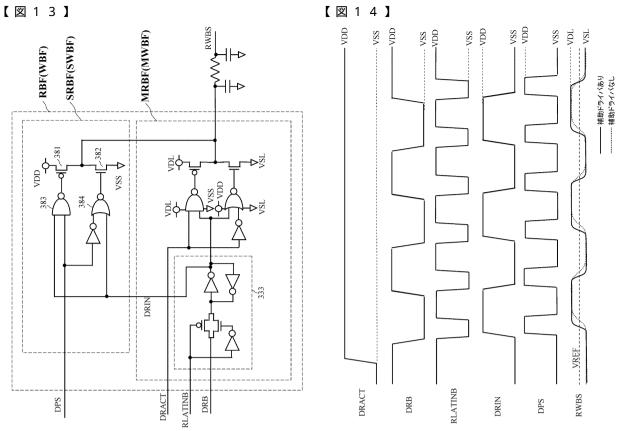

- 【図13】実施例4におけるデータバッファの回路ブロック図である。

- 【図14】実施例4におけるデータバッファの動作波形図である。

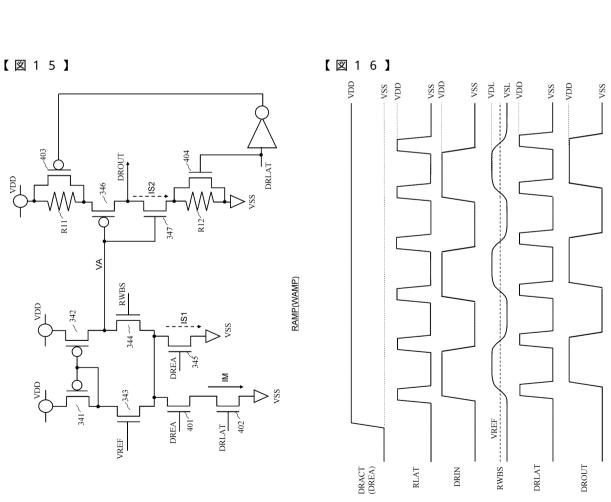

- 【図15】実施例4におけるデータレシーバの回路ブロック図である。

- 【図16】実施例4におけるデータレシーバの動作波形図である。

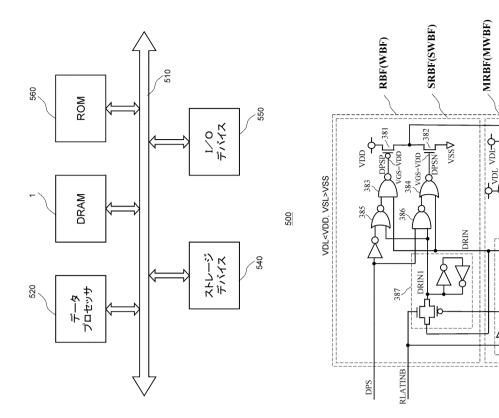

- 【図17】データ処理システムの実施例のブロック図である。

- 【図18】実施例5によるデータバッファの回路ブロック図である。

- 【図19】実施例5によるデータバッファの動作波形図である。

- 【図20】実施例1に対する比較例の動作を説明する図である。

- 【発明を実施するための形態】

- [0013]

本発明の代表的な実施形態によれば、複数の第1の伝送線により小振幅信号を並列に伝送するとともに、第2の伝送線により共通の基準信号を伝送するので、差動信号を伝送するより伝送線の数を減らすことができる。また、第1のレシーバは基準信号に基づいて小振幅信号のレベルを判定することができるので、小振幅信号の振幅を小さくすることができ、高速、かつ、低消費電力で小振幅信号を伝送することができる。

[0014]

また、小振幅信号を出力する第1のドライバの第1のインピーダンス値より基準信号を出力する第2のドライバの第2のインピーダンス値を高くすることにより、小振幅信号を高速に伝送すると共に、第2のドライバが基準信号を中間電圧にしたまま待機したとして第2のドライバの消費電力を抑制することができる。

[0015]

さらに、基準信号を伝送する第2の伝送線が、小振幅信号の電位である第1の電位と第2の電位にそれぞれ接続された第1の電源線と第2の電源線との間に配置され、かつ、第1の伝送線は、第1の電源線と第2電源線とに隣接されることなく配置されている。第1の伝送線を伝送する小振幅信号は、第1のドライバが相対的に低インピーダンスなので、第1の電源線及び/又は第2の電源線の電位変動に対してすばやく追従する。一方、第2の伝送線を伝送する基準信号は、第2のドライバが相対的に高インピーダンスなので、第1の電源線及び/又は第2の電源線に電位変動があっても、すぐには、追従しない。し、第2の伝送線を第1の電源線と第2の電源線の間に配置することにより、配線間容量によって、第2の伝送線を伝送する基準信号も、第1の伝送線を伝送する小振幅信号と同様に、第1の電源線及び/又は第2の電源線の電位変動に対して追従するようにすることができる。したがって、第1の電源線の第1の電位、及び/又は、第2の電源線の第2の電位が、電源ノイズ等により、影響を受けたとしても、その影響を抑制することができる

[0016]

上記効果は、第2の伝送線と第1の電源線、及び、第2の伝送線と第2の電源線の配線間容量を増やし、この配線間容量に対して、各第1の伝送線と第1の電源線、及び、各第1の伝送線と第2の電源線の配線間容量を相対的に小さくすることにより達成できる。より好ましくは、第2の伝送線と第1の電源線の配線間容量と、第2の伝送線と第2の電源線の配線間容量の値は、同等であることが望ましい。

[0017]

以下、実施例について、図面を参照して詳しく説明する。

【実施例1】

[0018]

図1は、実施例1の半導体装置1全体のブロック図である。図1の半導体装置1は、DDR SDRAM(Double Data Rate Synchronous DRAM)等の同期式のDRAMである。図1において、10はメモリセルアレイ、11はロウアドレスをデコードし選択されたワード線(図示せず)を駆動するロウデコーダ、12はメモリセルアレイの中から選択したメモリセル(図示せず)のデータをセンシングするセンスアンプ、13はセンスアンプ12がセンシングした複数のデータのうちカラムアドレスに基づいて選択したデータをメモリセルアレイ10の外へ出力するカラムセレクタである。半導体記憶装置1には、Bank0~Bank7の8つのメモリセルアレイ10が設けられており、ロウデコーダ11、センスアンプ12、カラムセレクタ13もメモリセルアレイ毎に設けられている。

10

20

30

40

20

30

40

50

#### [0019]

クロック生成器20は、外部から与えられる非反転クロック信号CK、反転クロック信 号 / CK、クロックイネーブル信号CKEから内部動作クロックを生成する。コマンドデ コーダ14は、外部から与えられたチップセレクト信号/CS、ロウアドレスストローブ 信号/RAS、カラムアドレスストローブ信号/CAS、ライトイネーブル信号/WEを デ コ ー ド し て 外 部 の メ モ リ コ ン ト ロ ー ラ 等 か ら 半 導 体 装 置 1 に 与 え ら れ た リ ー ド 、 ラ イ ト 等 の コ マ ン ド を 解 読 す る 。 コ ン ト ロ ー ル ロ ジ ッ ク 1 5 は 、 コ マ ン ド デ コ ー ダ 1 4 が 解 読 し たコマンド、モードレジスタ17の状態に基づいて、クロック生成器20から与えられた クロックに同期して半導体装置1の各部へコマンドを実行するために必要な信号を出力す る。モードレジスタ17、カラムアドレスバッファ・バーストカウンタ16、ロウアドレ スバッファ18には、それぞれ外部アドレス入力端子A0~A13、バンクアドレス入力 端子BA0、BA1、BA2が内部アドレスバスを介して接続される。モードレジスタ1 7は、モードレジスタ設定コマンドが与えられたとき、内部アドレスバスから与えられた データをレジスタに設定する。ロウアドレスバッファ 1 8 は、バンクアクティブ A C T コ マンドが与えられたとき、ロウアドレスをラッチしロウデコーダ11へ出力する。カラム アドレスバッファ・バーストカウンタ16は、リードコマンド、ライトコマンドが与えら れたとき、カラムアドレスをラッチし、デコードしてカラムセレクタ13を選択する。ま た、バーストリード、バーストライトコマンドが与えられたときは、指定されたバースト 長に基づいてカラムアドレスをカウントする。リフレッシュカウンタ回路19は、リフレ ッシュアドレスのカウントアップを行う。また、DLL21は、外部クロック端子CK、 / C K から与えられた外部クロック信号に基づいて、外部クロック信号と位相の揃ったク ロック信号を生成し、外部I/O端子22からのデータ入出力のタイミングを制御する。

[0020]

また、リードライトアンプ 3 1、内部回路側入出力回路 3 3 は、Bank0~Bank7の8つのメモリセルアレイ 1 0 毎にメモリセルアレイ 1 0 の外に設けられる。リードライトアンプ 3 1 は、リードコマンド実行時には、センスアンプ 1 2、カラムセレクタ 1 3、 I / O線 5 2 を介してメモリセルアレイ 1 0 の外に読み出されたメモリセルのデータをセンシングする。また、ライトコマンド実行時には、外部 I / O端子 2 2 から外部端子側入出力回路 3 6、リードライトデータバスRWBS、内部回路側入出力回路 3 3 を経由して入力されたライトデータをメモリセルアレイ 1 0 に対して書込みを行う。

[0021]

内部回路側入出力回路33は、リード動作時には、リードライトアンプがセンシングしたデータをリードライトデータバスRWBSへ出力する。また、ライト動作時には、リードライトデータバスRWBSからライトデータを取り込み、リードライトアンプへライトデータとして送る。

[0022]

リードライトデータバス(第1の伝送線)RWBSは、各メモリセルアレイ10と各外部I/O端子22との間を接続する並列データバスである。後で詳しく説明するように、このリードライトデータバスRWBSは、小振幅の信号を伝送するバスであり、小振幅信号のハイレベル、ロウレベルの判定基準となる基準電圧信号(第2の伝送線)VREFが、小振幅信号の電源となる内部電源線VDLとVSLに挟まれて内部回路側入出力回路33と外部端子側入出力回路36との間に配線されている。なお、リードライトデータバスRWBUSが複数のビットのバスであるに対して、基準電圧信号VREFは、1本の信号線(第2の伝送線)である。内部電源線VDLとVSLは、内部電源VDL、VSLを生成する内部電源生成回路50で生成される。一例として、内部電源線VDLとVSLは、半導体装置1の外部端子である高電位側のVDD端子600、低電位側のVSS601から供給される。

[0023]

外部端子側入出力回路36は、半導体装置1の外部端子である各外部I/O端子22(図1には1端子のみ図示)に対応して設けられており、リード動作時には、リードライト

20

30

40

50

データバスから並列に入力したリードデータをDLL21が出力するDLLCLKに同期して直列データに変換し、外部I/O端子22から出力する。また、ライト動作時には、DLL21が出力するDLLCLKに同期して外部I/O端子22から取り込んだライトデータを並列データに変換し、リードライトデータバスRWBSへ出力する。

## [0024]

ライトデータとリードデータの入出力端子である外部 I / O端子 2 2 は、図1では代表して1端子しか記載していないが、DDR等の同期式DRAMでは、一般的に、4端子から16端子である。ライト動作時には、4~16本の外部 I / O端子 2 2 から直列に入力されたデータは、外部端子側入出力回路 3 6 により、8~128ビットの並列データに変換され、リードライトデータバスRWBSを介して該当するバンクの内部側入出力回路に転送され、メモリセルアレイ10へ書込まれる。リード動作時には、8~128ビットの並列データとしてリードライトデータバスRWBSを介して外部端子側入出力回路に読み出されたライトデータは、外部端子側入出力回路 3 6 により直列データに変換され、4~16本の外部 I / O端子から出力される。なお、リードライトデータバスRWBSのビット数は、4本の外部 I / O端子から入出力するデータを2ビット並列に転送する場合は、8ビットであり、16本の各外部 I / O端子からそれぞれバースト入出力する8ビットデータを並列に転送する場合は、128ビットである。

## [0025]

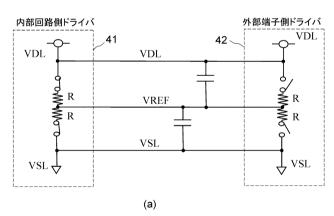

図2は、実施例1による半導体装置におけるメモリセルアレイ10と外部I/O端子22とのインタフェース部分全体のブロック図である。ただし、図2では、8個のメモリセルアレイ10のうち、3個のメモリセルアレイのみ図示し、他のメモリセルアレイ10の記載は省略している。また、図2では、4~16端子の外部I/O端子22のうち、1端子のみを図示し、他の外部I/O端子22の図示も省略している。さらに、図2では、基準電圧信号VREFの伝送に関連する第2の伝送線に関する記載は省略している。

#### [0026]

図2において、メモリセルアレイ10は、1バンクのメモリセルアレイが配置される領域を示している。1バンクのメモリセルアレイ10は、複数の部分領域10・1に分かれて配置され、部分領域10・1毎にセンスアンプSAをまとめて配置したセンスアンプ列12・1が設けられている。ビット線BLT、BLTBは、センスアンプSAを介してエーカルIO線LIOT、LIOBに接続されている。さらに、ローカルIO線LIOT、LIOBに接続されている。さらに、ローカルIO線LIOT、LIOBに接続されている。は、リードライトゲート13・1を介してメインIO線MIOT、MIOBに接され、メインIO線MIOT、MIOBは、リードライトアンプRWAMP(図1の31に相当)へと接続されている。なお、1バンクのメモリセルアレイ10には、多数のコンプ列12・1とローカルIO線LIOT、LIOBがそれぞれ設けられている。また、図2では、メインIO線MIOT、MIOBは1対しか記載していないが各メモリIO線 MIOT、MIOBが設けられ、各メモリIO線 MIOT、MIOBに対応して複数のリードライトアンプRWAMPが設けられている

#### [0027]

内部回路側入出力回路33は、リードデータバッファRBFと、ライトデータラッチWLATと、ライトデータレシーバWAMPを含んで構成される。リードデータバッファRBFは、リードライトアンプRWAMPから読み出したリードデータを一時的に保存するラッチ回路と、ラッチ回路が保持するデータをリードライトデータバスRWBSへ小振幅信号として出力するドライブ回路を備えている。ライトデータアンプ(第2のレシーバ)WAMPは、ライトコマンド実行時にリードライトデータバスRWBSの小振幅信号をセンシングする。なお、ライトデータアンプWAMPには、基準電圧信号VREFも接続されるが、図2では、記載を省略している。ライトデータラッチWLATは、ライトコマンド実行時にライトデータアンプWAMPがセンシングしたデータをメモリセルアレイ10に書き込むまで一時的に保持するラッチである。なお、内部回路側入出力回路33は、各

20

30

40

50

リードライトアンプRWAMPに対応してバンク毎に複数設けられる。

### [0028]

リードライトデータバスRWBSは、8~128本の伝送線からなる双方向のバスであり、各メモリセルアレイ10に対応して設けられた複数の内部回路側入出力回路33と、各外部I/O端子22に対応して設けられた複数の外部回路側入出力回路36と、を接続する。1本のリードライトデータバスRWBSには、バンク毎に複数の内部回路側入出力回路33が接続される。また、リードライトデータバスRWBSは、各バンクのメモリセルアレイ10近傍に設けられる内部回路側入出力回路33から外部I/O端子22近傍に設けられる外部端子側入出力回路36まで配線されるので、リードライトデータバスRWBSの配線の長さは、半導体装置1の半導体チップ長辺の長さに相当する程度の長さを備えたバスである。複数のメモリセルアレイ10は、互いに排他的に一つのリードライトデータバスRWBSをアクセス(リード又はライト)する。

#### [0029]

外部端子側入出力回路 3 6 は、外部 I / O 端子 2 2 毎に設けられ、リードデータレシーバ(第 1 のレシーバ) R A M P、リードデータラッチ R L A T、ライトデータバッファW B F を含むリードライトデータバスインタフェース部と、並直列 / 直並列変換回路 3 6 2 と、入出力バッファ 3 6 1 を備えている。

## [0030]

リードデータレシーバ(第1のレシーバ)RAMPは、リードコマンド実行時にリードライトデータバスRWBSの小振幅信号をセンシングする。なお、リードデータレシーバRAMPには、基準電圧信号VREFも接続されるが、図2では、記載を省略している。リードデータラッチRLATは、リードコマンド実行時にリードデータレシーバRAMPがセンシングしたデータを一時的に保持するラッチである。ライトデータバッファWBFは、並直列/直並列変換回路362が直並列変換したデータを一時的に保存するラッチ回路と、ラッチ回路が保持するデータをリードライトデータバスRWBSへ小振幅信号として出力するドライブ回路を備えている。

## [ 0 0 3 1 ]

共通基準電圧回路40に含まれる第2の伝送線VREF、高電位側内部電源VDL及び低電位側内部電源VSLは、複数のリードライトデータバスRWBSのグループに隣接して併走し、複数の内部回路側入出力回路33及びリードデータレシーバRAMPに供給する。詳細は、図3で後述する。尚、複数のメモリセルアレイ10毎に、または複数の内部回路側入出力回路33毎に、それぞれ対応する複数の内部回路側のドライバを有することが望ましい。

## [0032]

並直列/直並列変換回路362は、リードコマンド実行時に、リードデータラッチRLATに一時的に保持するデータをDLLCLKに同期して並直列変換し、入出力バッファへ出力する。また、ライトコマンド実行時には、入出力バッファ361から入力したデータをDLLCLKに同期して並列データに変換し、ライトデータバッファWBFのラッチ回路へ格納する。

#### [0033]

入出力バッファ361は、リードコマンド実行時には、並直列/直並列変換回路362により直列データに変換されたデータを外部I/O端子22から出力し、ライトコマンド実行時には、外部I/O端子22から入力されるデータを取り込み、並直列/直並列変換回路362へ送る。なお、入出力バッファ361が外部I/O端子22から入出力するデータ信号に同期して、DQS端子(図示せず)からデータストローブ信号が入出力される

#### [0034]

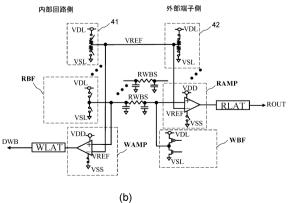

図3は、実施例1による半導体装置1におけるリードライトデータバスRWBSを伝送する小振幅信号の伝送に関連する内部回路側(第1の領域)と外部端子側(第2の領域)のデータ伝送回路の回路ブロック図である。なお、図3に記載されている各回路のうち、

20

30

40

50

電源として小振幅信号の高電位側電源VDL、低電位側電源VSLが電源として供給される回路については、電源をVDL、VSLと明記しているが、電源VDD、電源VSSが供給される回路の電源は記載を一部省略している。従って、図3に記載されている回路のうち、電源系が明記されていない回路の電源には、VDDとVSSが供給されている。なお、高電位側電源VDLの電圧は、電源VDDの電圧以下の電圧であり、半導体装置1の内部で生成する内部電源である。

#### [0035]

図3において、リードデータバッファRBFは、ラッチ回路333と、NAND回路334とNOR回路335を含むプリバッファ回路と、PチャンネルMOSトランジスタ337を含むバッファ回路により構成されるアチロ路333は、ラッチ信号RLATINBがロウレベルのときにリードライトアNBがハイレベルのとき、ラッチ回路333は、データを保持する。NAND回路334、NAND回路333は、データを保持する。NAND回路334、NAND回路333は、データを保持する。NAND回路334、NA回路333に保持する。NAND回路333は、データを保持する。NAND回路334、NA回路333に保持する。NAND回路333に保持する。NAND回路333に保持する。Tボハイレベルのときに、リードラータバス(第1の伝送線トンジスタ337は、サードデータバスク3336、NチャンネルMOSトランジスタ337は、共にオフリードデータバッファRBFは、出力ハイインピーダンスの状態になる。なお、小振幅信号がリードデータバスROSFFは、出力ハイインピーダンスの状態になる。なお、小振幅信号がリードデータバスROSを高速に伝送するように構成されている。

#### [0036]

なお、リードデータバッファRBF内の回路のうち、NAND回路334の高電位側電源端子は内部電源VDLに接続され、低電位側電源端子は電源VSSに接続されている。また、NOR回路の高電位側電源端子は電源VDDに接続され、低電位側電源端子は電源VSLに接続され、ハチャンネルMOSトランジスタ337のソースは、内部電源VDLに接続され、NチャンネルMOSトランジスタ337のソースは、内部電源VSLに接続されている。なお、高電位側の内部電源VSDは、高電位側電源VDD以下の電圧の半導体装置1の内部で生成した電源であり、低電位側の内部電源VSLは、低電位側電源VSS以上の電圧の半導体装置1の内部で生成した電源電圧である。なお、高電位側電源VDD、高電位側内部電源VSD、低電位側内部電源VSL、低電位側電源VSSの電位を示すと式(1)のとおりである。

### [0037]

VDD VDL>VSL VSS 式(1)

### [ 0 0 3 8 ]

第1のドライバ回路となるPチャンネルMOSトランジスタ336、NチャンネルMOSトランジスタ337は、それぞれ、ソースがVDL、VSLに接続されているので、リードデータバッファ回路RBFからリードライトデータバスRWBSへ出力される信号は、高電位側VDL、低電位側VSLの小振幅信号となり、電源が電源VDDとVSSに接続されているドライバ回路より小振幅の信号となる。従って、リードライトデータバスRWBSの充放電電流を減らし、振幅を小さくすることにより、高速な信号の伝播が可能となる。

## [0039]

また、NAND回路334の低電位側の電源をVSS、NOR回路335の高電位側の電源をVDDから取っているので、VDLとVSL間の電位差が小さくても、VDLとVSSとの電位差、VDDとVSLとの電位差が、それぞれ、PチャンネルMOSトランジスタ336のトランジスタ閾値、NチャンネルMOSトランジスタ336とNチャンネルMO

20

30

40

50

S トランジスタ 3 3 7 からなる第 1 のドライバは動作する。 したがって、リードライトデータバス R W B S を伝送する信号を小振幅にすることが可能である。

#### [0040]

共通基準電圧回路40は、内部回路側で基準電圧信号VREFを出力する内部回路側基準電圧回路41と、外部端子側で基準電圧信号VREFを出力する外部端子側基準電圧回路42を備える。内部回路側基準電圧回路41と外部端子側基準電圧回路42は、共に、高電位側内部電源VDLに接続されたスイッチS1と、低電位川内部電源VSLに接続されたスイッチS2と、基準電圧VREFを伝送する第2の伝送線VREFとスイッチS1との間に接続された抵抗R1と、第2の伝送線VREFとスイッチS1との間に接続された抵抗R1と、第2の伝送線VREFとスイッチS1た抵抗R2を備えている。また、抵抗R1と抵抗R2の抵抗値は互いにほぼ等しく、その抵抗値は、1k 以上であり、比較的高抵抗である。抵抗R1と抵抗R2の抵抗値がほぼ等しいので、スイッチS1、S2を閉じたときは、第2の伝送線VREFの基準電圧VREFは、おおよそ式(2)で示す電圧となる。

[0041]

VREF=1/2(VDL+VSL) 式(2)

#### [0042]

リードデータレシーバ(第1のレシーバ)RAMPは、リードライトデータバス(第1の伝送線)RWBSが非反転信号入力端子に、第2の伝送線VREFが反転信号入力端子に接続され、リードライトデータバスRWBSを伝送されてくる小振幅信号を第2の伝送線の基準電圧信号VREFと比較する差動回路である。差動回路の出力信号は、リードデータラッチRLATに接続され、制御信号RLATOUTBがロウレベルのときに、リードデータラッチRLATに取り込まれる。なお、制御信号RLATOUTBがハイレベルのとき、リードデータラッチRLATはデータを保持する。リードデータラッチRLATの出力信号ROUTは、並直列変換回路(図2の並直列変換/並直列変換回路362の並直列変換部)に接続される。

[0043]

ライトデータバッファWBFは、ラッチ回路363と、NAND回路364とNOR回路365を含むプリバッファ回路と、PチャンネルMOSトランジスタ366とNチャンネルMOSトランジスタ367を含むバッファ回路により構成される。ラッチ回路363は、ラッチタイミング制御信号WLATINBがロウレベルのときに図2の並直列変換/並直列変換回路362の直並列変換データ信号であるWINを取り込む。ラッチ回路363は、ラッチタイミング制御信号WLATINBがハイレベルのときは取り込んだデータを保持する。

[0044]

NAND回路364、NOR回路365、PチャンネルMOSトランジスタ366、NチャンネルMOSトランジスタ367は、第3のドライバ回路として機能し、ラッチ回路363に取り込んだライトデータを制御信号DWACTがハイレベルのときに、リードライトデータバスRWBSへ小振幅信号として出力する。制御信号DWACTがロウレベルのときはPチャンネルMOSトランジスタ366、NチャンネルMOSトランジスタ367は、共にオフし、ライトデータバッファWBFは、出力ハイインピーダンスの状態になる。

[0045]

なお、ライトデータバッファWBF内の回路のうち、NAND回路364の高電位側電源端子は内部電源VDLに接続され、低電位側電源端子は電源VSSに接続されている。また、NOR回路365の高電位側電源端子は電源VDDに接続され、低電位側電源端子は電源VSLに接続されている。また、バッファ回路を構成するPチャンネルMOSトランジスタ366のソースは、内部電源VDLに接続され、NチャンネルMOSトランジスタ367のソースは、内部電源VSLに接続されている。

[0046]

第3のドライバ回路となるPチャンネルMOSトランジスタ366、NチャンネルMO

20

30

40

50

Sトランジスタ367は、それぞれ、ソースがVDL、VSLに接続されているので、ライトデータバッファ回路WBFからリードライトデータバスRWBSへ出力される信号は、高電位側VDL、低電位側VSLの小振幅信号となり、電源がVDDとVSSに接続されているドライバ回路より小振幅の信号となる。従って、リードライトデータバスRWBSの充放電電流を減らし、振幅を小さくすることにより、高速な信号の伝播が可能となる

## [0047]

また、NAND回路364の低電位側の電源をVSS、NOR回路365の高電位側の電源をVDDから取っているので、VDLとVSL間の電位差が小さくても、VDLとVSLの電位差が、それぞれ、PチャンネルMOSトランジスタ366のトランジスタ閾値、NチャンネルMOSトランジスタ367のトランジスタ閾値を超える電圧であれば、PチャンネルMOSトランジスタ366とNチャンネルMOSトランジスタ367からなる第1のドライバは動作する。したがって、リードライトデータバスRWBSを伝送する信号を小振幅にすることが可能である。

## [0048]

ライトデータレシーバWAMPは、リードライトデータバス(第1の伝送線)RWBSが非反転信号入力端子に、第2の伝送線VREFが反転信号入力端子に接続され、リードライトデータバスRWBSを伝送されてくる小振幅信号を第2の伝送線の基準電圧信号VREFと比較する差動回路である。差動回路の出力信号は、ライトデータラッチWLATに接続され、制御信号WLATOUTBがロウレベルのときに、ライトデータラッチWLATに取り込まれる。なお、制御信号WLATOUTBがハイレベルのとき、ライトデータラッチWLATはデータを保持する。ライトデータラッチWLATの出力信号DWBは、リードライトアンプRWAMP(図2参照)に接続される。

#### [0049]

なお、リードライトデータバス(第1の伝送線)RWBSと第2の伝送線VREFは、各内部回路側入出力回路33と外部端子側入出力回路36に接続されるが、外部端子側基準電圧回路42は、外部端子側入出力回路36の近傍に配置され、内部回路側基準電圧回路41は、第1の伝送線RWBSと第2の伝送線VREFの配線上において、外部端子側入出力回路36から最遠端に配置される内部回路側入出力回路33の近傍か、さらに遠くに配置することが望ましい。また、内部回路側基準電圧回路41は、バンク毎に各バンクに対応して設けられた内部回路側入出力回路33の近傍に配置してもよい。

## [0050]

また、第2の伝送線VREFは、内部電源配線VDLと内部電源配線VSLに挟まれて 各内部回路側入出力回路33から外部端子側入出力回路36まで配線されている。このように配線すると、内部電源配線VDLと第2の伝送線VREFとの配線間容量と、内部電源配線VSLと第2の伝送線VREFとの配線間容量は、共に大きな値となる。

## [0051]

一方、各第1の伝送線RWBSは、信号の伝播が内部電源配線VDL及び内部電源配線VSLに影響を与えないように、内部電源配線VDL及びVSLから離間して配線されている。内部電源配線VSLと内部電源配線VDL及びVSLとの距離は、第1の伝送線RWBSの小振幅信号の伝送が配線間容量や相互インダクタンスにより内部電源配線VDLとVSLの電位に大きな影響を与えないように離せば十分である。

## [0052]

図4は実施例1における内部電源 VDL、VSLを生成する内部電源生成回路50のブロック図である。内部電源生成回路50は、半導体装置1の内部に設けられ、外部から供給される高電位側電源VDDと低電位側電源VSSから内部高電位電源VDL、内部低電位電源VSLを生成する。なお、図4では、内部高電位電源VDLは、電源VDDから第1の内部電源生成回路51により生成し、内部低電位電源VSLは電源VSSから第2の内部電源生成回路52によって生成している。なお、図4の内部電源生成回路50の構成は、一例であり、半導体装置1の内部回路で用いる電源VDD、VSSの電位に対して、上

20

30

40

50

記式(1)の関係を満たす電源VDL、VSLを生成する回路であれば、どのような回路 を用いてもよい。

## [0053]

図5は、図3におけるリードデータレシーバ(第1のレシーバ)RAMP及びライトデータレシーバ(第2のレシーバ)WAMPの一例を示す回路プロック図である。図5のデータレシーバ回路は、制御信号が異なるだけで、リードデータレシーバRAMPにもライトデータレシーバWAMPにも用いることができる。図5のデータレシーバは、電流源となるNチャンネルMOSトランジスタ345、差動対を構成するNチャンネルMOSトランジスタ341と342と、を含む差動回路と、自行回路となるPチャンネルMOSトランジスタ341と342と、を含む差動回路と、PチャンネルMOSトランジスタ346とNチャンネルMOSトランジスタ347とを含む出力回路を備えている。上記構成により基準電圧信号VREFとリードライトデータバスRWBSとの電位差が小さい場合でも、電源VDDと電源VSSとの間でフルに振幅するデジタル信号に変換して出力端子Voutから出力する。

## [0054]

図 3 で説明したように、第 2 の伝送線 V R E F は、内部電源配線 V D L 、 V S L の間に 配置し、かつ、各第1の伝送線RWBSを内部電源配線VDL、VSLから離間して配置 している。図6、図20を参照して、図3において、第2の伝送線VREFが、内部電源 配線VDL、VSLの間に配置している理由について説明する。図2、3において、メモ リセルアレイ10の配置位置と、データI/O端子22との半導体チップ1上の配置によ って、メモリセルアレイ10の近傍に配置する内部回路側入出力回路33とデータェノO 端子22の近傍に配置する外部端子側入出力回路36とは、離間して配置される場合があ る。そのような場合、内部回路側入出力回路33と外部端子側入出力回路36との間を接 続 す る 複 数 の 第 1 の 伝 送 線 R W B S と 、 第 2 の 伝 送 線 V R E F の 長 さ は 長 く な ら ざ る を 得 ない。その伝送線のその長さは、半導体チップ1の長辺の長さに相当するか、半導体チッ プ1の長辺の長さを超えることも考えられる。特に第1の伝送線RWBSはリードライト データを高速に伝送するため、第1のドライバであるPチャンネルMOSトランジスタ3 3 6 、 N チャンネル M O S トランジスタ337、 及び第3のドライバである P チャンネル MOSトランジスタ366、NチャンネルMOSトランジスタ367の出力インピータダ ンスは低インピーダンスにする必要がある。また、第1の伝送線RWBSは、8~128 本存在し、8~128ビット並列にデータを転送するので、内部電源VDL、VSLは、 第 1 の 伝 送 線 R W B S に 出 力 す る デ ー タ に よ っ て 、 電 源 の 電 位 が あ る 程 度 変 動 す る 。 内 部 電 源 V D L 、 V S L の 電 位 が 変 動 し て も 第 1 の ド ラ イ バ ( 3 3 6 、 3 3 7 ) 、 第 3 の ド ラ イバ ( 3 6 6 、 3 6 7 ) は比較的低インピーダンスであるので、内部電源 V D L 、 V S L の電位の変動にすばやく反応し、第1の伝送線RWBSを伝送する小振幅信号の電位は、 内部電源VDL、VSLの電位の変動を反映した電位となる。

## [0055]

一方、第2の伝送線VREFを伝送するのは、基準電圧信号であり、電位の変動が基本的にないので、第2のドライバ41、第4のドライバ42の出力インピータダンスは低くする必要がない。また、第2の伝送線VREFは、待機時においても、中間電位VREFを維持する必要があり、消費電力を低減するため、第2のドライバ41、第4のドライバ41、第4のドライバ41、第4のドライバ41、第4のドライバ41、第4のドライバ41、第4のドライバの電圧が変動した場合でも第2の伝送線VREFの電位はすぐには反応しない。すなわち、内部電源VDL、VSLの電位がゆれた場合、第1の伝送線を伝送する小振幅信号が、電源の変動に対応して電位がすばやく反応するのに対して、第2の伝送線VREFの電位の変動が遅いので、第1のレシーバRAMP、第2のレシーバWAMPの電圧マージンが減少する。さらに、小振幅信号の振幅を小さくして、高速、かつ、低消費電力化を実現しようとした場合、内部電源VDL、VSLの電位変動より誤動作する恐れも生じる。

## [0056]

図20は、第1のドライバの内部電源VDL、VSLとは共通インピーダンスを持たないVDL、VSLと同一電圧の別電源VDL2、VSL2から第2のドライバが基準電圧

20

30

40

50

VREFを生成し、第1のレシーバに基準電圧を供給し、かつ、基準電圧VREFと内部電源VDL及びVSLとの間に容量を設けない場合を想定した比較例の図面である。図20では、内部電源VDL、VSLは電源ノイズにより電位が変動し、この電位の変動は、第1の伝送線RWBSを伝送する小振幅信号の電圧レベルに影響を与える。また、小振幅信号は、第1の伝送線RWBSを伝送中に半導体基板などからのコモンノイズの影響を受ける。

## [0057]

一方、基準電圧VREFは、内部電源VDL、VSLの変動の影響を受けず、第1の伝送線RWBSが受ける基板などからのコモンノイズの影響も受けないとする。そうすると、小振幅信号の電圧が内部電源VDL、VSLの電圧変動の影響や半導体基板などからのコモンノイズを受けるとその分、信号マージンが減少する。

[0058]

これに対して実施例1では、図3、図6に示すように、第2の伝送線VREFを内部電源配線VDLとVSLで挟んで配線しているので、第2の伝送線VREFと内部電源配線VDL、第2の伝送線VREFと内部電源配線VSLとの配線間容量は、大きくなり、内部電源VDL、及び/又は、内部電源VSLの電位がゆれると、配線間容量によって、第2の伝送線VREFの電位も同一方向に変動することになる。従って、第2のドライバ41、第4のドライバ42の出力インピーダンスが第1のドライバ(336、337)、第3のドライバ(366、367)より高く、内部電源VDL、VSLの電源電圧のゆれに対して第2のドライバ41、第4のドライバ42自体の反応が遅くとも、内部電源VDL、VSLの配線間容量により、第2の伝送線の基準電圧信号VREFの電位の変動が内部電源VDL、VSLの電源変動に対して追従するようにすることができる。

[0059]

さらに、図6に示すように第2の伝送線VREFの第2のドライバ41の好ましい配置位置は、第1の伝送線RWBSの第1のドライバRBFの近傍に配置し、第1のドライバRBFと第2のドライバ41との間の内部電源配線VDL、VSLの配線インピーダンスをできるだけ小さくすることが好ましい。そのように配置すれば、第1のドライバRBFによる内部電源VDL、VSLの電源変動がそのまま第2のドライバを介して第2の伝送線VREFの電圧変動として表れるからである。

[0060]

また、第1のレシーバRAMPに対して第2のドライバ41を第1のドライバRBFより遠くに配置し、第2の伝送線VREF、及び第2の伝送線を両側から挟んで配置する内部電源配線VDL、VSLの配線の途中に第1のドライバRBFを配置してもよい。そのように配置すれば、第1のドライバが受ける内部電源VDL/VSLの電源変動、第1の伝送線の途中に第1の伝送線RWBSが受ける基板などからのコモンノイズが内部電源VDL/VSLや第2の伝送線VREFにも同じように影響を与え、信号マージンを確保できるからである。

[0061]

なお、図6では、第1のドライバRBF、第2のドライバ41、第1のレシーバRAMPについて説明したが、第3のドライバWBF、第4のドライバ42、第2のレシーバWAMPの場合も同様である。この様な配置にすることにより、内部電源VDL、VSLの電源変動に対する、第1のレシーバRAMP、第2のレシーバWAMPの動作マージンを増やし、誤動作の可能性を抑制することができる。さらには、第1の伝送線RWBSを伝送する信号の振幅をさらに小さな振幅とすることにより、第1の伝送線RWBSを充放電する電流を減らし、さらに低消費電力化を図ると共に、より高速な信号の伝送を可能にすることもできる。

[0062]

なお、第2の伝送線VREFの両側を内部電源VDLと内部電源VSLで挟むことにより、第2の伝送線VREFに対する内部電源VDLとの配線間容量と内部電源VSLとの配線間容量が実質的に等しくするように配線することもできる。そのように配線すること

20

30

40

50

により、内部電源VDL、内部電源VSLのどちらの電源電圧が揺れた場合にも、第2の伝送線を伝送する基準電圧信号VREFの電位が追従するようにすることができる。さらに、内部電源配線VDLと内部電源配線VSLとによって第2の伝送線を挟むことによって、内部電源配線VDL、VSL以外の内部配線や外部からのノイズに対して第2の伝送線VREFをシールドする効果も得られ、誤動作の可能性をさらに抑制することができる

#### [0063]

図7(a)は、内部回路側から外部端子側にデータを伝送するとき(リードコマンド実行時)のドライバの状態を説明する図であり、(b)は外部端子側から内部回路側にデータを伝送するとき(ライトコマンド実行時)のドライバ回路の状態を説明する図である。図7(a)に示すように、内部回路側から外部端子側にデータを伝送するときは、第1のドライバRBF、第2のドライバ41が導通し、第3のドライバWBF、第4のドライバ42は出力ハイインピーダンスの状態になる。従って、第1の伝送線RWBSを伝送する小振幅信号も第2の伝送線VREFを伝送する基準電圧信号も内部回路側から外部端子側へ出力する。外部端子側の第1のレシーバRAMPは、内部回路側入出力回路が出力する基準電圧信号VREFに基づいて、小振幅信号の電圧レベルを判定する。また、内部回路側の第2のレシーバWAMPは動作を停止する。

#### [0064]

図7(b)に示すように、外部端子側から内部回路側にデータを伝送するとき(ライトコマンド実行時)は、第3のドライバWBF、第4のドライバ42が導通し、第1のドライバRBF、第2のドライバ41は出力ハイインピーダンスの状態になる。従って、第1の伝送線RWBSを伝送する小振幅信号も第2の伝送線VREFを伝送する基準電圧信号も外部端子側から内部回路側へ出力する。内部回路側の第2のレシーバWAMPは、外部端子側入出力回路が出力する基準電圧信号VREFに基づいて、小振幅信号の電圧レベルを判定する。また、外部端子側の第1のレシーバRAMPは動作を停止する。

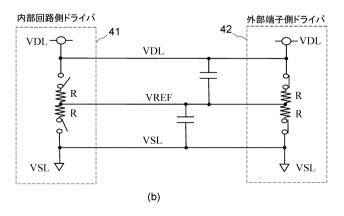

#### [0065]

図8(a)は、実施例1において、リード動作時の基準電圧ドライバ(第2のドライバと第4のドライバ)41、42の状態を説明する図である。また、図8(b)は、実施例1において、ライト動作時の基準電圧ドライバ41、42の状態を説明する図である。図8(a)に示すように、リード動作時には、内部回路側ドライバ(第2のドライバ)41を導通させる一方、外部端子側ドライバ(第4のドライバ)42を出力ハイインピーダンスにして、第1の伝送線を伝送するリードデータに合わせて、第2の伝送線も、内部回路側から外部端子側へ基準電圧VREFを伝送する。

## [0066]

一方、図 8 ( b ) に示すように、ライト動作時には、外部端子側ドライバ(第 4 のドライバ) 4 2 を導通させる一方、内部回路側ドライバ(第 2 のドライバ) 4 1 を出力ハイインピーダンスにして、第 1 の伝送線を伝送するライトデータに合わせて、第 2 の伝送線も、外部端子側から内部回路側へ基準電圧 V R E F を伝送する。

## [0067]

上記動作により、内部回路側から外部端子側にデータを伝送するときは、データを出力する内部回路側の内部電源VDL、VSLの変動についてデータを受ける外部端子側のレシーバ(第1のレシーバ)の基準電圧VREFに反映することができる。一方、外部端子側から内部回路側にデータを伝送するときは、データを出力する外部端子側の内部電源VDL、VSLの変動についてデータを受ける内部回路側のレシーバ(第2のレシーバ)の基準電圧VREFに反映することができる。

## 【実施例2】

### [0068]

実施例2は、外部端子側のドライバと内部回路側のドライバについて、それぞれのドライバと内部電源配線VDL、VSLとを切り離す複数のスイッチを設けて、基準電圧信号VREFが内部回路側と外部端子側のうち、データを出力する側の内部電源VDL、VS

Lの揺らぎをより的確にデータを受ける側の基準電圧信号VREFの揺らぎに反映させる 実施例である。

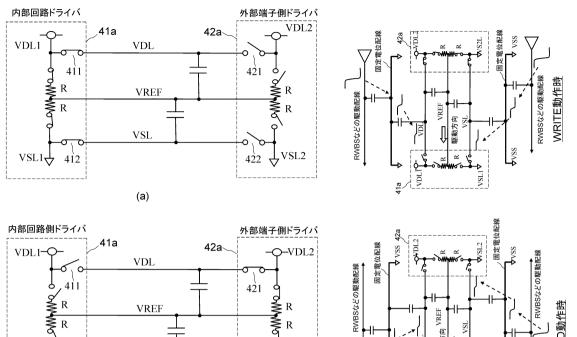

## [0069]

図 9 ( a ) は、内部回路側から外部端子側にデータを出力(リードデータ出力)すると き の 内 部 回 路 側 の 基 準 電 圧 ド ラ イ バ ( 第 2 の ド ラ イ バ ) 4 1 a と 外 部 端 子 側 の 基 準 電 圧 ド ライバ42aの動作を説明する図である。実施例2では、実施例1の基準電圧ドライバ4 1、42(図3、図8参照)と異なり、基準電圧ドライバ41a、42aの内部電源VD L1、VSL1、VDL2、VSL2を内部電源配線VDL、VSLから切り離すスイッ チ 4 1 1 、 4 1 2 、 4 2 1 、 4 2 2 を設けている。内部回路側から外部端子側にデータを 伝送(リードデータ出力)するときは、外部端子側基準電圧ドライバ42aの出力をハイ インピーダンスにするだけにとどまらず、スイッチ421、422をオフに設定すること により、外部端子側基準電圧ドライバ42aの内部電源端子VDL2、VSL2を内部電 源配線VDL、VSLから切り離している。一方、内部回路側の基準電圧ドライバ41a のスイッチ411、412をオンさせることにより、基準電圧ドライバ41aの内部電源 端子VDL1、VSL1は、スイッチ411、412を介して内部電源配線VDL、VS Lに接続されている。従って、電源配線VDL、VSLは、より忠実にデータを出力する 側(内部回路側)の内部電源電圧VDL1、VSL1を反映した電圧となり、電源配線V DL、VSLと基準電圧信号VREFとの配線間容量により、基準電圧信号VREFの電 位 を よ り 忠 実 に デ ー タ を 出 力 す る 内 部 回 路 側 の ド ラ イ バ 回 路 の 内 部 電 源 電 圧 V D L 1 、 V SL1を反映した電圧とすることができる。

#### [0070]

また、図9(b)に示すように、外部端子側から内部回路側にデータを転送(ライトデータ入力)するときには、スイッチ421と422をオンにして、スイッチ411と412をオフにしている。この様に設定することにより、内部回路側基準電圧ドライバ41aの出力をハイインピーダンスにするだけにとどまらず、内部回路側基準電圧ドライバの内部電源端子VDL1、VSL1を内部電源配線VDL、VSLから切り離している。一方、基準電圧ドライバ42aの内部電源端子VDL2、VSL2は、スイッチ421、422を介して内部電源配線VDL、VSLに接続されている。従って、電源配線VDL、VSLは、より忠実にデータを出力する側(外部端子側)の内部電源電圧VDL2、VSL2を反映した電圧となり、電源配線VDL、VSLと基準電圧信号VREFとの配線間容量により、基準電圧信号VREFの電位をより忠実にデータを出力する外部端子側のドライバ回路の内部電源電圧VDL1、VSL1を反映した電圧とすることができる。

#### [0071]

なお、スイッチ411、412、421、422を設け、内部回路側と外部端子側のドライバの内部電源VDL1、VSL1、VDL2、VSL2のうち、データを受ける側のドライバを内部電源配線VDL、VSLから切り離すこと以外は、実施例2の構成及び動作は、実施例1と同一であるので、重複する説明は省略する。

#### [0072]

また、実施例2において、内部電圧生成回路50(図4参照)を外部端子側と内部回路側にそれぞれ設け、内部回路側に設けた内部電圧生成回路50は、内部回路側の第1のドライバ(図3の336、337)、第2のドライバ41aに内部電源VDL1、VSL1を供給し、外部端子側に設けた内部電圧生成回路50は、外部回路側の第3のドライバ(図3の366、367)、第4のドライバ42aに内部電源VDL2、VSL2を供給するようにしてもよい。そして、内部電源配線VDL、VSLには、内部電源VDL1、VSL1とVDL2、VSL2のうち、データを出力する側の内部電圧生成回路50が生成した内部基準電圧を供給するようにしてもよい。

### [0073]

図11は、内部電源VSLが変動した場合の(a)実施例2における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。図11(a)では、第2の伝送線VREFと低電位側内部電源配線VSLとを隣接して配置し

10

20

30

40

、第2の伝送線VREFと内部電源配線VSLとの配線間容量を大きくしている。一方、図11(b)は、比較例で第2の伝送線VREFと内部電源配線VSLとの配線間容量は設けていない。

[0074]

図11において、縦軸は電圧(V)であり、横軸は時間(ns)である。VDD=1.5 V、VSS=0V、VSL=0.5 V、VDL=0.9 V、VREF=0.7Vに設定している。ただし、VSLは、0.5 Vに完全に固定されておらず、回路動作に連動して最大で0.6 Vまで浮き上がっている(例えば、152ns前後参照)。また、図11(a)の実施例では、VSLとVREF間の配線間容量により、第2の伝送線VREFは、VSLの変動に連動して0.7Vから0.75Vまでの範囲で変動している。

[0075]

第1の伝送線RWBSがロウレベルを伝送するときの電圧レベルをVRWBS(L)とすると、そのときの信号量(第1の伝送線を伝送するロウレベルの電圧と第2の伝送線の基準電圧との電圧マージン)は、本来、式(3)で表すことができる。

[0076]

VREF-VRWBS(L)=0.7V-0.5V=0.2V 式(3)

[0077]

すなわち、低電位側内部電源電圧VSLに揺れがなければ、第1の伝送線RWBSの口ウレベルには、式(3)に示すとおり0.2Vの電圧マージンが存在する。しかし、低電位側内部電源電圧VSLが電圧の揺れにより、0.5Vより上昇すると、その分、VRWBS(L)も上昇し、電圧マージンが減少する。図11では、低電位側内部電源電圧VSLは、0.5Vから0.6Vに上昇している(浮き上がっている)ので、その分電圧マージンは減る。しかし、この実施例では、低電位側内部電源電圧VSLと第2の伝送線VREFとの間に積極的に配線間容量を設けているので、低電位側内部電源電圧VSLが浮き上がるときは、第2の伝送線VREFの電位も浮き上がっており、電圧マージンの減少を抑制している。この低電位側内部電源電圧VSLが0.5Vから0.6Vに上昇している(図11(a)の152ns前後を参照)。このときの電圧マージンは、式(4)で表すことができる。

[0078]

VREF-VRWBS(L)=0.75V-0.6V=0.15V 式(4)

[0079]

すなわち、何も対策を行わない場合には、低電位側内部電源電圧VSLが上昇すると、その上昇した電圧分だけ電圧マージンが減ってしまうが、配線間容量により低電位側内部電源電圧VSLが上昇したときに、基準電圧VREFの電圧も上昇するので、電圧マージンの減少を抑制することができる。

[0080]

一方、図11(b)の比較例では、低電位側内部電源電圧VSLと第2の伝送線VREF間には配線間容量を設けていないので、低電位側内部電源電圧VSLの電位が上昇すると、その上昇した電圧は、そのまま電圧マージンの減少として現れる。すなわち、図11(b)での電圧マージンは、式(5)で表すことができる。

[0081]

VREF-VRWBS(L)=0.7V-0.6V=0.1V 式(5)

[ 0 0 8 2 ]

図11(b)の比較例では、式(5)に示すとおり、低電位側内部電源電圧VSLが0.1V上昇すると、式(5)に示すとおり電圧マージンは、0.1Vに減少するが、図11(a)の実施例によれば、式(4)に示すとおり、電圧マージンは、0.15V確保できている。すなわち、式(3)の本来の電圧マージン0.2Vを基準とすると、比較例の式(5)の0.1Vに対して実施例の式(4)は0.15Vであるので、電圧マージン(信号量)が25パーセント改善されている。また、電圧マージンの改善により、アクセス

10

20

30

40

時間も0.14ns改善されている。

[0083]

次に、図12は、内部電源VDLが変動した場合の(a)実施例2における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。図12(a)では、第2の伝送線VREFと高電位側内部電源配線VDLとを隣接して配置し、第2の伝送線VREFと内部電源配線VDLとの配線間容量を大きくしている。一方、図12(b)は、比較例で第2の伝送線VREFと内部電源配線VDLとの配線間容量は設けていない。

[0084]

図 1 2 において、縦軸は電圧(V)であり、横軸は時間(ns)である。VDD=1.5 V、VSS= 0 V、VSL= 0 .5 V、VDL= 0 .9 V、VREF= 0 .7 Vに設定している。ただし、VDLは、 0 .9 Vに完全に固定されておらず、回路動作に連動して最大で 0 .8 Vまで沈み込んでいる(図 1 2 の 1 4 7 n s 近辺参照)。また、図 1 2 ( a )の実施例では、VDLとVREF間の配線間容量により、第 2 の伝送線VREFは、VDLの変動に連動して 0 .6 5 V から 0 .7 Vまでの範囲で変動している。

[0085]

第1の伝送線RWBSがハイレベルを伝送するときの電圧レベルをVRWBS(H)とすると、そのときの信号量(第1の伝送線を伝送するハイレベルの電圧と第2の伝送線の基準電圧との電圧マージン)は、本来、式(6)で表すことができる。

[0086]

VRWBS(H) - VREF=0.9V-0.7V=0.2V 式(6)

[0087]

すなわち、高電位側内部電源電圧VDLに揺れがなければ、第1の伝送線RWBSのハイレベルには、式(6)に示すとおり0.2Vの電圧マージンが存在する。しかし、高電位側内部電源電圧VDLが電圧の揺れにより、0.9Vより下降すると、その分、VRWBS(H)も下降し、電圧マージンが減少する。図12では、高電位側内部電源電圧VDLは、0.9Vから0.8Vに下降している(沈み込んでいる)ので、その分電圧マージンは減る。しかし、この実施例では、高電位側内部電源電圧VDLと第2の伝送線VREFとの間に積極的に配線間容量を設けているので、高電位側内部電源電圧VDLが沈み込むときは、第2の伝送線VREFの電位も沈み込んでおり、電圧マージンの減少を抑制している。この高電位側内部電源電圧VDLが0.9Vから0.8Vに下降している(図12(第2の伝送線の基準電圧VREFは、0.7Vから0.65Vに下降している(図12(a)の147ns前後を参照)。このときの電圧マージンは、式(7)で表すことができる。

[0088]

VRWBS(H)-VREF=0.8V-0.65V=0.15V 式(7)

[0089]

すなわち、何も対策を行わない場合には、高電位側内部電源電圧VDLが下降すると、その下降した電圧分だけ電圧マージンが減ってしまうが、配線間容量により高電位側内部電源電圧VDLが下降したときに、基準電圧VREFの電圧も下降するので、電圧マージンの減少を抑制することができる。

[0090]

一方、図12(b)の比較例では、高電位側内部電源電圧VDLと第2の伝送線VREF間には配線間容量を設けていないので、高電位側内部電源電圧VDLの電位が下降すると、その下降した電圧は、そのまま電圧マージンの減少として現れる。すなわち、図12(b)での電圧マージンは、式(8)で表すことができる。

[0091]

VRWBS(H)-VREF=0.8V-0.7V=0.1V 式(8)

[0092]

図12(b)の比較例では、式(8)に示すとおり、高電位側内部電源電圧VDLが0

10

20

30

40

40

20

30

40

50

. 1 V下降すると、式(8)に示すとおり電圧マージンは、0. 1 Vに減少するが、図12(a)の実施例によれば、式(7)に示すとおり、電圧マージンは、0. 1 5 V確保できている。すなわち、式(6)の本来の電圧マージン0. 2 Vを基準とすると、比較例の式(8)の0. 1 Vに対して実施例の式(7)は0. 1 5 Vであるので、電圧マージン(信号量)が25パーセント改善されている。また、電圧マージンの改善により、アクセス時間も0.26ns改善されている。

#### 【実施例3】

## [0093]

実施例3は、第2の伝送線VREFを挟むように配置された内部電源配線VDL、VS Lとその外側にさらに配線される電位が変動する駆動配線との間にVSSやVDD等の固 定電位に接続された配線を設けることにより、駆動配線の伝送する信号の電圧レベルの変 動が、 第2の 伝送線VREF や内部電源配線VDL、VSLに影響を与えないようにする 実 施 例 で あ る 。 第 2 の 伝 送 線 V R E F を 駆 動 す る 第 2 の ド ラ イ バ 4 1 、 第 4 の ド ラ イ バ 4 2 は、出力インピーダンスが比較的高いのでノイズの影響を受けやすい。第2の伝送線 V R E F の両側を内部電源配線 V D L 、 V S L で挟んでもさらに内部電源配線 V D L 、 V S Lの外側に配置された信号配線の電位が変動するとその影響を内部電源配線VDL、VS Lが受けて、内部電源配線VDL、VSLの電位が変動し、さらにその内部電源配線VD L、 V S L の揺れが第 2 の伝送線 V R E F の電位に影響を与える。データを出力する第 1 のドライバ ( 図 3 の 3 3 6 、 3 3 7 ) 、 第 3 のドライバ ( 図 3 の 3 6 6 、 3 6 7 ) の内部 電源VDL、VSLの揺らぎと連動して第2の伝送線VREFの電位が変動することは、 好ましいが、データを出力する第1、第3のドライバの電源電位の変動に基づかない内部 電源配線VDL、VSLの揺らぎによる第2の伝送線VREFの揺らぎは誤動作を生じさ せる恐れがある。実施例3では、第2の伝送線VREFを挟んで配置された内部電源配線 VDL、VSLとノイズとなる信号配線(駆動配線)との間に固定電位に接続された配線 を 配 置 す る こ と に よ り 、 丿 イ ズ と 新 配 線 が 配 線 間 の 寄 生 容 量 や 配 線 間 の 相 互 イ ン ダ ク タ ン ス等により悪影響を与えることを防いでいる。

## [0094]

図10は、実施例3において、(a)リード動作時(内部回路側から外部端子側へのデータ出力時)の内部電源線VDL、VSL及び基準電圧伝送線(第2の伝送線)VREFのノイズの影響と、(a)ライト動作時(外部端子側から内部回路側へのデータ入力時)の内部電源線及び基準電圧伝送線のノイズの影響と、を説明する図である。

## [0095]

図 1 0 ( a ) において、第 2 の伝送線 V R E F の両側を内部電源線 V D L と V S L が挟 んで配線されており、さらにその外側に固定電位配線(図10(a)では、電源VSSに 固定された配線)が配線されている。なお、電源VSSは、固定電位配線の一例であり、 電 源 VSS以外にも任意の電源線や通常動作時に使用しないテストモードの信号線などを 使 用 し て も よ い 。 第 1 の 伝 送 線 R W B S 等 の 電 位 が 変 動 す る 信 号 配 線 は 、 さ ら に そ の 外 側 に配線されている。信号配線と固定電位配線VSSとの間には配線間容量があるので、信 号配線(RWBSなどの駆動配線)の電位の変動により、固定電位配線(図10(a)で は、VSS)の電位は若干影響を受けて電位が変動する。さらに、固定電位配線VSSの 内側には、内部電源配線VDL、VSLが配線されている。固定電位配線VSSと内部電 源配線VDL、VSLとの間には、配線間容量があるので、固定電位配線VSSの電位の 変動はさらに減衰して内部電源配線VDL、VSLの電位に影響を与える。しかし、第2 の伝送線VREFは、さらにその内側に配線されているので、第1の伝送線RWBS等の 電位が変動する信号配線の電位が変動しても、最も内側に配線された第2の伝送線VRE F の電位には、ほとんど影響を与えない。なお、図10(a)において、リード動作時に 、内部回路側から外部端子側にリードデータを出力するときは、内部回路側基準電圧ドラ イバ 4 1 a を オン さ せ て 、 内 部 電 源 配 線 に 接 続 し 、 外 部 端 子 側 基 準 電 圧 ド ラ イ バ 4 2 a を 出 力 ハ イ イ ン ピ ー ダ ン ス に す る と 共 に 、 外 部 端 子 側 基 準 電 圧 ド ラ イ バ 4 2 a の 電 源 端 子 V DL2、VSL2は、実施例2と同様に、内部電源配線VDL、VSLから切り離してい

20

30

40

50

る。その効果は、実施例2で説明したとおりである。

### [0096]

一方、図10(b)に示すように、ライト動作時に、外部端子側から内部回路側にライトデータを入力するときは、外部端子側基準電圧ドライバ42aをオンさせて、内部電源配線に接続し、内部回路側基準電圧ドライバ41aを出力ハイインピーダンスにすると共に、内部回路側基準電圧ドライバ41aの電源端子VDL1、VSL1は、実施例2と同様に、内部電源配線VDL、VSLから切り離している。その効果は、実施例2で説明したとおりである。

### 【実施例4】

## [0097]

図13は、実施例4におけるデータバッファの回路ブロック図である。図13のデータバッファは、実施例1乃至実施例3におけるリードデータバッファRBF、及び/又は、ライトデータバッファWBFとして用いることができる(図2、図3参照)。図13のデータバッファは、リードデータバッファRBF、ライトテータバッファWBFのどちらにも用いることができるが、以下の実施例では、リードデータバッファRBFに用いる場合を例に説明する。

#### [0098]

図13において、メインリードバッファMRBFは、実施例1のリードバッファRBFとその構成、動作が同一である。図13では、このメインリードバッファMRBFに加えてさらに、サブリードバッファSRBFが設けられている。サブリードバッファSRBFを構成する回路の電源は、すべて電源VDDと電源VSSから供給されており、小振幅信号の電源である内部電源VDL、VSLは、サブリードバッファSRBFには供給されていない。このサブリードバッファSRBFは、メインリードバッファMRBFに対する補助ドライバとして機能する。

#### [0099]

サブリードバッファSRBFは、制御信号DPSとラッチ回路333が保持するデータ信号DRINが入力端子に接続されたNAND回路383と、制御信号DPSの反転信号とデータ信号DRINが入力端子に接続されたNOR回路384と、NAND回路383の出力信号がゲートに接続され、ソースが電源VDDに、ドレインが第1の伝送線RWBSに接続されたPチャンネルMOSトランジスタ381と、ゲートがNOR回路384の出力信号に接続され、ソースが電源VSSに、ドレインが第1の伝送線RWBSに接続されたNチャンネルMOSトランジスタ382を含んで構成される。

#### [0100]

図14は、実施例4におけるリードデータバッファRBFの動作波形図である。制御信号 DRACTは、リードデータバッファRBFの出力活性化信号であり、DRACTがハイレベルには出力ハイインとピーダスとしてがハイレベルになると、メインリードバッファMRBFのドライバは導通する。反転データ信号 DRBは、リードデータバッファRBFへカデータ信号であり、反転データ信号 DRBは、リードデータバッファRBFへカデータ信号である。RLATINBは、ラッチ回路333のラッチ信号であり、みからである。RLATINBの立下りに同期して反転データ信号 DRBを取り込べルのチラッチである「DPSは、サブリードバッファSRBFの制御信号であり、ハイレベルのときに、カッチ回路333のデータ出力信号である「DRINのデータに基づいて、アチャンの持する。「DPSは、「DRACTがハイレベルで、かっ、「ラッチ信号RLATINBがロスととのようのより、「フッチ回路333のデータが更新されるときのみ、「フンショットパルスとして出力される。

### [0101]

RWBSは、第1の伝送線RWBSの電圧レベルである。補助ドライバであるサブリー

20

30

40

50

ドバッファSRBFを設けないときの第1の伝送線RWBSの電圧レベルを破線で、補助ドライバであるサブリードバッファSRBFを設けたときの第1の伝送線RWBSの電圧レベルを実線で示す。補助ドライバが第1の伝送線RWBSの立ち上がり、立下りに同期して導通することにより、第1の伝送線RWBSの立ち上がり、立下りを急峻にすることができる。さらに、補助ドライバは、第1の伝送線RWBSの論理レベルが変わらないタイミングでは非導通となるので、第1の伝送線RWBSを伝送する信号が、不必要にオーバースイングすることはなく、小振幅な信号レベルを維持できる。

## [0102]

すなわち、サブリードバッファSRBFを設けることにより、内部電源電圧VDLとVSLとの電位差が小さくても、サブリードバッファSRBFにより、メインリードバッファMRBFの駆動能力を補うことができるので、第1の伝送線RWBSの充放電時間を短縮することができ、アクセス時間を短縮できる。

#### [ 0 1 0 3 ]

図 1 5 は、実施例 4 におけるデータレシーバの回路ブロック図である。図 1 5 のデータレシーバは、実施例 1 乃至実施例 3 における第 1 のレシーバ R A M P 、及び / 又は、第 2 のレシーバW A M P として用いることができる(図 2 、図 3 、図 5 参照)。図 1 5 のデータレシーバは、第 1 のレシーバ R A M P 、第 2 のレシーバW A M P のどちらにも用いることができるが、以下の実施例では、第 1 のレシーバ R A M P に用いる場合を例に説明する

## [0104]

図 1 5 のレシーバ R A M P は、電流源となる N チャンネル M O S トランジスタ 3 4 5 、 4 0 1 、 4 0 2 と、差動対を構成する N チャンネル M O S トランジスタ 3 4 3 、 3 4 4 と 、 負荷回路となる P チャンネル M O S トランジスタ 3 4 1 と 3 4 2 と、を含む差動回路と、 P チャンネル M O S トランジスタ 3 4 6 、 4 0 3 と N チャンネル M O S トランジスタ 3 4 7 、 4 0 4 とを含む出力回路とを備えている。

#### [0105]

図15の差動回路の電流源回路(345、401、402)は、第1の伝送線データの受信時(リードデータの出力時)には、常時電流IS1を流すNチャンネルMOSトランジスタ345による電流源と、一定のタイミングで電流IMを流すNチャンネルMOSトランジスタ401とNチャンネルMOSトランジスタ402のゲートには、制御信号DRLATが接続され、NチャンネルMOSトランジスタ345とNチャンネルMOSトランジスタ401のゲートには、制御信号DREAが接続されている。

## [0106]

また、出力回路は、ドライバとなるPチャンネルMOSトランジスタ346のソースと電源VDDとの間に、ゲートが制御信号DRLATの反転信号に接続されたPチャンネルMOSトランジスタ403と抵抗R11とが並列に接続されている。また、ドライバとなるNチャンネルMOSトランジスタ347のソースと電源VSSとの間に、ゲートが制御信号DRLATに接続されたNチャンネルMOSトランジスタ404と抵抗R12とが並列に接続されている。

## [0107]

図16は、図15のデータレシーバの動作波形図である。制御信号DRACTは、ドライバ側を制御する信号であり、DRINは、ドライバ側が出力するデータ信号である。また、RLATは、図13のRATINVの反転信号であり、DRINは、RATINVの立ち上がりに同期してデータが更新される。DRACTがハイレベルに立ち上がると、第1の伝送線には、データ信号DRINに基づいた小振幅信号が出力される。データレシーバは、制御信号DRACTの立ち上がりに同期して制御信号DREAを活性化し、差動回路への電流の供給を開始する。

## [0108]

制御信号DRLATは、制御信号RLATの位相を遅らせた信号である。データレシー

バは、ドライバ側の送信データの変化するタイミングに合わせて、制御信号DRLATをワンショットでハイレベルにする。制御信号DRLATがハイレベルになると、NチャンネルMOSトランジスタ402が導通し、差動回路(343、344)に流れる電流は、IS1からIS1+IMに増加する。差動回路に流す電流が増加すると、差動回路はより高速に動作し、比較結果をノードVAに出力する。

#### [0109]

また、制御信号 D R L A T がハイレベルになると、出力回路の P チャンネル M O S トランジスタ 4 0 3 と N チャンネル M O S トランジスタ 4 0 4 が導通し、出力回路は、ノード V A の電圧レベルを C M O S レベルの出力信号にレベル変換し、 D R O U T から出力する

## [0110]

次に、制御信号DRLATが立ち下がると差動回路に流れる電流はIS1に減少する。しかし、減少した電流の供給は維持されるので、差動回路は、比較結果のノードVAへの出力レベルを維持する。また、制御信号DRLATが立ち下がると出力回路のPチャンネルMOSトランジスタ404は非導通となる。出力回路のPチャンネルMOSトランジスタ403とNチャンネルMOSトランジスタ404が非導通となると出力回路の負荷駆動能力は減少するが、PチャンネルMOSトランジスタ403及びNチャンネルMOSトランジスタ404と並列に抵抗R11、R12が接続されているので、DROUTの出力電圧レベルは維持される。

#### [0111]

上記のデータレシーバを用いれば、第1の伝送線RWBSを伝送するデータが変化するタイミングで差動回路に流れる電流を増加させ、差動回路を高速に動作させるとともに、出力回路の駆動能力を増加させ、負荷を高速に駆動することができる。

#### [ 0 1 1 2 ]

一方、第1の伝送線を伝送するデータが変化しないタイミングでは、差動回路に流れる電流を減少させ、差動回路に流れる電流を抑制する。また、差動回路の出力のノードVAは完全なCMOSレベルではないので、差動回路が動作中は、出力回路に貫通電流が流れる。このとき、抵抗と並列に接続されたPチャンネルMOSトランジスタ403とNチャンネルMOSトランジスタ404が非導通となるように制御することにより、DROUTの出力電圧を維持しつつ、出力回路の貫通電流を減らすことができる。

#### [0113]

なお、制御信号DRLATは、ドライバ側のラッチ回路のラッチ信号を遅延させて生成することができる。上記図15と図16を用いて説明したデータレシーバは、実施例1乃至3のいずれのレシーバとして用いることもできる。

# 【実施例5】

## [0114]

図18は、実施例5によるデータバッファの回路ブロック図である。図18に示すデータバッファは、図13に示す実施例4のデータバッファに対して、ラッチ回路333のデータが更新された場合であっても、以前と同一データに更新され、第1の伝送線RWBSから出力する小振幅信号の論理レベルに変更がない場合は、サブリードバッファSRBF(サブライトバッファSWBF)を導通させずに、消費電力を削減する実施例である。実施例4のデータバッファと同様に、実施例5のデータバッファは、リードデータバッファRBFとしても用いる場合について、説明する。

#### [0115]

図18に示す実施例5のリードデータバッファRBFは、実施例4と同様に、メインリードバッファMRBFとサブリードバッファSRBFにより構成され、メインリードバッファMRBFと同一である。 実施例5のサブリードバッファSRBFは、RLATINBの立下りでDRINのデータをラッチするラッチ回路387と、ラッチ回路387とラッチ回路333のデータに基づ 10

20

30

40

20

30

40

50

いて、データが変化したときだけ、サブリードバッファSRBFのドライブトランジスタ381又は382を導通させる組み合わせ回路(NAND回路386、NOR回路385)を備えている。

[0116]

図19は、図18のリードデータバッファRBFの動作波形図である。制御信号DRACT、反転データ信号DRBNNは、実施例4と同一の信号であるので、重複した説明は省略する。DRIN1は、サブリードバッファSRBF内に設けたラッチ直路387の出力信号である。制御信号DPSは、実施例4と同じである。また、制御信号DPSPは、サブリードバッファSRBF内に設けたラッチ号DPSPは、サブリードバッファSRBFのドライバトランジスタであるPチャンネルMOSトランジスタ381は非導通となる。さらに、制御信号DPSNがロウレベルのときに、サブリードバッファSRBFのもう一つのドライバトランジスタであるNチャンネルMOSトランジスタ382は導通となる。RWBSは、第1の伝送線RWBSの電圧レベルである。

[0117]

図19で、リードデータバッファRBFへの入力データ信号である反転データ信号DRBと、ラッチ信号RLATINBと、ラッチ回路333にラッチされたデータ信号DRINに着目すると、ラッチ信号RLATINBの立ち下がリタイミングにおいて、ラッチされたデータ信号DRINの論理レベルが反転している場合と反転していない場合が存在する。例えば、時刻t1とt5ではデータ信号DRINはロウレベルからハイレベルに立ち上がり、時刻t3ではデータ信号DRINはハイレベルからロウレベルに立ち下がっているが、時刻t2、t4、t6では、ラッチ回路333のデータは以前と同じデータに更新されているため、データ信号DRINの論理レベルは以前の論理レベルを保持している。また、サブリードバッファSRBFに設けられたラッチ回路387の出力データ信号である。

[0118]

サブリードバッファSRBFは、このデータ信号DRIN、DRIN1と制御信号DPSに基づいて、データ信号DRINがロウレベルからハイレベルに立ち上がったときだけ(時刻t1、t5のみ)、1ショットで制御信号DPSPをロウレベルに制御し、PチャンネルMOSトランジスタ381を導通させ、データ信号DRINがハイレベルからハイレベルに立ち下がったときだけ(時刻t3のみ)、1ショットで制御信号DPSNをハイレベルに前御し、NチャンネルMOSトランジスタ382を導通させる。それ以外のタイミングでは、ラッチ回路333のデータが更新された場合であっても、以前と同一の論理レベルに更新され、第1の伝送線RWBSに出力する小振幅信号の論理レベルを変更うる必要がない場合は、PチャンネルMOSトランジスタ381やNチャンネルMOSトランジスタ381で、実施例4の効果にブスタ382を導通させないように制御している。この構成により、実施例4の効果にベルVDL、ロウレベルVSL)がVDL以上のハイレベルやVSL以下のロウレベルに不必要にオーバードライブされることを防ぐ効果が得られる。

【実施例6】

[0119]

図 1 7 は、半導体装置 1 を用いたデータ処理システムのブロック図である。図に示すデータ処理システム 5 0 0 は、データプロセッサ 5 2 0 と、半導体装置(DRAM) 1 が、システムバス 5 1 0 を介して相互に接続されている。データプロセッサ 5 2 0 としては、例えば、マイクロプロセッサ(MPU)、デジタルシグナルプロセッサ(DSP)などを

20

30

40

50

含むが、これらに限定されない。図17においては説明を簡単にするため、システムバス510を介してデータプロセッサ520とDRAM530とが接続されているが、システムバス510を介さずにローカルなバスによってこれらが接続されていても構わない。

[0120]

また、図17には、説明を簡単にするためシステムバス510が1組しか描かれていないが、必要に応じ、コネクタなどを介しシリアルないしパラレルに設けられていても構わない。また、図に示すデータ処理システムでは、ストレージデバイス540、I/Oデバイス550、ROM560がシステムバス510に接続されているが、これらは必ずしも必須の構成要素ではない。

[0121]

ストレージデバイス 5 4 0 としては、ハードディスクドライブ、光学ディスクドライブ、フラッシュメモリなどが挙げられる。また、I/Oデバイス 5 5 0 としては、液晶ディスプレイなどのディスプレイデバイスや、キーボード、マウスなどの入力デバイスなどが挙げられる。

[0122]

また、I/Oデバイス550は、入力デバイス及び出力デバイスのいずれか一方のみであっても構わない。

[0123]

さらに、図に示す各構成要素は、簡単のため1つずつ描かれているが、これに限定されるものではなく、1又は2以上の構成要素が複数個設けられていても構わない。

[0124]

実施例6において、DRAMを制御するコントローラ(例えばデータプロセッサ520)は、システムクロックCK,CKBとその他の制御信号を利用してDRAM10へデータのリードアクセスやライトアクセスに関連する各種コマンドを発行する。コントローラからリードコマンドを受けた半導体装置1は、内部に保持する記憶情報を読み出し、第1の伝送線RWBS(図1)を経由してシステムバス510へそのデータを出力する。また、コントローラからライトコマンドを受けた半導体装置1は、システムバス510から入力したデータを第1の伝送線RWBSを経由してメモリセルアレイ10にデータを書き込む。尚、コントローラが発行する前記複数のコマンドは、所謂、周知の半導体装置を制御する業界団体(JEDEC(Joint E1ectron Device Engineering Counci1) Solid State Technology Association)で規定されるコマンド(システムとしてのコマンド)である。

[0125]

また、実施例6において、DRAM10だけでなく、ストレージデバイス540、I/Oデバイス550、ROM560も、内部データの伝送に、実施例1乃至実施例5で説明した第1の伝送線RWBSと第2の伝送線VREFを用いた半導体装置とすることができる。データプロセッサからの要求に応答して各チップの内部において、高速、かつ、低消費電力にデータの入出力を行うことができる。

[0126]

なお、上記の実施例では、データの伝送が双方向である例について説明したが、データの伝送は、必ずしも双方向である必要はない。データの伝送が一方向である場合にも、本発明によれば、低消費電力で、かつ、高速にデータを伝送することができる。また、上記実施例1乃至5では、内部回路側と外部端子側との間でデータを伝送する実施例について説明したが、データの伝送は、内部回路側と外部端子側との間でのデータの伝送に限られず、内部回路同士のデータの伝送にも用いることができることは明らかである。

[0127]

さらに、実施例では、メモリのデータ信号の伝送について説明したが、本発明はこれに限られず、例えば、データプロセッサのデータの伝送に適用することもできる。更に、ドライバ、レシーバの具体的な回路形式、その他の制御信号を生成する回路は、実施例が開示する回路形式に限定されるものではない。たとえば、小振幅信号を生成する制御部分(

回路)は、実施例の開示に限られない。

[0128]

また、本発明による伝送線を備えた半導体装置は、CPU(Central Processing Unit)、MCU(Micro Control Unit)、DSP(Digital Signal Processor)、ASIC(Application Specific Integrated Circuit)、ASSP(Application Specific Standard Circuit)等の半導体装置全般に、適用することができる。このような本発明による半導体装置の製品形態としては、例えば、SOC(システムオンチップ)、MCP(マルチチップパッケージ)やPOP(パッケージオンパッケージ)などが挙げられる。これらの任意の製品形態、パッケージ形態を有する半導体装置に対して本発明を適用することができる。

[0129]

また、トランジスタは、電界効果トランジスタ(Field Effect Transistor;FET)であれば、MOS(Metal Oxide Semiconductor)に限定されず、MIS(Metal-Insulator Semiconductor)、TFT(Thin Film Transistor)等の様々なFETに適用できる。更に一部がバイポーラ型トランジスタであっても良い。FET以外のトランジスタであっても良い。

[0130]

なお、 P チャンネル M O S トランジスタ ( P 型 チャネル M O S トランジスタ ) は、 第 1 導電型のトランジスタ、 N チャンネル M O S トランジスタ ( N 型 チャネル M O S トランジスタ ) は、 第 2 導電型のトランジスタの代表例である。

[0131]

以上、図面を用いて説明したようにしたように、本発明は様々なモード(形態)に展開が可能であるか、好ましいモード(形態)をさらに、いくつか列挙すると以下の通りである。

[0132]

(モード1)

第3の電位の電源電圧と、前記第3の電位より低電位の第4の電位の電源電圧と、が供給されて動作する第1の論理回路と、

前記第1の論理回路の出力信号を、前記第3の電位以下の電位で、かつ、前記第4の電位より高電位な第1の電位をハイレベル、前記第1の電位より低電位で、かつ、前記第4の電位以上の第2の電位をロウレベルとし、前記第1の電位と前記第2の電位との電位差が、前記第3の電位と前記第4の電位との電位差より小さい小振幅信号に変換して出力するドライバ回路と、を備え、

前記ドライバ回路が、

電源が前記第1の電位と第2の電位とに接続され、前記出力信号に応答して前記小振幅信号を出力するメインドライバと、

電源が、前記第3の電位と、前記第4の電位と、に接続され、前記出力信号の論理レベルが変化しうるタイミングにおいて前記出力信号に応答して導通し、前記第1の信号の論理レベルが変化しないタイミングでは出力ハイインピーダンスとなる補助ドライバと、を備える

ことを特徴とする半導体装置。

上記モード1において、一例として図13、図18に示すように、第1の電位(例えば VDL)は、第3の電位(例えばVDD)より低い電位であることが好ましいが、第1の 電位と第3の電位は同電位であってもよい。また、第2の電位(例えばVSL)は、第4 の電位(例えばVSS)より高い電位であることが好ましいが、第2の電位と第4の電位 は同電位であってもよい。ただし、第1の電位と第2の電位との電位差(例えば、VDL とVSLとの電位差)は、第3の電位と第4の電位との電位差(例えば、VDDとVSS との電位差)より小さい小振幅信号である。 10

20

30

40

#### [0133]

(E-F2)

第3の電位の電源電圧と、前記第3の電位より低電位の第4の電位の電源電圧と、が供給されて動作する第1の論理回路と、

前記第1の論理回路の出力信号を、前記第3の電位以下の電位で、かつ、前記第4の電位より高電位な第1の電位をハイレベル、前記第1の電位より低電位で、かつ、前記第4の電位以上の第2の電位をロウレベルとし、前記第1の電位と前記第2の電位との電位差が、前記第3の電位と前記第4の電位との電位差より小さい小振幅信号に変換して出力するドライバ回路と、を備え、

前記ドライバ回路が、

10

電源が前記第1の電位と第2の電位とに接続され、前記出力信号に応答して前記小振幅信号を出力するメインドライバと、

前記出力信号の論理レベルの変化を検出する検出回路と、

電源が前記第3の電位と第4の電位とに接続され、前記検出回路が論理レベルの変化を検出したときに、前記出力信号に応答して導通し、前記検出回路が論理レベルの変化を検出しないときには、出力ハイインピーダンスとなる補助ドライバと、を備えることを特徴とする半導体装置。

例えば、図18の383~387は検出回路として機能する。

#### [0134]

(モード3)

20

第1の論理回路と、

前記第1の論理回路から離間して配置された第2の論理回路と、

前記第1の論理回路と前記第2の論理回路とを接続する伝送線と、

前記第1の論理回路の出力信号を前記第1の論理回路のハイレベルとロウレベルの信号レベルより電位差の小さい小振幅信号に変換して第1の伝送線に出力するドライバ回路と

前記小振幅信号を前記第2の論理回路が用いる信号のハイレベルとロウレベルの電位差を有する信号に変換して前記第2の論理回路に伝えるレシーバ回路と、を備え、

前記ドライバ回路は、

前記小振幅信号のハイレベルと同一電位の電源と、前記小振幅信号のロウレベルと同一電位の電源と、に接続され、前記出力信号を前記小振幅信号に変換して第 1 の伝送線に出力するメインドライバと、

前記第1の伝送線に接続された前記第1の論理回路と同一電源系の出力ドライバであって、前記出力信号の論理レベルが変化しうるタイミングにおいて前記出力信号に応答して 導通し、前記第1の信号の論理レベルが変化しないタイミングでは出力ハイインピーダン スとなる補助ドライバと、

を備えることを特徴とする半導体装置。

#### [0135]

(モード4)

第1の論理回路と、

40

30

前記第1の論理回路から離間して配置された第2の論理回路と、

前記第1の論理回路と前記第2の論理回路とを接続する伝送線と、

前記第1の論理回路の出力信号を前記第1の論理回路のハイレベルとロウレベルの信号レベルより電位差の小さい小振幅信号に変換して第1の伝送線に出力するドライバ回路と

前記小振幅信号を前記第2の論理回路が用いる信号のハイレベルとロウレベルの電位差を有する信号に変換して前記第2の論理回路に伝えるレシーバ回路と、を備え、

前記ドライバ回路は、

前記小振幅信号のハイレベルと同一電位の電源と、前記小振幅信号のロウレベルと同一電位の電源と、に接続され、前記出力信号を前記小振幅信号に変換して第1の伝送線に出

力するメインドライバと、

前記出力信号の論理レベルの変化を検出する検出回路と、

前記第1の伝送線に接続された前記第1の論理回路と同一電源系の出力ドライバであって、前記検出回路が論理レベルの変化を検出したときに、前記出力信号に応答して導通し、前記検出回路が論理レベルの変化を検出しないときには、出力ハイインピーダンスとなる補助ドライバと、

を備えることを特徴とする半導体装置。

[0136]

(E-F5)

前記ドライバ回路は、クロックに同期して前記第1の伝送線に出力するデータを更新し

前記レシーバ回路は、前記伝送線に接続され、前記小振幅信号を受信し増幅するアンプ部と、前記アンプ部により増幅した前記小振幅信号をより振幅の大きな前記第2の論理回路が用いるハイレベルとロウレベルを有する信号に整形して出力する出力部と、を備え、

前記小振幅信号の受信期間中に、前記クロックに同期して前記アンプ部に流す電流を増加減少させるとともに、前記クロックに同期して前記出力部の出力インピーダンス値を増加減少させる受信制御部と、

を備えることを特徴とする前記モード3又は4に記載の半導体装置。

[ 0 1 3 7 ]

以上、実施例について説明したが、本発明は上記実施例の構成にのみ制限されるものでなく、本発明の範囲内で当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

[ 0 1 3 8 ]

1 : 半導体装置

10:メモリセルアレイ

10-1:メモリセルアレイの一部領域

11:ロウデコーダ

12:センスアンプ(配置領域)

12-1:センスアンプ列

13:カラムセレクタ

13-1:カラムセレクタの一部(リードライトゲート)

14:コマンドデコーダ

15:コントロールロジック

16:カラムアドレスバッファ・バーストカウンタ

17:モードレジスタ

18:ロウアドレスバッファ

19:リフレッシュカウンタ回路

20:クロック生成器

2 1 : D L L

2 2 : 外部 I / O 端子

31:リードライトアンプ

3 3 : 内部回路側入出力回路

3 3 3 、 3 6 3 、 3 8 7 : ラッチ回路

3 3 4 、 3 6 4 、 3 8 3 、 3 8 6 : N A N D 回路

3 3 5 、 3 6 5 、 3 8 4 、 3 8 5 : N O R 回路

3 3 6 、 3 4 1 、 3 4 2 、 3 4 6 、 3 6 6 、 3 8 1 、 4 0 3 : PチャンネルMOSトランジスタ

3 3 7 、 3 4 3 、 3 4 4 、 3 4 5 、 3 4 7 、 3 6 7 、 3 8 2 、 4 0 1 、 4 0 2 、 4 0 4 : NチャンネルMOSトランジスタ

50

10

20

30

- 3 6:外部端子側入出力回路

- 3 6 1 : 入出力バッファ

- 362:並直列/直並列变換回路

- 40:共通基準電圧回路

- 4 1 : 内部回路側基準電圧ドライバ (第2のドライバ)

- 42:外部端子側基準電圧ドライバ(第4のドライバ)

- 50:内部電源生成回路

- 5 1:第1の内部電源生成回路

- 52:第2の内部電源生成回路

- 5 0 0 : データ処理システム

- 5 1 0 : システムバス

- 520:データプロセッサ

- 540:ストレージデバイス

- 5 5 0 : I / O デバイス

- 5 6 0 : R O M

- 600: V D D 端子

- 601: VSS端子

- MRBF:メインリードバッファ

- R、R1、R2、R11、R12:抵抗

- RAMP: リードデータレシーバ (第1のレシーバ)

- R B F : リードデータバッファ

- RLAT:リードデータラッチ

- RWAMP:リードライトアンプの一部

- RWBS:リードライトデータバス(第1の伝送線)

- S 1 、 S 2 : スイッチ

- SA:センスアンプ

- SRBF:サブリードバッファ

- WAMP: ライトデータレシーバ (第2のレシーバ)

- WBF:ライトデータバッファ

- V D D 、 V S S : 電源、電源配線、電源電圧

- V D L 、 V S L : 内部電源、内部電源配線、内部電源電圧

- VREF:基準信号、基準電圧信号、第2の伝送線

- DPS:制御信号

- **VA:ノード**

20

# 【図5】

RAMP(WAMP)

# 【図6】

# 【図7】

# 【図8】

**Q**

# 【図10】

DRACT

DRB

【図17】

【図20】

#### 【手続補正書】

【提出日】平成23年1月21日(2011.1.21)

【手続補正1】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項17

【補正方法】変更

【補正の内容】

【請求項17】

前記複数の第1のドライバがそれぞれ出力する小振幅信号を第1の小振幅信号としたときに、それぞれ、前記複数の第1のレシーバ側に配置され、それぞれ前記第1の電位と前記第2の電位との間で遷移する第2の小振幅信号を低インピーダンスで前記複数の第1の伝送線に出力する複数の第3のドライバと、

前記複数の第1のドライバ側に配置され、前記第1の伝送線及び第2の伝送線に接続された複数の第2のレシーバと、

前記複数の第1のレシーバ側に配置され、前記第2の伝送線へ第1の基準電圧信号と同電位の第2の基準電圧信号を前記第3のドライバより高インピーダンスで出力する第4のドライバと、をさらに備え、

前記第1の電源線及び第2の電源線は、前記第2の伝送線を両側から挟んで、前記第4のドライバ近傍から前記複数の第2のレシーバ近傍まで配線され、

前記複数の第3のトライバ及び第4のドライバを出力ハイインピーダンスとして、前記複数の第1のドライバからそれぞれ前記第1の小振幅信号を前記第1の伝送線に出力し、前記第2のドライバから前記第1の基準電圧信号を前記第2の伝送線に出力し、前記複数の第1のレシーバがそれぞれ前記第1の小振幅信号及び前記第1の基準電圧信号を受信する第1の動作モードと、

前記複数の第1のドライバ及び第2のドライバを出力ハイインピーダンスとして、前記複数の第3のドライバからそれぞれ前記第2の小振幅信号を前記第1の伝送線に出力し、前記第4のドライバから前記第2の基準電圧信号を前記第2の伝送線に出力し、前記複数の第2のレシーバがそれぞれ前記第2の小振幅信号及び前記第2の基準電圧信号を受信する第2の動作モードと、

を有し、さらに、

\_\_前記複数の第1のドライバ側に設けられ、前記第1の電位と前記第2の電位を生成する 第1<u>の内</u>部電源生成回路と、前記複数の第1のレシーバ側に設けられ、前記第1の電位と 前記第2の電位を生成する第2の内部電源生成回路と、を含み、

前記第1の電源線及び第2の電源線は、前記第1の動作モードにおいて前記第2の内部電源生成回路から電気的に切り離されて前記第1の内部電源生成回路に電気的に接続され、前記第2の動作モードにおいて前記第1の内部電源生成回路から電気的に切り離されて前記第2の内部電源生成回路に電気的に接続される、ことを特徴とする<u>請求項6万至15</u>いずれか1項記載の半導体装置。

## 【手続補正2】

【補正対象書類名】特許請求の範囲

【補正対象項目名】請求項21

【補正方法】変更

【補正の内容】

【請求項21】

第1の半導体装置と、

第2の半導体装置と、

前 記 第 1 と 前 記 第 2 の 半 導 体 装 置 と の 間 を 接 続 す る シ ス テ ム バ ス と 、 を 備 え 、

前記第1の半導体装置は、

データ記憶部と、

複数の第1の伝送線と、

一つの第2の伝送線と、

第1の電位と第2の電位との間で遷移する小振幅信号を第1のインピーダンスで生成し、それぞれ対応して接続する前記複数の第1の伝送線の一端に出力する第1の領域に配置された複数の第1のドライバと、

前記第1の電位と第2の電位との中間電位の基準電圧信号を前記第1のインピーダンスより高い第2のインピーダンスで生成し、接続する前記第2の伝送線の一端に出力する前記第1の領域に配置された第2のドライバと、

前記一つの第2の伝送線の他端に接続すると共に、前記複数の第1の伝送線の他端にそれぞれ対応して接続し、前記基準電圧信号と前記小振幅信号をそれぞれ受ける第2の領域に配置された複数の第1のレシーバと、

前記第1の電位を有し、一端が前記第1の領域、他端が前記第2の領域に含まれる第1 の電源線と、

前記第2の電位を有し、一端が前記第1の領域、他端が前記第2の領域に含まれる第2の電源線と、を備え、

前記第2の伝送線は、前記第1と第2の電源線との間に前記複数の第1の伝送線を含むことなく配置され、

前記複数の第1の伝送線は、それぞれ前記第1と第2の電源線の間に配置されることなく、互いに隣接して配置され、

前記<u>第1の半導体装置</u>は、前記<u>第2の半導体装置</u>からの要求に応答して、前記データ記憶部に格納されたデータを前記複数の第1のドライバと、前記複数の第1の伝送線と、前記複数の第1のレシーバと、を介して前記システムバスに出力する、ことを特徴とするデータ処理システム。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0009

【補正方法】変更

【補正の内容】

[0009]

本発明の第3の側面によるデータ処理システムは、第1の半導体装置と、第2の半導体 装 置 と 、 前 記 第 1 と 前 記 第 2 の 半 導 体 装 置 と の 間 を 接 続 す る シ ス テ ム バ ス と 、 を 備 え 、 前 記 第 1 の 半 導 体 装 置 は 、 デ ー タ 記 憶 部 と 、 複 数 の 第 1 の 伝 送 線 と 、 一 つ の 第 2 の 伝 送 線 と 、 第 1 の電位と第 2 の電位との間で遷移する小振幅信号を第 1 のインピーダンスで生成し それぞれ対応して接続する前記複数の第1の伝送線の一端に出力する第1の領域に配置さ れた複数の第1のドライバと、前記第1の電位と第2の電位との中間電位の基準電圧信号 を前記第1のインピーダンスより高い第2のインピーダンスで生成し、接続する前記第2 の伝送線の一端に出力する前記第1の領域に配置された第2のドライバと、前記一つの第 2 の 伝 送 線 の 他 端 に 接 続 す る と 共 に 、 前 記 複 数 の 第 1 の 伝 送 線 の 他 端 に そ れ ぞ れ 対 応 し て 接続し、前記基準電圧信号と前記小振幅信号をそれぞれ受ける第2の領域に配置された複 数 の 第 1 の レ シ ー バ と 、 前 記 第 1 の 電 位 を 有 し 、 一 端 が 前 記 第 1 の 領 域 、 他 端 が 前 記 第 2 の領域に含まれる第1の電源線と、前記第2の電位を有し、一端が前記第1の領域、他端 が前記第2の領域に含まれる第2の電源線と、を備え、前記第2の伝送線は、前記第1と 第 2 の 電 源 線 と の 間 に 前 記 複 数 の 第 1 の 伝 送 線 を 含 む こ と な く 配 置 さ れ 、 前 記 複 数 の 第 1 の伝送線は、それぞれ前記第1と第2の電源線の間に配置されることなく、互いに隣接し て配置され、前記第1の半導体装置は、前記第2の半導体装置からの要求に応答して、前 記 デ ー タ 記 憶 部 に 格 納 さ れ た デ ー タ を 前 記 複 数 の 第 1 の ド ラ イ バ と 、 前 記 複 数 の 第 1 の 伝 送 線 と 、 前 記 複 数 の 第 1 の レ シ ー バ と 、 を 介 し て 前 記 シ ス テ ム バ ス に 出 力 す る 。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0012

【補正方法】変更

#### 【補正の内容】

- [0012]

- 【図1】本発明の実施例1による半導体装置全体のブロック図である。

- 【図2】実施例1による半導体装置におけるメモリセルアレイとデータ入出力端子とのインタフェース部分全体のブロック図である。

- 【図3】実施例1による半導体装置における内部回路側と外部端子側のデータ伝送回路の回路ブロック図である。

- 【図4】実施例1における内部電源生成回路のブロック図である。

- 【図5】実施例1におけるデータレシーバの回路ブロック図である。

- 【図6】実施例1において好ましいレイアウト配置を説明する図面である。

- 【図7】実施例1において、(a)は内部回路側から外部端子側にデータを出力(リード動作)するときのドライバ回路の状態を説明する図であり、(b)は外部端子側から内部回路側にデータを入力(ライト動作)するときのドライバ回路の状態を説明する図である

- 【図8】実施例1において、(a)はリード動作時の基準電圧ドライバの状態を説明する図であり、(b)はライト動作時の基準電圧ドライバの状態を説明する図である。

- 【図9】実施例2において、(a)はリード動作時の基準電圧ドライバの状態を説明する図であり、(b)はライト動作時の基準電圧ドライバの状態を説明する図である。

- 【図10】実施例3において、(a)リード動作時の内部電源線及び基準電圧伝送線の状態と、<u>(b)</u>ライト動作時の内部電源線及び基準電圧伝送線の状態と、を説明する図である。

- 【図11】内部電源VSLが変動した場合の(a)実施例2における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。

- 【図12】内部電源 V D L が変動した場合の(a)実施例 2 における伝送線のシミュレーション波形図と、(b)比較例における伝送線のシミュレーション波形図である。

- 【図13】実施例4におけるデータバッファの回路ブロック図である。

- 【図14】実施例4におけるデータバッファの動作波形図である。

- 【図15】実施例4におけるデータレシーバの回路ブロック図である。

- 【図16】実施例4におけるデータレシーバの動作波形図である。

- 【図17】データ処理システムの実施例のブロック図である。

- 【図18】実施例5によるデータバッファの回路ブロック図である。

- 【図19】実施例5によるデータバッファの動作波形図である。

- 【図20】実施例1に対する比較例の動作を説明する図である。

- 【手続補正5】

- 【補正対象書類名】明細書

- 【補正対象項目名】0020

- 【補正方法】変更

- 【補正の内容】

- [0020]

また、リードライトアンプ31、内部回路側入出力回路33は、Bank0~Bank7の8つのメモリセルアレイ10毎にメモリセルアレイ10の外に設けられる。リードライトアンプ31は、リードコマンド実行時には、センスアンプ12、カラムセレクタ13、<u>I/O線62</u>を介してメモリセルアレイ10の外に読み出されたメモリセルのデータをセンシングする。また、ライトコマンド実行時には、外部I/O端子22から外部端子側入出力回路36、リードライトデータバスRWBS、内部回路側入出力回路33を経由して入力されたライトデータをメモリセルアレイ10に対して書込みを行う。

#### 【手続補正6】

- 【補正対象書類名】明細書

- 【補正対象項目名】0022

- 【補正方法】変更

#### 【補正の内容】

## [0022]

リードライトデータバス(第1の伝送線)RWBSは、各メモリセルアレイ10と各外部 I / O端子 2 2 との間を接続する並列データバスである。後で詳しく説明するように、このリードライトデータバスRWBSは、小振幅の信号を伝送するバスであり、小振幅信号のハイレベル、ロウレベルの判定基準となる基準電圧信号(第2の伝送線)VREFが、小振幅信号の電源となる内部電源線VDLとVSLに挟まれて内部回路側入出力回路33と外部端子側入出力回路36との間に配線されている。なお、リードライトデータバスRWBSが複数のビットのバスであるに対して、基準電圧信号VREFは、1本の信号線(第2の伝送線)である。内部電源線VDLとVSLは、内部電源VDL、VSLを生成する内部電源生成回路50で生成される。一例として、内部電源線VDLとVSLは、半導体装置1の外部端子である高電位側のVDD端子600、低電位側のVSS601から供給される。

## 【手続補正7】

【補正対象書類名】明細書

【補正対象項目名】0024

【補正方法】変更

【補正の内容】

[0024]

ライトデータとリードデータの入出力端子である外部 I / O端子 2 2 は、図 1 では代表して 1 端子しか記載していないが、 D D R 等の同期式 D R A M では、一般的に、 4 端子から 1 6 端子である。ライト動作時には、 4 ~ 1 6 本の外部 I / O端子 2 2 から直列に入力されたデータは、外部端子側入出力回路 3 6 により、 8 ~ 1 2 8 ビットの並列データに変換され、リードライトデータバス R W B S を介して該当するバンクの内部側入出力回路に転送され、メモリセルアレイ 1 0 へ書込まれる。リード動作時には、 8 ~ 1 2 8 ビットの並列データとしてリードライトデータバス R W B S を介して外部端子側入出力回路に 3 6 により直列データに変換され、 4 ~ 1 6 本の外部 I / O端子から出力する。なお、リードライトデータバス R W B S のビット数は、 4 本の外部 I / O端子から入出力するデータを 2 ビット並列に転送する場合は、 5 を並列に転送する場合は、 1 2 8 ビットである。

## 【手続補正8】

【補正対象書類名】明細書

【補正対象項目名】0025

【補正方法】変更

【補正の内容】

[ 0 0 2 5 ]

図 2 は、実施例 1 による半導体装置におけるメモリセルアレイ 1 0 と外部 I / 0 端子 2 2 とのインタフェース部分全体のブロック図である。ただし、図 2 では、 8 個のメモリセルアレイ 1 0 のうち、 3 個のメモリセルアレイのみ図示し、他のメモリセルアレイ 1 0 の記載は省略している。また、図 2 では、 4 ~ 1 6 端子の外部 I / 0 端子 2 2 のうち、 1 端子のみを図示し、他の外部 I / 0 端子 2 2 の図示も省略している。

【手続補正9】

【補正対象書類名】明細書

【補正対象項目名】0026

【補正方法】変更

【補正の内容】

[0026]

図 2 において、メモリセルアレイ 1 0 は、 1 バンクのメモリセルアレイが配置される領域を示している。 1 バンクのメモリセルアレイ 1 0 は、複数の部分領域 1 0 - 1 に分かれ

て配置され、部分領域10-1毎にセンスアンプSAをまとめて配置したセンスアンプ列12-1が設けられている。ビット線BLT、<u>BLB</u>は、センスアンプSAを介してローカルIO線LIOT、LIOBに接続されている。さらに、ローカルIO線LIOT、LIOBは、リードライトゲート13-1を介してメインIO線MIOT、MIOBに接続され、メインIO線MIOT、MIOBは、リードライトアンプRWAMP(図1の31に相当)へと接続されている。なお、1バンクのメモリセルアレイ10には、多数の部分領域10-1がマトリクス状に複数設けられ、各部分領域にそれぞれ対応してセンスアンプ列12-1とローカルIO線LIOT、LIOBがそれぞれ設けられている。また、図2では、メインIO線MIOT、MIOBは1対しか記載していないが各メモリセルアレイ10内には、多数のメインIO線対MIOT、MIOBが設けられ、各メインIO線対MIOT、MIOBに対応して複数のリードライトアンプRWAMPが設けられている。

【手続補正10】

【補正対象書類名】明細書

【補正対象項目名】0027

【補正方法】変更

【補正の内容】

[0027]

内部回路側入出力回路33は、リードデータバッファRBFと、ライトデータラッチWLATと、ライトデータレシーバWAMPを含んで構成される。リードデータバッファRBFは、リードライトアンプRWAMPから読み出したリードデータを一時的に保存するラッチ回路と、ラッチ回路が保持するデータをリードライトデータバスRWBSへ小振幅信号として出力するドライブ回路を備えている。ライトデータアンプ(第2のレシーバ)WAMPは、ライトコマンド実行時にリードライトデータバスRWBSの小振幅信号をセンシングする。なお、ライトデータアンプWAMPには、基準電圧信号VREFも接続される。ライトデータラッチWLATは、ライトコマンド実行時にライトデータアンプWAMPがセンシングしたデータをメモリセルアレイ10に書き込むまで一時的に保持するラッチである。なお、内部回路側入出力回路33は、各リードライトアンプRWAMPに対応してバンク毎に複数設けられる。

【手続補正11】

【補正対象書類名】明細書

【補正対象項目名】0036

【補正方法】変更

【補正の内容】

[ 0 0 3 6 ]

なお、リードデータバッファRBF内の回路のうち、NAND回路334の高電位側電源端子は内部電源VDLに接続され、低電位側電源端子は電源VSSに接続されている。また、NOR回路の高電位側電源端子は電源VDDに接続され、低電位側電源端子は電源VSLに接続されている。また、バッファ回路を構成するPチャンネルMOSトランジスタ337のソースは、内部電源VDLに接続され、NチャンネルMOSトランジスタ337のソースは、内部電源VSLに接続されている。なお、高電位側の内部電源VDL」は、高電位側電源VDD以下の電圧の半導体装置1の内部で生成した電源であり、低電位側の内部電源VSLは、低電位側電源VSS以上の電圧の半導体装置1の内部で生成した電源電圧である。なお、高電位側電源VDD、高電位側内部電源VDL、低電位側内部電源VDL、低電位側電源VSSの電位を示すと式(1)のとおりである。

【手続補正12】

【補正対象書類名】明細書

【補正対象項目名】0047

【補正方法】変更

【補正の内容】

[0047]

また、NAND回路364の低電位側の電源をVSS、NOR回路365の高電位側の電源をVDDから取っているので、VDLとVSL間の電位差が小さくても、VDLとVSLとの電位差が、それぞれ、PチャンネルMOSトランジスタ366のトランジスタ閾値、NチャンネルMOSトランジスタ367のトランジスタ閾値を超える電圧であれば、PチャンネルMOSトランジスタ366とNチャンネルMOSトランジスタ367からなる第3のドライバは動作する。したがって、リードライトデータバスRWBSを伝送する信号を小振幅にすることが可能である。

【手続補正13】

【補正対象書類名】明細書

【補正対象項目名】0051

【補正方法】変更

【補正の内容】

[0051]

一方、各第1の伝送線RWBSは、信号の伝播が内部電源配線VDL及び内部電源配線VSLに影響を与えないように、内部電源配線VDL及びVSLから離間して配線されている。 第1の伝送線RWBSと内部電源配線VDL及びVSLとの距離は、第1の伝送線RWBSの小振幅信号の伝送が配線間容量や相互インダクタンスにより内部電源配線VDLとVSLの電位に大きな影響を与えないように離せば十分である。

【手続補正14】

【補正対象書類名】明細書

【補正対象項目名】0070

【補正方法】変更

【補正の内容】

[ 0 0 7 0 ]

また、図9(b)に示すように、外部端子側から内部回路側にデータを転送(ライトデータ入力)するときには、スイッチ421と422をオンにして、スイッチ411と412をオフにしている。この様に設定することにより、内部回路側基準電圧ドライバ41aの出力をハイインピーダンスにするだけにとどまらず、内部回路側基準電圧ドライバの内部電源端子VDL1、VSL1を内部電源配線VDL、VSLから切り離している。一方、基準電圧ドライバ42aの内部電源端子VDL2、VSL2は、スイッチ421、422を介して内部電源配線VDL、VSLに接続されている。従って、電源配線VDL、VSLは、より忠実にデータを出力する側(外部端子側)の内部電源電圧VDL2、VSL2を反映した電圧となり、電源配線VDL、VSLと基準電圧信号VREFとの配線間容イバ回路の内部電源電圧VDL2、VSL2を反映した電圧とすることができる。

【手続補正15】

【補正対象書類名】明細書

【補正対象項目名】0093

【補正方法】変更

【補正の内容】

[0093]

実施例3は、第2の伝送線VREFを挟むように配置された内部電源配線VDL、VSLとその外側にさらに配線される電位が変動する駆動配線との間にVSSやVDD等の固定電位に接続された配線を設けることにより、駆動配線の伝送する信号の電圧レベルの変動が、第2の伝送線VREFや内部電源配線VDL、VSLに影響を与えないようにする実施例である。第2の伝送線VREFを駆動する第2のドライバ41、第4のドライバ42は、出力インピーダンスが比較的高いのでノイズの影響を受けやすい。第2の伝送線VREFの両側を内部電源配線VDL、VSLで挟んでもさらに内部電源配線VDL、VSLの外側に配置された信号配線の電位が変動するとその影響を内部電源配線VDL、VSLの電位が変動し、さらにその内部電源配線VD

L、VSLの揺れが第2の伝送線VREFの電位に影響を与える。データを出力する第1のドライバ(図3の336、337)、第3のドライバ(図3の366、367)の内部電源VDL、VSLの揺らぎと連動して第2の伝送線VREFの電位が変動することは、好ましいが、データを出力する第1、第3のドライバの電源電位の変動に基づかない内部電源配線VDL、VSLの揺らぎによる第2の伝送線VREFの揺らぎは誤動作を生じさせる恐れがある。実施例3では、第2の伝送線VREFを挟んで配置された内部電源配線VDL、VSLとノイズとなる信号配線(駆動配線)との間に固定電位に接続された配線を配置することにより、ノイズとなる信号配線が配線間の寄生容量や配線間の相互インダクタンス等により悪影響を与えることを防いでいる。

【手続補正16】

【補正対象書類名】明細書

【補正対象項目名】0094

【補正方法】変更

【補正の内容】

[0094]

図10は、実施例3において、(a)リード動作時(内部回路側から外部端子側へのデータ出力時)の内部電源線VDL、VSL及び基準電圧伝送線(第2の伝送線)VREFのノイズの影響と、(b)ライト動作時(外部端子側から内部回路側へのデータ入力時)の内部電源線及び基準電圧伝送線のノイズの影響と、を説明する図である。

【手続補正17】

【補正対象書類名】明細書

【補正対象項目名】0107

【補正方法】変更

【補正の内容】

[ 0 1 0 7 ]

図16は、図15のデータレシーバの動作波形図である。制御信号DRACTは、ドライバ側を制御する信号であり、DRINは、ドライバ側が出力するデータ信号である。また、RLATは、図13の<u>RLATINB</u>の反転信号であり、DRINは、<u>RLAT</u>の立ち上がりに同期してデータが更新される。DRACTがハイレベルに立ち上がると、第1の伝送線には、データ信号DRINに基づいた小振幅信号が出力される。データレシーバは、制御信号DRACTの立ち上がりに同期して制御信号DREAを活性化し、差動回路への電流の供給を開始する。

【手続補正18】

【補正対象書類名】明細書

【補正対象項目名】0119

【補正方法】変更

【補正の内容】

[0119]

図17は、半導体装置1を用いたデータ処理システムのブロック図である。図に示すデータ処理システム500は、データプロセッサ520と、半導体装置(DRAM)1が、システムバス510を介して相互に接続されている。データプロセッサ520としては、例えば、マイクロプロセッサ(MPU)、デジタルシグナルプロセッサ(DSP)などを含むが、これらに限定されない。図17においては説明を簡単にするため、システムバス510を介してデータプロセッサ520と<u>DRAM1</u>とが接続されているが、システムバス510を介さずにローカルなバスによってこれらが接続されていても構わない。

【手続補正19】

【補正対象書類名】明細書

【補正対象項目名】0124

【補正方法】変更

【補正の内容】

#### [0124]

実施例6において、DRAMを制御するコントローラ(例えばデータプロセッサ520)は、システムクロックCK,CKBとその他の制御信号を利用して<u>DRAM1</u>へデータのリードアクセスやライトアクセスに関連する各種コマンドを発行する。コントローラからリードコマンドを受けた半導体装置1は、内部に保持する記憶情報を読み出し、第1の伝送線RWBS(図1)を経由してシステムバス510へそのデータを出力する。また、コントローラからライトコマンドを受けた半導体装置1は、システムバス510から入力したデータを第1の伝送線RWBSを経由してメモリセルアレイ10にデータを書き込む。尚、コントローラが発行する前記複数のコマンドは、所謂、周知の半導体装置を制御する業界団体(JEDEC(Joint E1ectron Device Engineering Counci1) Solid State Technology Association)で規定されるコマンド(システムとしてのコマンド)である。

#### 【手続補正20】

【補正対象書類名】明細書

【補正対象項目名】0125

【補正方法】変更

【補正の内容】

[0125]

また、実施例6において、<u>DRAM1</u>だけでなく、ストレージデバイス540、I/Oデバイス550、ROM560も、内部データの伝送に、実施例1乃至実施例5で説明した第1の伝送線RWBSと第2の伝送線VREFを用いた半導体装置とすることができる。データプロセッサからの要求に応答して各チップの内部において、高速、かつ、低消費電力にデータの入出力を行うことができる。

【手続補正21】

【補正対象書類名】図面

【補正対象項目名】図1

【補正方法】変更

【補正の内容】

【図1】