## (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 111063306 A (43)申请公布日 2020.04.24

(21)申请号 201911290363.2

(22)申请日 2019.12.16

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明 街道塘明大道9-2号

(72)发明人 刘世奇

(74)专利代理机构 深圳紫藤知识产权代理有限 公司 44570

代理人 远明

(51) Int.CI.

**G09G** 3/3233(2016.01)

权利要求书2页 说明书4页 附图2页

#### (54)发明名称

一种像素电路及其驱动方法、显示面板

#### (57)摘要

本发明提供一种像素电路及其驱动方法、显示面板,所述像素电路为7T1C的结构,其包括第一晶体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第五晶体管(T5)、第一发光元件(R)以及存储电容(Cst)。本发明的技术效果在于,提供一种像素电路及其驱动方法、显示面板,在提高分辨率的同时,无需减少每个像素电路的空间,从而解决了电路结构复杂、制作工艺复杂的技术问题,有利于提高显示面板的显示效果。

1.一种像素电路,其特征在于,包括:

第一晶体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第五晶体管(T5)、第一发光元件(R)以及存储电容(Cst);

所述第一晶体管 (T1) 的漏极连接所述电源电压 (Vdd),所述第一晶体管 (T1) 的源极连接所述存储电容 (Cst) 的第二端,所述第一晶体管 (T1) 的栅极连接所述第二晶体管 (T2) 的漏极:

所述第二晶体管 (T2) 的源极连接数据线 (Data),所述第二晶体管 (T2) 的漏极连接所述存储电容 (Cst) 的第一端,所述第二晶体管 (T2) 的栅极连接扫描线 (Scan);

所述第三晶体管(T3)的源极连接所述第一晶体管(T1)的源极,所述第三晶体管(T3)的漏极连接感测线(Sense),所述第三晶体管(T3)的栅极连接所述扫描线(Scan);

所述第五晶体管 (T5) 的漏极连接所述第三晶体管 (T3) 的源极,所述第五晶体管 (T5) 的漏极连接所述第一发光元件 (R) 的阳极,所述第五晶体管 (T5) 的栅极连接第一发光数据线 (Data R):

所述第一发光元件(R)的阴极连接参考电位(Vss)。

2. 如权利要求1所述的像素电路,其特征在于,还包括

第四晶体管(T4),所述第四晶体管(T4)的源极连接感测线(Sense),所述第四晶体管(T4)的漏极连接复位线,所述第四晶体管(T4)的栅极连接读取信号线。

3. 如权利要求2所述的像素电路,其特征在于,还包括

所述第六晶体管 (T6) 的漏极连接所述第三晶体管 (T3) 的源极,所述第六晶体管 (T6) 的漏极连接所述第二发光元件 (G) 的阳极,所述第六晶体管 (T6) 的栅极连接第二发光数据线 (Data G);

所述第二发光元件(G)的阴极连接参考电位(Vss)。

4. 如权利要求3所述的像素电路,其特征在于,还包括

所述第七晶体管(T7)的漏极连接所述第三晶体管(T3)的源极,所述第七晶体管(T7)的漏极连接所述第三发光元件(B)的阳极,所述第七晶体管(T7)的栅极连接第三发光数据线(Data B);

所述第三发光元件(B)的阴极连接参考电位(Vss)。

5. 如权利要求4所述的像素电路,其特征在于,

所述第四晶体管 (T4) 用以防止所述第五晶体管 (T5)、所述第六晶体管 (T6)、所述第七晶体管 (T7) 的源极电压漏流至所述感测线 (Sense) 上。

6. 如权利要求1所述的像素电路,其特征在于,

所述第一晶体管(T1)用以提供恒定的驱动电流。

7.一种包括如权利要求1-6中任一项所述的像素电路驱动方法,其特征在于,包括如下步骤:

在第一阶段,向所述扫描线(Scan)输入高电平信号,所述数据线(Data)输入高电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第一届体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第四晶体管(T4)导通,所述存储电容(Cst)充电;

在第二阶段,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入高电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第五晶体管(T5)导通,控制第一发光元件(R)发光,获取所述第五晶体管(T5)的阈值电压:

在第三阶段,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第六晶体管(T6)导通,控制第二发光元件(G)发光,获取所述第六晶体管(T6)的阈值电压;

在第四阶段,向所述扫描线(Scan)输入低电平信号,所述数据线输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data G)输入低电平信号,所述第三发光数据线(Data B)输入高电平信号,所述第四晶体管(T4)、第七晶体管(T7)导通,控制第三发光元件(B)发光,获取所述第七晶体管(T7)的阈值电压。

- 8. 如权利要求7所述的所述的像素电路驱动方法,其特征在于, 所述存储电容(Cst)充电调控所述第一晶体管(T1)的供给电流的大小。

- 9. 如权利要求7所述的所述的像素电路驱动方法,其特征在于,

在所述在第一阶段,利用所述第三晶体管(T3)的打开和关闭,所述感测线(Sense)用以监控所述第一晶体管(T1)、所述第五晶体管(T5)、所述第六晶体管(T6)以及所述第七晶体管(T7)的状态。

10.一种显示面板,包括如权利要求1-6中任一项所述的像素电路。

## 一种像素电路及其驱动方法、显示面板

#### 技术领域

[0001] 本发明涉及显示技术领域,特别是涉及一种像素电路及其驱动方法、显示面板。

#### 背景技术

[0002] 随着显示面板的发展,人们追求更大屏幕,对高清显示的需求,集成电路及显示行业不断发展和创新。各类高分辨率的显示屏纷纷占据各大终端品牌,AMOLED (Activematrix organic lightemitting diode,有源矩阵有机发光二极体或主动矩阵有机发光二极体)产品也是其中的一员。

[0003] 在显示面板的尺寸固定的情况下,随着分辨率的提升,每个像素电路需要的空间就越少,如压缩走线的线宽或者存储电容(Cst)等元器件占用空间等,从而导致电路结构复杂,制作工艺复杂的技术问题。

### 发明内容

[0004] 本发明的目的在于,提供一种像素电路及其驱动方法、显示面板,以解决现有存在的显示面板的像素电路空间受限,电路结构复杂,制作工艺复杂的技术问题。

[0005] 为实现上述目的,本发明提供一种像素电路,其为7T1C的结构,包括第一晶体管 (T1)、第二晶体管 (T2)、第三晶体管 (T3)、第五晶体管 (T5)、第一发光元件 (R)以及存储电容 (Cst);所述第一晶体管 (T1)的漏极连接所述电源电压 (Vdd),所述第一晶体管 (T1)的源极连接所述存储电容 (Cst)的第二端,所述第一晶体管 (T1)的栅极连接所述第二晶体管 (T2)的漏极连接数据线 (Data),所述第二晶体管 (T2)的漏极连接 所述存储电容 (Cst)的第一端,所述第二晶体管 (T2)的栅极连接扫描线 (Scan);所述第三晶体管 (T3)的源极连接所述第一晶体管 (T1)的源极,所述第三晶体管 (T3)的源极连接感测线 (Sense),所述第三晶体管 (T3)的栅极连接所述扫描线 (Scan);所述第五晶体管 (T5)的漏极连接所述第三晶体管 (T5)的漏极连接所述第一届体管 (T5)的漏极连接所述第三晶体管 (T5)的漏极连接所述第一人光元件 (R)的阳极,所述第五晶体管 (T5)的栅极连接第一发光数据线 (Data R);所述第一发光元件 (R)的阳极连接参考电位 (Vss)。

[0006] 进一步地,所述像素电路还包括第四晶体管(T4),所述第四晶体管(T4)的源极连接感测线(Sense),所述第四晶体管(T4)的漏极连接复位线,所述第四晶体管(T4)的栅极连接读取信号线。

[0007] 进一步地,所述像素电路还包括所述第六晶体管(T6)的漏极连接所述第三晶体管(T3)的源极,所述第六晶体管(T6)的漏极连接所述第二发光元件(G)的阳极,所述第六晶体管(T6)的栅极连接第二发光数据线(Data G);所述第二发光元件(G)的阴极连接参考电位(Vss)。

[0008] 进一步地,所述像素电路还包括所述第七晶体管(T7)的漏极连接所述第三晶体管(T3)的源极,所述第七晶体管(T7)的漏极连接所述第三发光元件(B)的阳极,所述第七晶体管(T7)的栅极连接第三发光数据线(Data B);所述第三发光元件(B)的阴极连接参考电位

$(V_{SS})$  .

[0009] 进一步地,所述第四晶体管(T4)用以防止所述第五晶体管(T5)、所述第六晶体管(T6)、所述第七晶体管(T7)的源极电压漏流至所述感测线(Sense)上。

[0010] 进一步地,所述第一晶体管(T1)用以提供恒定的驱动电流。

[0011] 一种像素电路驱动方法,包括前文所述的像素电路,包括如下步骤:

[0012] 在第一阶段,向所述扫描线(Scan)输入高电平信号,所述数据线输入高电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data G)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第一届体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第四晶体管(T4)导通,所述存储电容(Cst)充电;

[0013] 在第二阶段,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入高电平信号,所述第二发光数据线(Data G)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第五晶体管(T5)导通,控制第一发光元件(R)发光,获取所述第五晶体管(T5)的阈值电压;

[0014] 在第三阶段,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data G)输入高电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第六晶体管(T6)导通,控制第二发光元件(G)发光,获取所述第六晶体管(T6)的阈值电压;

[0015] 在第四阶段,向所述扫描线(Scan)输入低电平信号,所述数据线输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data G)输入低电平信号,所述第三发光数据线(Data B)输入高电平信号,所述第四晶体管(T4)、第七晶体管(T7)导通,控制第三发光元件(B)发光,获取所述第七晶体管(T7)第三阈值电压。

[0016] 进一步地,所述存储电容(Cst)充电调控所述第一晶体管(T1)的供给电流大小。

[0017] 进一步地,在所述在第一阶段,利用所述第三晶体管(T3)的打开和关闭,所述感测线(Sense)用以监控所述第一晶体管(T1)、所述第五晶体管(T5)、所述第六晶体管(T6)以及所述第七晶体管(T7)的状态。

[0018] 一种显示面板,包括如前文所述的像素电路。

[0019] 本发明的技术效果在于提供一种像素电路及其驱动方法、显示面板,在提高分辨率的同时,无需减少每个像素电路的空间,从而解决了电路结构复杂、制作工艺复杂的技术问题,有利于提高显示面板的显示效果。

#### 附图说明

[0020] 为了更清楚地说明本发明实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

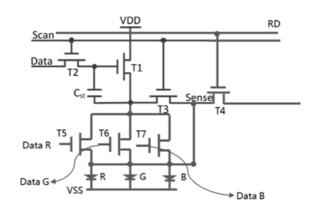

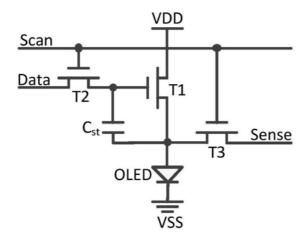

[0021] 图1为本实施例所述像素电路的电路示意图;

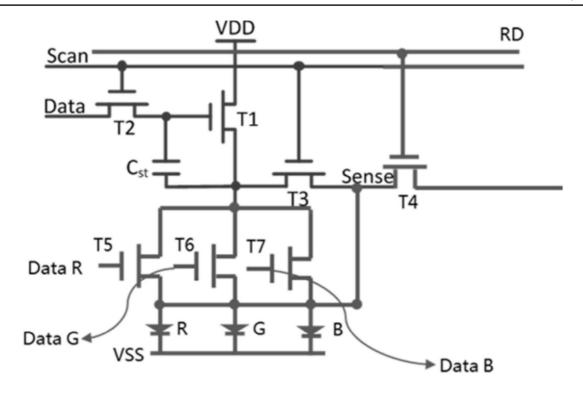

[0022] 图2为本实施例所述像素电路的的信号时序示意图;

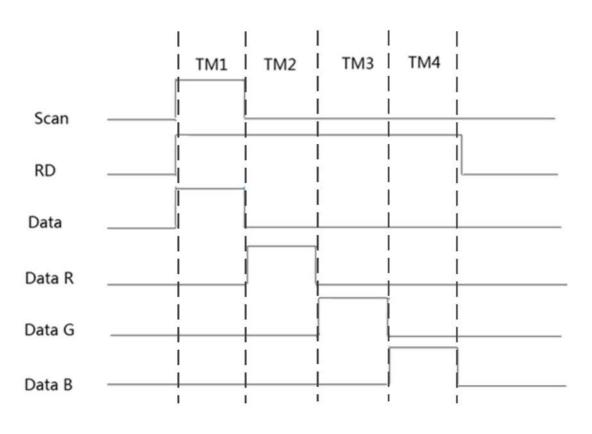

[0023] 图3为现有技术所述像素电路的电路示意图。

#### 具体实施方式

[0024] 以下参考说明书附图介绍本发明的优选实施例,用以举例证明本发明可以实施, 这些实施例可以向本领域中的技术人员完整介绍本发明的技术内容,使得本发明的技术内 容更加清楚和便于理解。然而本发明可以通过许多不同形式的实施例来得以体现,本发明 的保护范围并非仅限于文中提到的实施例。

[0025] 本实施例提供一种显示面板,所述显示面板优选为AMOLED面板,其中所述显示面板包括像素电路。

[0026] 如图1所示,本实施例提供一种像素电路,包括第一晶体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第四晶体管(T4)、第五晶体管(T5)、第六晶体管(T6)、第七晶体管(T7)、第一发光元件(R)以及存储电容(Cst)。

[0027] 第一晶体管 (T1) 的漏极连接所述电源电压 (Vdd),第一晶体管 (T1) 的源极连接存储电容 (Cst) 的第二端,第一晶体管 (T1) 的栅极连接第二晶体管 (T2) 的漏极。其中,第一晶体管 (T1) 用以提供恒定的驱动电流。

[0028] 第二晶体管 (T2) 的源极连接数据线 (Data),第二晶体管 (T2) 的漏极连接存储电容 (Cst) 的第一端,第二晶体管 (T2) 的栅极连接扫描线 (Scan)。

[0029] 第三晶体管 (T3) 的源极连接所述第一晶体管 (T1) 的源极,所述第三晶体管 (T3) 的漏极连接感测线 (Sense),第三晶体管 (T3) 的栅极连接所述扫描线 (Scan)。

[0030] 第五晶体管 (T5) 的漏极连接第三晶体管 (T3) 的源极,第五晶体管 (T5) 的漏极连接第一发光元件 (R) 的阳极,第五晶体管 (T5) 的栅极连接第一发光数据线 (Data R);所述第一发光元件 (R) 的阴极连接参考电位 (Vss)。

[0031] 第四晶体管 (T4) 的源极连接感测线 (Sense),第四晶体管 (T4) 的漏极连接复位线, 第四晶体管 (T4) 的栅极连接读取信号线。

[0032] 第六晶体管 (T6)的漏极连接第三晶体管 (T3)的源极,第六晶体管 (T6)的漏极连接第二发光元件 (G)的阳极,第六晶体管 (T6)的栅极连接第二发光数据线 (Data G);所述第二发光元件 (G)的阴极连接参考电位 (Vss)。

[0033] 第七晶体管 (T7)的漏极连接第三晶体管 (T3)的源极,第七晶体管 (T7)的漏极连接第三发光元件 (B)的阳极,第七晶体管 (T7)的栅极连接第三发光数据线 (Data B);第三发光元件 (B)的阴极连接参考电位 (Vss)。

[0034] 本实施例中,第四晶体管(T4)用以防止第五晶体管(T5)、第六晶体管(T6)、第七晶体管(T7)的源极电压漏流至所述感测线(Sense)上。例如,当第一发光元件(R)、所述第二发光元件(G)、第三发光元件(B)不工作时,第四晶体管(T4)侦测第五晶体管(T5)、第六晶体管(T6)、第七晶体管(T7)的阈值电压;当第一发光元件(R)、所述第二发光元件(G)、第三发光元件(B)工作时,第四晶体管(T4)不侦测第五晶体管(T5)、第六晶体管(T6)、第七晶体管(T7)的阈值电压。

[0035] 如图2所示,所述像素电路驱动方法,包括前文所述的像素电路,其包括如下步骤:

[0036] 在第一阶段TM1,扫描线(Scan)输入高电平信号,所述数据线(Data)输入高电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第一届体管(T1)、第二晶体管(T2)、第三晶体管(T3)、第四晶体管(T4)导通,存储电容(Cst)充电,调控所述第一晶体管(T1)的供给电流大小。在所述第一阶段TM1,利用所述第三晶体管(T3)的打开和关闭,所述感测线(Sense)用以监控所述第一晶体管(T1)、所述第五晶体管(T5)、所述第六晶体管(T6)以及所述第七晶体管(T7)的状态。

[0037] 在第二阶段TM2,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入高电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第三发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第五晶体管(T5)导通,控制第一发光元件(R)发光,获取所述第五晶体管(T5)的源极电压,所述第五晶体管(T5)的源极电压为第五晶体管(T5)的阈值电压。

[0038] 在第三阶段TM3,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第二发光数据线(Data B)输入低电平信号,所述第四晶体管(T4)、第六晶体管(T6)导通,控制第二发光元件(G)发光,获取第六晶体管(T6)的源极电压为第六晶体管(T6)的阈值电压。

[0039] 在第四阶段TM4,向所述扫描线(Scan)输入低电平信号,所述数据线(Data)输入低电平信号,所述读取信号线输入高电平信号,所述第一发光数据线(Data R)输入低电平信号,所述第二发光数据线(Data B)输入高电平信号,所述第二发光数据线(Data B)输入高电平信号,所述第四晶体管(T4)、第七晶体管(T7)导通,控制第三发光元件(B)发光,获取第七晶体管(T7)的源极电压为第七晶体管(T7)的阈值电压。

[0040] 本实施例中,利用第五晶体管(T5)的阈值电压、第六晶体管(T6)的阈值电压、第七晶体管(T7)的阈值电压补偿显示面板显示画面的分布不均的状态。

[0041] 本实施例提供一种像素电路的驱动方法,向扫描线(Scan)、数据线(Data)以及感测线(Sense)置入高电平,通过第一发光数据线(Data R)、第二发光数据线(Data G)、第三发光数据线(Data B)获取不同的阈值电压,并将阈值电压加到相应的像素中,然后依画面亮度的需求选取不同电压来点亮像素,从而使显示面板具有良好的显示效果。

[0042] 如图3所示,现有技术中,利用3个薄膜晶体管和一个电容驱动一个0LED发光。若需同时驱动R、G、B三个子像素发光时,则需要利用九个薄膜晶体管和三个电容的像素电路驱动R、G、B三个子像素发光,该电路简称为9T3C像素电路。然而,本实施例提供的像素电路,利用7T-1C像素电路驱动R、G、B三个子像素发光。与现有技术的9T3C像素电路相比,节省了两个薄膜晶体管和两个电容。因此,在一显示面板的尺寸固定的情况下,在提高分辨率的同时,无需减少每个像素电路的空间,从而避免了电路结构复杂、制作工艺复杂的技术问题,有利于提高显示面板的显示效果。

[0043] 以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

图1

图2

图3