(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5325995号 (P5325995)

(45) 発行日 平成25年10月23日(2013.10.23)

(24) 登録日 平成25年7月26日 (2013.7.26)

(51) Int.Cl.

G 1 1 C 11/413 (2006.01)

G 1 1 C 11/34

FL

K

請求項の数 10 (全 12 頁)

(21) 出願番号 特願2011-542285 (P2011-542285) (86) (22) 出願日 平成21年12月11日 (2009.12.11) (65) 公表番号 特表2012-513073 (P2012-513073A) (43) 公表日 平成24年6月7日 (2012.6.7) (86) 国際出願番号 PCT/US2009/067663 (87) 国際企閱番号 W02010/080342

(87) 国際公開番号 W02010/080342 (87) 国際公開日 平成22年7月15日 (2010.7.15) 審査請求日 平成24年11月6日 (2012.11.6)

(31) 優先権主張番号 12/340,022

(32) 優先日 平成20年12月19日 (2008.12.19)

(33) 優先権主張国 米国 (US)

|(73)特許権者 503161132

インテル・コーポレーション

アメリカ合衆国・カリフォルニア・95054・サンタ・クララ・ミッション・カレ

ッジ・ブールヴァード・2200

|(74)代理人 110000028

特許業務法人明成国際特許事務所

||(72) 発明者 ダーマ・ジョナサン

アメリカ合衆国 カリフォルニア州911 06 パサディナ,ノース・マー・ビスタ ・アベニュー,55,アパートメント 3

2

最終頁に続く

(54) 【発明の名称】偽性デュアルポート型SRAM

### (57)【特許請求の範囲】

### 【請求項1】

メモリであって、

複数の単ポート型記憶装置(メモリバンク)から成り、各記憶装置は第一数のエントリを有するものである主メモリと、

該単ポート型記憶装置の中の異なるものから同時に読み書き操作を可能とするように構成された並列バスと、

該第一数のエントリを備える側帯メモリであって、該側帯メモリ内の各エントリは該主メモリ内の記憶装置の一つの中の対応するエントリにマッピングされ、該側帯メモリはサイクル毎に該側帯メモリへ並列読み書きアクセスが可能であるように構成されたものである側帯メモリと、

該主メモリあるいは該側帯メモリへ読み書き操作を導くように構成されたスイッチ回路 と、

該主メモリの中のどの記憶装置に該側帯メモリ内の各エントリが対応するか追跡し、メモリアドレス情報に応じて決定論的に該スイッチ回路を制御して該メモリが完全に供給されたデュアルポート型メモリのように機能するように該主メモリと該側帯メモリへのアクセスパタンを実施するように構成された制御論理とを備える、メモリ。

### 【請求項2】

該主メモリ内の記憶装置の各々が複数の単ポート型トランジスタ 6 個型( 6 T )スタティックランダムアクセスメモリ( S R A M )セルを備えるものである、請求項 1 に記載の

メモリ。

### 【請求項3】

該側帯メモリがデュアルポート型アレイを備えるものである、請求項1に記載のメモリ

### 【請求項4】

該デュアルポート型アレイが複数のデュアルポート型スタティックランダムアクセスメモリ(SRAM)セルを備え、該SRAMセルがトランジスタ10個型(10T)SRAMセル又はトランジスタ8個型(8T)SRAMセルである、 請求項3に記載のメモリ

【請求項5】

該側帯メモリが並列の第一及び第二単ポート型アレイを備え、該アレイの各々は該第一数のエントリを有し、第一及び第二単ポート型アレイの対応する対の各々は該主メモリ内の記憶装置の一つの中の対応するエントリにマッピングされ、第一及び第二単ポート型アレイの中のエントリの各対応する対の中の只一つのみ有効化され、該制御論理がエントリの各対応する対の中のどれが有効化されているか追跡するように更に構成されているものである、請求項1に記載のメモリ。

### 【請求項6】

該制御論理は該側帯メモリ内の対応するエントリの各対に対応する該主メモリ内の記憶 装置を特定するタグメモリを備え、該タグメモリは更にエントリの各対応する対の中のど れが有効化されているか特定するものである、請求項 5 に記載のメモリ。

【請求項7】

該制御論理は該側帯メモリ内の各エントリに対応する該主メモリ内の記憶装置を特定するタグメモリを備え、該タグメモリはサイクル毎に該タグメモリに三つのメモリアクセスを可能にするように構成されているものである、 請求項1に記載のメモリ。

### 【請求項8】

該タグメモリはトリプルポート型のアレイを備えるものである、請求項7に記載のメモリ。

### 【請求項9】

該タグメモリは並列の第一及び第二デュアルポート型アレイを備えるものであり、該アレイの各々は該第一数のエントリを有し、該タグメモリへの書き込み操作は該第一及び第二デュアルポート型アレイ内のエントリの各対応する対の両方に同じ値を書き込み、第一及び第二同時読み出し操作は夫々該第一及び第二デュアルポート型メモリから読み出すものである、請求項7に記載のメモリ。

【請求項10】

共有メモリスイッチであって、

複数の受信ポートと、

複数の送信ポートと、

メモリであって、該メモリは

複数の単ポート型記憶装置(メモリバンク)から成り、各記憶装置は第一数のエント リを有するものである主メモリと、

該単ポート型記憶装置の中の異なるものから同時に読み書き操作を可能とするように 構成された並列バスと、

該第一数のエントリを備える側帯メモリであって、該側帯メモリ内の各エントリは該主メモリ内の記憶装置の一つの中の対応するエントリにマッピングされ、該側帯メモリはサイクル毎に該側帯メモリへ並列読み書きアクセスが可能であるように構成されたものである側帯メモリと、

該主メモリあるいは該側帯メモリへ読み書き操作を導くように構成されたスイッチ回路と、

該主メモリの中のどの記憶装置に該側帯メモリ内の各エントリが対応するか追跡し、 メモリアドレス情報に応じて決定論的に該スイッチ回路を制御して該メモリが完全に供給 10

20

30

40

されたデュアルポート型メモリのように機能するように該主メモリと該側帯メモリへのアクセスパタンを実施するように構成された制御論理とを備える、メモリと、

該受信ポートのいずれをも該メモリと接続するように機能可能である受信クロスバー回路と、

該メモリを該送信ポートのいずれとも接続するように機能可能である送信クロスバー回路と、

該ポート、クロスバー回路、及びメモリの相互作用を制御して該メモリ内のデータ貯蔵 及び検索を実行するスイッチ論理と、

を備える共有メモリスイッチ。

【発明の詳細な説明】

# 【背景技術】

#### [00001]

本出願は2008年12月19日に提出された米国特許出願12/340022号を基に優先権を主張するものであり、この全体をすべての目的において此処に合同するものとする。

### [0002]

本発明は単ポート型の記憶装置 (メモリバンク)を使用してサイクル毎に読み書きの同時操作を可能とするメモリに関する。

#### [0003]

共有メモリスイッチにおいて、その帯域幅を限定する隘路の一つはメモリの速度である。最悪の場合、各パケット上の読み書きに特別なメモリ位置が必要となることがある。従って、単ポート型のスタティックランダムアクセスメモリ(SRAM)セルを使用する与えられた帯域幅の完全に供給されたスイッチを得るためには、メモリの操作速度が所望のパケット速度の二倍でなくてはならない。

### [0004]

その一方、サイクル毎に二操作(即ち読み出しと書き込み)が可能な二重(デュアル)ポート型のSRAMセルを使用すれば、メモリの所要速度の半減が可能となる。しかし、これには単ポート型のSRAMに比して二倍ものシリコン面積が必要となる。

### 【発明の概要】

### [0005]

本発明の種々な実施形態において、各々が第一数のエントリを持つ複数の単ポート型記憶装置を有する主(メイン)メモリを含むメモリが提供される。並列バスが異なる単ポート型記憶装置からの同時読み書きを可能とするように設定されている。この第一数のエントリを有する側帯(サイドバンド)メモリが備えてあり、側帯メモリの各エントリは主メモリの中の一つの記憶装置の対応するエントリにマッピングされる。側帯メモリはサイクル毎にこの側帯メモリへの並列読み書きアクセスを可能とするように設定されている。主メモリと側帯メモリのいずれかへの読み書き操作へ導くようにスイッチ回路が設定されている。制御論理は側帯メモリの各のエントリが主メモリの中のどの記憶装置に対応するか追跡し、メモリアドレス情報に応じてスイッチ回路を決定的に制御して主メモリと側帯メモリへのアクセスパタンを実行することにより、このメモリが完全供給されたデュアルポート型のメモリのように機能すべく設定されている。

# [0006]

本発明の一種の実施形態において、側帯メモリは同一のサイクルで異なるアドレスでの 読み書きが可能なデュアルポート型のアレイとして実施される。

# [0007]

本発明の別種の実施形態において、側帯メモリには並列に第一と第二の単ポート型のアレイがあり、その各々に第一数のエントリが含まれている。第一と第二の単ポート型のアレイの中の各対応する対のエントリの両方が主メモリの中の一つの記憶装置の対応する一つのエントリにマッピングされている。第一と第二の単ポート型のアレイの中の各対応するエントリの一対の中の一方のみが有効である。制御論理は各対応するエントリの対の中

10

20

30

40

どちらが有効なのか追跡するように設定されている。

[0008]

本発明の更に別種の実施形態においては、側帯メモリの中の各エントリが対応する主メモリ内の記憶装置を同定するタグメモリが制御論理に含まれる。このタグメモリはサイクル毎に例えば二回の読み出しと一回の書き込みのように三回のアクセスを許容するように設定されている。この種の若干の実施形態において、タグメモリは三重ポート型のアレイとして実施される。

[0009]

この種の中の別の実施形態において、タグメモリは並列の第一と第二の単ポート型のアレイで実施され、その各々には第一数のエントリがあり、タグメモリへの書き込み操作では第一と第二の単ポート型のアレイの中の各対応する対のエントリの両方に同じ値が書き込まれ、第一と第二の同時の読み出し操作では夫々第一と第二のデュアルポート型メモリから読み出される。

[0010]

更に考慮されて居る実施形態では、本発明の実施形態によって実装されたメモリの使用によって共用メモリスイッチ及びかような共用スイッチの互いに接続された複数のインスタンスを含むスイッチ構造が実現される。

[0011]

本発明の特徴及び利点は明細書の以後の部分及び図面によって更に明確に理解されることであろう。

【図面の簡単な説明】

[0012]

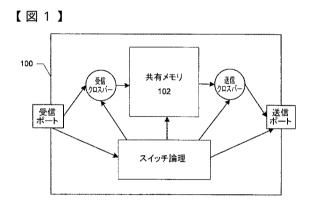

【図1】二重周期又はデュアルポート型共用メモリを要する共用メモリスイッチ構造のブロック図である。

[0013]

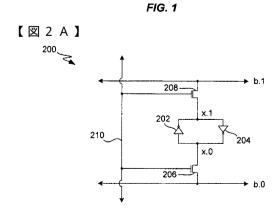

【図2A】は本発明の種々の実施形態で使用可能な単ポート型のSRAMメモリセルの回路図である。

【図2B】本発明の種々の実施形態で使用可能なデュアルポート型のSRAMメモリセルの回路図である。

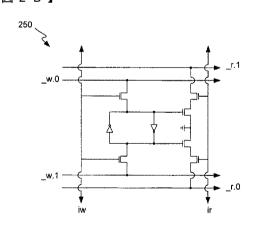

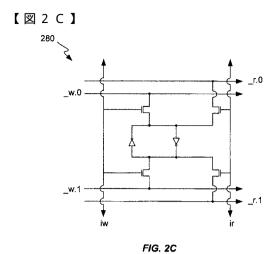

【図2C】本発明の種々の実施形態で使用可能なデュアルポート型のSRAMメモリセルの回路図である。

[0014]

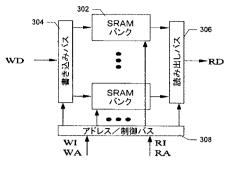

【図3】並列の読み書きバスに接続された単ポート型装置の主SRAMアレイのブロック図である。

[0015]

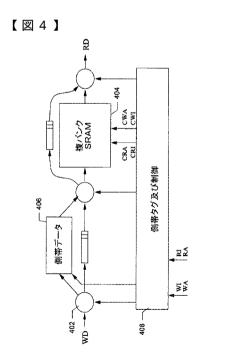

【図4】本発明の所定の実施形態によって実装されたSRAMのブロック図である。

[0016]

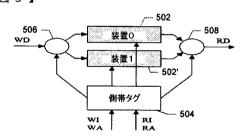

【図5】本発明の所定の実施形態によって実装されたSRAMの一部のブロック図である

[0017]

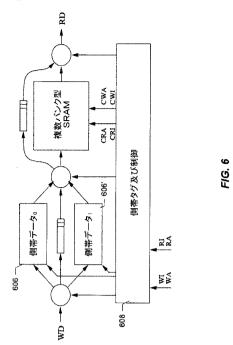

【図6】本発明の別の所定の実施形態によって実装されたSRAMの一部のブロック図で ある。

【発明を実施するための形態】

[0018]

本発明を実施するに当たり発明者が最良とみなす形体を含めた特別な実施形態を参照して発明を詳細に説明する。これら実施形態の例は図に示されて居る。発明はこれらの実施形態について説明されるが、発明はこれらの実施形態に限定される意図ではない。それに反し、各種の代替、変形、相当例などは本発明の範囲に含まれるものと理解されたい。以下の記述に於いて、多くのを特別な細部事項が徹底的な理解の目的で提出される。本発明を実施するに当たっては、これらの詳細事項がすべて必要とは限らない。その他の場合に

10

20

30

40

は、本発明の内容を不必要な程度までに不明確にしないために、周知の手順の実施などについては、詳細な記述は省略される。

### [0019]

本発明の種々の実施形態において、デュアルポート型性能は単ポート型メモリの記憶装置を使用し、同時の読み書き操作が同一の記憶装置に導かれる隅のケースに対処するためメモリを通じて代行的通路を提供することにより達成される。単ポート型の装置は同時に一つの装置から書き込んで他の装置から読み出し可能なデュアルポート型データ、アドレス、及び制御バスによって接続されている。しかし、装置自身は単ポート型なので、このシステムは同一サイクルで同じ装置から読み書きをすることが出来ない。以後説明されるように、本発明の実施形態は無制限な装置のデュアルポート型外部アクセスを維持する一方、これらの装置コンフリクトを回避する機構を提供するものである。

### [0020]

本発明の実施形態は例えばその全体を此処に参照して合同する2006年5月23日に発行された題名を Asynchronous Static Random Access Memory とする米国特許7050324号に記載されたような非同時性SRAMを実現するために使用可能である。しかし、本発明の実施形態は或る非同時性デザインのスタイルに適当であるが、本発明の基礎的原理は同時性メモリデザインに極めて応用可能であり、従って同時性メモリデザイン及びそれを使用する装置やシステムも本発明の範囲内に含まれることに留意されるべきである。

### [0021]

本発明の特種な実施形態は共有メモリ型スイッチ及び/或はそのような共有メモリ型スイッチの複数のインスタンスを備えるスイッチ構造を実現するのに使用されてもよい。本発明の実施形態が実装可能な共有メモリ型スイッチの例はその全体をすべての目的で此処に参照して合同する2006年7月13日に発行された題目をShared-Memory Switch Fabric Architecture とする米国特許公開2006-0155938A1に記載されている。更に一般的なこととして、本発明の基礎的原理はエサネット、シリアルラピッドI/O、アドバンスドスイッチング、あらゆるストリーミングプロトコル(例えばTDM,SPI-4)、あらゆる高級層プロトコル(例えばTCP/IP)、及びあらゆる他のものの上のプロトコル(例えばエサネット上のハイパートランスポート)を含めた事実上すべてのプロトコル或いは相互接続技術に実現されてよい。

# [0022]

更に一般的なこととして、本発明はSRAM技術、共有メモリ型スイッチ技術、又はそれに類する応用面に限定されるものでないと留意されるべきである。それに反し、本発明の実施例は単ポート型メモリへの限定が問題点となるあらゆるコンテキストにおいてその対応に使用可能である。

# [0023]

図1は共有メモリアレイとしてSRAMアレイ102を含む共有メモリ型スイッチ101の簡素化されたブロック図である。SRAMアレイ102は各々が単ポート型SRAMセルで実現されているSRAM装置0からB-1(例えば図3の装置302)の主メモリアレイで実現されている。図に示された装置の数は例示のためであって、任意の数の装置が使用可能であることは理解されよう。異なる装置との同時操作が起こってもよいようにデュアルポート型のバス及びアドレスの分配(例えば図3のバス304、306及び308)が供されているが、単ポート型SRAMセルが主メモリ装置の実現に使用されているので、与えられた時間においては只一回のみのアクセス(即ち読み出し又は書き込み)が与えられた記憶装置には起こり得る。

### [0024]

以下論じられるように、二次"側帯"メモリが同時の読み書き操作間の装置コンフリクトを解決すべく主メモリに並列構造として供されている。種々の実施形態において、この側帯メモリは主メモリの中のSRAM装置の一つと同じサイズ、即ちメモリセルの数が同

10

20

30

40

じである。特種な実施形態において、この側帯メモリはデュアルポート型SRAMセルで 実現され、従って同時の読み書きを支持する。しかし、後述するように、実施形態では側 帯メモリは単ポート型メモリセルを使用して実現されるように考慮されている。

### [0025]

本発明の種々の実施例との使用に好適な単ポート型及びデュアルポート型SRAMセルの例が図2A乃至2Cに示されている。図2Aは対応するビット線b.0及びb.1に接続するトランジスタ通過(パス)ゲイト206及び208と交差カプリングする一対のインバータ202及び204を含むトランジスタ6個型(6T)SRAM状態要素200を示す。アドレス線210は通過ゲイト206及び208をオンにしてビット線をSRAM状態要素の内部ノード×.0及び×.1の上の状態に露出する。ビット線b.0及びb.1はSRAM状態要素200に貯蔵されたデータのデュアルレイル型表示と思われてよい

10

#### [0026]

SRAM状態要素 2 0 0 の状態を読み出すにはアドレス線 2 1 0 を使用してトランジスタ通過ゲイト 2 0 6 及び 2 0 8 をオンにしてビット線 b . 0 及び b . 1 (予め高に帯電)を夫々内部ノード× . 0 及び× . 1 のに接続する。低である内部ノードは対応する感知されたビット線を低に引き、デュアルレイル値はバッファされて請求者に送られる。SRAM状態要素 2 0 0 に書き込むにはアドレス線 2 1 0 が内部ノードをビット線に露出するように再び使用され、内部ノードは所望の書き込み値で駆動され、交差カプリングされたインバータ 2 0 2 及び 2 0 4 の中のトランジスタを圧倒し状態要素の新しい内部状態を設立する。

20

### [0027]

図2 B は 2 本のバスがその中 1 本が読み出しに、他の 1 本が書き込みに使用されるトランジスタ 1 0 個型(1 0 T) S R A M 状態要素 2 5 0 を示す。即ち、状態要素 2 5 0 への書き込みにはアドレス線 i w と共に書き込みバス線 w . 0 及び w . 1 が使用される一方、状態要素 2 5 0 からの読み出しにはアドレス線 i r と共に読み出しバス線 r . 0 及び r . 1 が使用される。図 2 A の 6 T 状態要素と対照的に、1 0 T 状態要素はダイエアリアをよけい必要とする代わり著しく高速である。更に、読み書きのバスが別であるため、実質的に同時の別のアドレスの読み書き操作が同じ S R A M 装置で可能である。

30

### [0028]

デュアルポート型 SRAMを製作するのに、8T型のデュアルポート型状態ビットも使用可能である。図2Cは本発明の種々の実施形態で使用可能であり、図2Bの状態要素と同様な機能とトポロジイを有するトランジスタ8個型(8T)SRAM状態要素280を示す。

### [0029]

特種の実施形態においては、主メモリのSRAM装置内の"ストライプ"又はエントリ(例えばХХХХSTRIPEOХХХХХ)が側帯メモリ内の対応するストライプ又はエントリにマッピングされる。例えば装置0内のストライプ0は側帯メモリ内のストライプ0にマッピングされる。同様に装置1内のストライプ0は側帯メモリ内のストライプ0にマッピングされ、以下同様である。明らかに、主メモリ装置の一つに対応する只一つのエントリが与えられた時間において側帯メモリに貯蔵可能である。種々の実施形態において、主メモリSRAM装置に貯蔵された情報へのアクセスのパタンはSRAM102がそれがあたかも完全に供給されたデュアルポート型メモリであるかのように操作することによって容易にされる。

40

### [0030]

種々の実施形態において、側帯メモリ内の各エントリ又はストライプはいずれの与えられた時間においても装置 0 乃至 B - 1 のいずれかの一つの対応するエントリのコピイを貯蔵する。特別の種類の実施形態において、又下記のように、ある特別の操作を主メモリ S R A M 装置或いは側帯メモリに導くかとの決定は完全に決定論的なものである。より高い情報量を達成するために統計的行為に依存するメモリと異なり、本発明の種々の実施例に

従って実現されるメモリではメモリのアクセスに関するコンフリクトによりパケットを落とす危険がない。読み書きの同時操作の異なるシナリオに関する簡単な議論が有用と思われる。

### [0031]

第一の場合として、読み書きの操作の両方が側帯メモリに導かれる。側帯メモリはデュアルポート型であるから、従って両方の操作が並列的に実行される。

### [0032]

第二の場合では、操作の中の一方(即ち読み出し又は書き込み)が側帯メモリに貯蔵されたエントリに導かれ、他方(即ち書き込み又は読み出し)が主メモリのエントリに導かれる。この場合も、主メモリが他方を処理している間に側帯メモリが一方を処理できるので、両方の操作が並列的に実行される。

### [0033]

第三の場合では、両方の操作が導かれて行くエントリのいずれも側帯メモリに貯蔵されて居らず、操作は主メモリの異なる装置へ導かれて行く。上記のように平行な読み書きのバスが存在する限り、両方の操作はコンフリクトなしに主メモリの中で実施可能である。

#### [0034]

両方の操作が同一装置内のエントリに導かれ、これらのエントリのいずれも側帯メモリに貯蔵されていないと、興味ある場合となる。本発明の特種な実施形態では、このような場合が検出されると読み出し操作が主メモリに導かれ、書き込み操作が側帯メモリに導かれるように処理される。それと共に主メモリと側帯メモリの両方において同時に読み書きが実施される。これは以下のように実行される。

#### [0035]

この場合、上書きされる側帯メモリのエントリは書き込み操作が導かれるものとは違う装置に属すものであり、それはそうでないと書き込み操作で側帯メモリ内の自身のエントリの上書きをすることになるからである。更に、側帯メモリ内で上書きされているエントリは第一の読み出し操作と干渉しない様式で同時に側帯メモリから読み出され、主メモリの対応位置に書き戻されるかも知れない。これは読み出し操作が導かれる主メモリ内の装置は側帯メモリから上書きされているエントリを含むものと異なるからである。この側帯メモリからの同時読み出し操作はこれがデュアルポート型メモリであるから可能とされるものである。

### [0036]

理解される如く、本発明の実施形態に従って実行される側帯メモリに関連するオーバヘッドは主メモリ内の装置のサイズに比例する。即ち、主メモリの装置が大きい程側帯メモリは大きくなる。従って、全体的な面積上の不利益から、本発明の実施形態は主メモリが多数の装置を有する場合及び/或は記録装置のサイズが比較的小さい場合に殊に有利である。

# [0037]

特別な実施形態のより詳細な開示が図4に示されている。示される如く、書き込みチャネルは小さなスイッチ要素402に入り、これが書き出しデータを主メモリ404又は側帯メモリ406に送信する。

## [ 0 0 3 8 ]

側帯タグ論理408が読み書きアドレスを受信し、それに従って種々のクロスバー及びメモリを制御する。側帯タグ論理408には側帯メモリ406内の各エントリの装置番号を貯蔵し、即ち主メモリ404内のどちらの装置が側帯メモリ406内の各エントリに対応するのかを示す側帯タグメモリ(表示なし)が含まれる。従って、例えば主メモリに64個の装置がある場合、側帯メモリ内の各エントリはそのエントリに対応する主メモリ内の装置を特定する6ビットで表される。

### [0039]

側帯メモリがデュアルポート型(与えられたサイクル内で読み書き両方が可能)である 一方 、主メモリ404内のSRAMは単ポート型(与えられたサイクル内で読み書きの 10

20

30

40

一方のみ可能)である。或るタイプの実施形態では側帯タグ論理408内の側帯タグメモリは三重(トリプル)ポート型であり、各サイクルで二つの読み出しと一つの書き込みが可能である。これは各サイクルで二つの異なる指標の二つの読み出しが側帯タグメモリ内で起こることであり、即ち主メモリ404内の装置に導かれた二つのメモリ操作毎に一つである。更に、側帯メモリ406内のエントリが上書きされた場合、側帯タグメモリ内の対応エントリも変更される。もし主メモリ内の各装置がNエントリ対Wビットであると、主メモリ内の装置の数をBとした場合、側帯タグブロック内のメモリのサイズがNx[1 og2B]であることが理解されよう。

### [0040]

上記の実施により、単ポート型記憶装置と若干の追加オーバヘッドを使用したデュアルポート型メモリの性能をデュアルポート型8 T 又は 1 0 T の状態ビットで構築した均等周期のデュアルポート型デザインで表される面積のペナルティを 2 倍乃至 3 倍の小部分として可能にする。

### [0041]

図 5 に示される代行的アプローチによると、上記のような面積の節約は達成しないが、それでもデュアルポート型 S R A M よりは小型な側帯メモリと同様の概念が使用可能である。上記の実施形態のように、これも全く決定論的なものであって、統計的行為に依存する必要はない。

### [0042]

この実施形態においては単ポート型主メモリが二重化され(502及び502<sup>'</sup>)、貯蔵されるべきメモリ内の各エントリに二つの位置の可能性があることになる。理解されるように、単ポート型による実施の場合に比較すればこれによってサイズは二倍以上になるが、面積に関するこのペナルティはそれでもデュアルポート型セルを使用する場合より小さい。

### [0043]

各対の装置内の同じ位置の対応するエントリの対の各々について、制御論理 5 0 4 は現行の値を持っているのがどちらの装置であるか追跡をする。制御論理 5 0 4 はすべての読み出し操作を読み出し操作が導かれているエントリの現行の値を持った装置に導く。同時の読み書きの間、制御論理 5 0 4 は読み出し中でない装置に書き込み装置を導く。そのように書き込まれた装置は現行値を含む。

### [0044]

どちら装置が現行値を保持しているか追跡するため、制御論理504は装置502及び502,の中のN個のエントリの各々について1ビットを持っており、二つの装置の中のどちらが対応するエントリの値を持っているのか特定する。この情報を使用して、制御器504はクロスバー506及び508を制御し、読み書きの操作を適宜な装置に導く。特定のエントリが装置のなかの一つに上書きされる毎に、変化を反映するために制御論理504の中の対応するエントリが変化される。特別な実行法によると、制御論理504の中のメモリはデュアルポート型メモリであって、同一のサイクルの中で読み出し操作(即ちどちらの入力される読み出し操作が導かれるべきか特定するため)及び書き込み操作(即ち新しい現行装置を反映すべく入力される書き込み操作に対応するエントリを変更するため)の両方を実行可能にする。

### [0045]

特種の実施形態では、図5を参照して記述されたアプローチが側帯メモリの実施に使用される図4での実施例を改善したものが示されている。即ち、図6に示されているように、図4を参照して上記されたデュアルポート型側帯メモリ406は二個の並列された単ポート型メモリ606及び606′を使用して実施可能なものである。これは1ビットを側帯タグ論理408内のNエントリ側帯タグメモリ(即ちN×[(1og2B)+1])に付け加え、どちらの単ポート型側帯メモリが現行値を持つか追跡し、側帯タグ論理408が図5を参照して上記されたように操作する(その結果側帯タグ論理608)ように更新して達成することが出来る。このアプローチの利点は側帯メモリの実施に使用される単ポ

20

10

30

40

ートSRAM装置は主メモリ内のSRAM装置と同じであってもよいことである。

### [0046]

2個のデュアルポート型メモリを使用するトリプルポート型側帯タグメモリ410の代用の実施用として同様な線に沿って更に改善が可能である。即ち、図5を参照して上記のような2個並列された単ポート型メモリの代わりに、並列メモリはデュアルポート型であり、サイクル毎に一つの読み出し操作と一つの書き込み操作を支持するものである。変更はすべてこれらタグメモリの両方に書き込まれ、それで両者は常に同じ値を持っている。この二重化によって二つの読み込み操作が各タグ記憶装置を一つが使用して並列に起こる。即ち書き込み操作は両方のメモリ内の同じ位置に同じ値を書き込むことに関する。各サイクルの読み出し操作の一つは一方の並列デュアルポート型メモリで実施され、他方の読み出し操作は他方のもので実施される。

### [0047]

本発明は特種実施形態について記述されたものであるが、当業者には此処に記述された 実施形態の形態や細目は本発明の精神及び範囲を逸脱することなく変更されてよいもので あると理解されよう。例えば、此処ではSRAMに関するメモリ技術として記述がされて 居るが、此処に記述された技術は此処に記述された技術と同様に限定される種々のメモリ 技術を使用するメモリシステムの実施に使用可能であると理解されよう。更に、本発明の 種々な利点、観点、及び目的は種々の実施形態を参照して記述されているが、かかる利点 、観点、及び目的によって本発明の範囲は限定されるものでないと理解されよう。それに 反し、本発明の範囲は以下の請求項を参照して決定されるべきものである。

20

FIG. 2B

FIG. 2A

【図3】

FIG. 3

【図5】

FIG. 4

FIG. 5

【図6】

### フロントページの続き

# (72)発明者 ラインズ・アンドリュー

アメリカ合衆国 カリフォルニア州90265 マリブ,シーガル・ウェイ,26666,ユニット シー101

#### 審査官 菅原 浩二

### (56)参考文献 特表2008-527922(JP,A)

特開平09-128970(JP,A)

特開2005-108403(JP,A)

特開2004-242333(JP,A)

特開2002-055879(JP,A)

特開平10-326491(JP,A)

特開昭63-039191(JP,A)

特開平02-123594(JP,A)

特開平06-259323(JP,A)

特開平02-007141(JP,A)

特開平03-095795(JP,A)

特表2009-543268(JP,A)

特開昭63-186362(JP,A)

特開平09-115286(JP,A)

特開2004-288355(JP,A)

特開平03-063995(JP,A)

特開2008-143968(JP,A)

特開平04-117697(JP,A)

特開昭63-181191(JP,A)

特開平08-212784(JP,A)

特開平10-106269(JP,A)

特開昭62-243196(JP,A)

特開平10-326490(J P , A )

特開2000-013438(JP,A)

特表2004-536515(JP,A)

# (58)調査した分野(Int.CI., DB名)

G11C 11/413