## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6042999号 (P6042999)

(45) 発行日 平成28年12月14日(2016.12.14)

(24) 登録日 平成28年11月18日 (2016.11.18)

| (51) Int.Cl. |        |           | FΙ      |       |     |

|--------------|--------|-----------|---------|-------|-----|

| G11C         | 11/413 | (2006.01) | G11C    | 11/34 | Α   |

| G11C         | 11/417 | (2006.01) | G 1 1 C | 11/34 | M   |

| G11C         | 11/412 | (2006.01) | G 1 1 C | 11/34 | 305 |

|              |        |           | G11C    | 11/40 | 301 |

(全 18 頁) 請求項の数 9

特願2015-555219 (P2015-555219) (21) 出願番号 (86) (22) 出願日 平成26年1月21日 (2014.1.21) (65) 公表番号 特表2016-504705 (P2016-504705A) 平成28年2月12日 (2016.2.12) (43) 公表日 (86) 国際出願番号 PCT/US2014/012403 (87) 国際公開番号 W02014/116612 (87) 国際公開日 平成26年7月31日 (2014.7.31) 審査請求日 平成27年7月24日 (2015.7.24) (31) 優先権主張番号 13/750,943 (32) 優先日 平成25年1月25日 (2013.1.25) (33) 優先権主張国 米国(US)

(73)特許権者 503455363

レイセオン カンパニー

アメリカ合衆国 マサチューセッツ州 〇 2451-1449 ウォルサム ウィン ター ストリート 870

(74)代理人 100099759

弁理士 青木 篤

(74)代理人 100092624

弁理士 鶴田 準一

||(74)代理人 100114018

弁理士 南山 知広

|(74)代理人 100165191

弁理士 河合 章

|(74)代理人 100151459

弁理士 中村 健一

最終頁に続く

(54) 【発明の名称】低電力スタティックランダムアクセスメモリ

## (57)【特許請求の範囲】

## 【請求項1】

スタティックランダムアクセスメモリ(SRAM)セルのビット線ドライバであって、 第1の電圧を供給する第1の電源と、

前記第1の電圧よりも低い第2の電圧を供給する第2の電源と、

前記SRAMセルに対する書込みを行うときにビット線及び反転ビット線を駆動するよ うに構成された書込み回路と、

前記SRAMセルの内容の読出しを行う前に前記ビット線及び前記反転ビット線をプリ チャージするように構成されたプリチャージ回路と、

を備え、

10

前記ビット線ドライバは、前記ビット線ドライバが前記ビット線又は前記反転ビット線 をハイ状態にするときに前記第1の電圧よりも一つのトランジスタのしきい値電圧だけ低 い電圧を前記ビット線又は前記反転ビット線に供給するように構成され、

前記書込み回路は、前記書込み回路が前記ビット線をハイ状態にするときに前記第1の 電圧よりも一つのトランジスタのしきい値電圧だけ低い電圧を前記ビット線に供給するよ うに構成され、

前記書込み回路は、前記書込み回路が前記反転ビット線をハイ状態にするときに前記第 1 の電圧よりも一つのトランジスタのしきい値電圧だけ低い電圧を前記反転ビット線に供 給するように構成され、

前記書込み回路は、

## 一対のプルアップ回路と、

<u>各々が前記一対のプルアップ回路の反対の側のプルアップ回路のゲートに交差結合した</u> ゲートを有する一対のプルダウン回路と、

<u>各々が前記プルアップ回路の対応するものと前記一対のプルダウン回路の同一の側のプ</u>ルダウン回路との間に介在した一対のアクセス回路と、

#### を備え、

前記書込み回路は、データ信号及び書込み信号に従って前記ビット線及び前記反転ビット線を選択的にプルアップ又はプルダウンするように構成され、

前記一対のプルアップ回路は、

前記第1の電源と前記ビット線との間に結合した第1のトランジスタと、

前記第1の電源と前記反転ビット線との間に結合した第2のトランジスタと、

#### を備え、

前記一対のプルダウン回路は、

前記第2の電源と前記ビット線との間に結合した第3のトランジスタと、

<u>前記第2の電源と前記反転ビット線との間に結合した第4のトランジスタと、</u> を備え、

前記一対のアクセス回路は、

前記第1のトランジスタと前記ビット線との間に介在した第5のトランジスタと、

前記第2のトランジスタと前記反転ビット線との間に介在した第6のトランジスタと、

前記第3のトランジスタと前記ビット線との間に介在した第7のトランジスタと、

<u>前記第4のトランジスタと前記反転ビット線との間に介在した第8のトランジスタと、</u> を備え、

前記第 1 のトランジスタ、前記第 2 のトランジスタ、前記第 3 のトランジスタ、前記第 4 のトランジスタ、前記第 7 のトランジスタ及び前記第 8 のトランジスタは、 n 型トランジスタであり、

<u>前記第5のトランジスタ及び前記第6のトランジスタは、p型トランジスタである</u>ビット線ドライバ。

#### 【請求項2】

前記第1のトランジスタ及び前記第4のトランジスタは、共にオン及びオフになるように構成され、

前記第2のトランジスタ及び前記第3のトランジスタは、共にオン及びオフになるように構成され、

前記第5のトランジスタ、前記第6のトランジスタ、前記第7のトランジスタ及び前記第8のトランジスタは、共にオン及びオフになるように構成される請求項<u>1</u>に記載のビット線ドライバ。

## 【請求項3】

前記第1のトランジスタ及び前記第4のトランジスタは、前記データ信号に従ってオン 及びオフになるように構成され、

前記第2のトランジスタ及び前記第3のトランジスタは、前記データ信号の反転である 反転データ信号に従ってオン及びオフになるように構成され、

前記第5のトランジスタ、前記第6のトランジスタ、前記第7のトランジスタ及び前記第8のトランジスタは、前記書込み信号に従ってオン及びオフになるように構成される請求項2に記載のビット線ドライバ。

# 【請求項4】

前記第1のトランジスタ及び前記第3のトランジスタの少なくとも一方及び前記第2のトランジスタ及び前記第4のトランジスタの少なくとも一方は、前記SRAMセルの行アクセストランジスタと同一の型のトランジスタである請求項1に記載のビット線ドライバ

## 【請求項5】

前記プリチャージ回路は、前記プリチャージ回路が前記ビット線を前記ハイ状態にする

10

20

30

40

ときに前記第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧を前記ビット線 に供給するように構成され、

前記プリチャージ回路は、前記プリチャージ回路が前記反転ビット線を前記ハイ状態にするときに前記第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧を前記反転 ビット線に供給するように構成される請求項1に記載のビット線ドライバ。

## 【請求項6】

前記プリチャージ回路は、

プリチャージ信号に従って、前記ビット線を、前記第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第1のプルアップ回路と、前記プリチャージ信号に従って、前記反転ビット線を、前記第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第2のプルアップ

反転プリチャージ信号に従って前記ビット線の電圧と前記反転ビット線とのバランスを とるバランス回路と、

を備える請求項5に記載のビット線ドライバ。

#### 【請求項7】

回路と、

前記第1のプルアップ回路は、前記第1の電源と前記ビット線との間に介在した第1の トランジスタを備え、

前記第2のプルアップ回路は、前記第1の電源と前記反転ビット線との間に介在した第2のトランジスタを備え、

前記バランス回路は、前記ビット線と前記反転ビット線との間に結合した第3のトランジスタを備える請求項6に記載のビット線ドライバ。

## 【請求項8】

前記第1のトランジスタ及び前記第2のトランジスタは、前記SRAMセルの行アクセストランジスタと同一の型のトランジスタである請求項7に記載のビット線ドライバ。

## 【請求項9】

スタティックランダムアクセスメモリ(SRAM)アレイであって、

行配置された複数のワード線であって、前記ワード線の各々が複数のワード信号のうちの対応するワード信号を供給する複数のワード線と、

列配置された複数のビット線であって、前記ビット線の各々が複数のビット信号のうちの対応するビット信号を供給する複数のビット線と、

前記ビット線と共に列配置された複数の反転ビット線であって、前記反転ビット線の各々が複数の反転ビット信号のうちの対応する反転ビット信号を供給し、前記対応する反転ビット信号は、同一の列において前記ビット線のうちの対応するビット線によって供給される前記ビット信号の反転である複数の反転ビット線と、

第1の電圧を供給する第1の電源と、

前記第1の電圧よりも低い第2の電圧を供給する第2の電源と、

行列配置された複数のSRAMセルであって、前記SRAMセルの各々は、前記ワード線、前記ビット線及び前記反転ビット線の各々の一つに対応する複数のSRAMセルと、前記ワード線を駆動するように構成されたワード線ドライバと、

前記ビット線及び前記反転ビット線を駆動するように構成されたビット線ドライバと、 を備え、

前記ビット線ドライバは、前記ビット線ドライバが前記ビット線の一つをハイ状態にするときに前記第1の電圧よりも前記ビット線ドライバの一つのトランジスタのしきい値電圧だけ低い電圧を前記ビット線の一つに供給するように構成され、

前記ビット線ドライバは、前記ビット線ドライバが前記反転ビット線の一つをハイ状態にするときに前記第1の電圧よりも前記ビット線ドライバの一つのトランジスタのしきい 値電圧だけ低い電圧を前記反転ビット線の一つに供給するように構成され、

前記ビット線ドライバは、複数の書込み回路を備え、前記書込み回路の各々は、前記ビット線のうちの一つのビット線、前記反転ビット線のうちの一つの反転ビット線及び前記

10

20

30

40

## SRAMセルの一つの列に対応し、

前記書込み回路の各々は、

一対のプルアップ回路と、

各々が前記一対のプルアップ回路の反対の側のプルアップ回路のゲートに交差結合した ゲートを有する一対のプルダウン回路と、

各々が前記プルアップ回路の対応するものと前記一対のプルダウン回路の同一の側のプ ルダウン回路との間に介在した一対のアクセス回路と、

## を備え、

前記書込み回路の各々は、データ信号及び書込み信号に従って前記ビット線及び前記反 転ビット線を選択的にプルアップ又はプルダウンするように構成され、

10

20

前記一対のプルアップ回路は、

前記第1の電源と前記ビット線との間に結合した第1のトランジスタと、

前記第1の電源と前記反転ビット線との間に結合した第2のトランジスタと、

# を備え、

前記一対のプルダウン回路は、

前記第2の電源と前記ビット線との間に結合した第3のトランジスタと、

前記第2の電源と前記反転ビット線との間に結合した第4のトランジスタと、

## を備え、

前記一対のアクセス回路は、

前記第1のトランジスタと前記ビット線との間に介在した第5のトランジスタと、 前記第2のトランジスタと前記反転ビット線との間に介在した第6のトランジスタと、

前記第3のトランジスタと前記ビット線との間に介在した第7のトランジスタと、

前記第4のトランジスタと前記反転ビット線との間に介在した第8のトランジスタと、 を備え、

前記第1のトランジスタ、前記第2のトランジスタ、前記第3のトランジスタ、前記第 4 のトランジスタ、前記第 7 のトランジスタ及び前記第 8 のトランジスタは、 n 型トラン ジスタであり、

前記第5のトランジスタ及び前記第6のトランジスタは、p型トランジスタであるSR A M アレイ。

【発明の詳細な説明】

30

【技術分野】

[0001]

連邦政府による資金提供を受けた研究開発の記載

本発明は、米国政府の支援を受けた。米国政府は、本発明に対する所定の権利を有する

## 【背景技術】

[0002]

本発明の態様は、低電力スタティックランダムアクセスメモリに関する。

### [0003]

2. 従来技術の説明

スタティックランダムアクセスメモリ(SRAM)は、デジタルコンピュータ及び他の アプリケーションとともに用いるためのメモリを提供するためにデジタルシステムで広く 用いられている。SRAMは、他の何らかのタイプの記憶装置よりも高速かつ使いやすい という利点を有する。さらに、MOS技術を用いるSRAMは、低い待機電力を示し、格 納した情報を維持するためのリフレッシュサイクルを必要としない。

## [0004]

SRAM装置はしばしば、行及び列配置されたSRAMセルのアレイで構成される。 般的には、SRAMセルは、1ビットの情報を格納するときに二つのデータ状態のうちの 一方に設定される。各メモリセルを、行アドレス及び列アドレスを含む固有のメモリアド

50

20

30

40

50

レスによって参照してもよい。用語「ワード線」は、SRAMセルの行に対応する導体を言及し、用語「ビット線」は、SRAMセルの列に対応する導体を言及する。ワード線を、ワード線ドライバによって駆動してもよく、ビット線をビット線ドライバによって駆動してもよい。SRAMセルは、相補的なポートの対を有してもよく、各ポートは、当該列に対応する二つのビット線、記憶ビットを格納するための二つの交差結合インバータ及び交差結合インバータに対するアクセスを制御するための二つのアクセストランジスタのうちの一方に結合される。

## [0005]

SRAMアレイは、読出しモード及び書込みモードで動作してもよい。SRAMセルからの読出しを行うとき、SRAMセルに関連するビット線は、ハイ論理状態までプリチャージされ、対応するワード線は、格納された論理状態を読み出すために起動され、論理状態は、センス増幅器を用いることによってビット線から差動的に検知される。センス増幅器は、SRAMセルに格納された論理状態に対応する信号を出力する。SRAMセルに対する書込みを行うとき、SRAMセルに関連するビット線は、相補的に所定の論理状態にされ、対応するワード線は、SRAMセルにアクセスするように起動され、SRAMセルは、論理ハイを一方のポートに示すとともに論理ローを他方のポートに示す特定の論理状態にラッチされる。

### [00006]

SRAMアレイにおいて、読出しサイクル及び書込みサイクルは、ビット線の放電及び充電動作のために電力の大部分を消費する。動作の頻度、動作電圧及び各ビット線の容量は、各動作で消費される電力を決定する際の要因となる。Cをビット線の容量とし、Vを使用電圧(すなわち、ビット線の振幅電圧(swing voltage))とし、Fをビット線を充電及び放電する頻度とした場合、消費される電力をC\*V²\*Fとして計算することができる。

## 【発明の概要】

【発明が解決しようとする課題】

#### [0007]

本発明の態様は、低電力消費のスタティックランダムアクセスメモリ(SRAM)を提供する。

## [0008]

典型的なSRAMアレイにおいて、ビット線がプリチャージされ又は書き込まれるとき、ビット線の少なくとも一方の電圧は、電源電圧になる。しかしながら、SRAM行アクセスゲートは、全電源電圧をパスせず、代わりに、電源電圧よりもしきい値電圧だけ低い電圧までパスすることができる。したがって、ビット線の電圧振幅を低減することによって、電力を電圧低下の2乗に比例して低減することができる。したがって、本発明の態様は、電力消費を低減するために電源電圧より低い電圧までビット線を充電するように構成されたSRAMアレイを提供する。

## 【課題を解決するための手段】

## [0009]

本発明の一実施の形態は、スタティックランダムアクセスメモリ(SRAM)セルのビット線ドライバであって、第1の電圧を供給する第1の電源と、第1の電圧よりも低い第2の電圧を供給する第2の電源と、SRAMセルに対する書込みを行うときにビット線及び反転ビット線を駆動するように構成された書込み回路と、SRAMセルの内容の読出しを行う前にビット線及び反転ビット線をプリチャージするように構成されたプリチャージ回路と、を備え、ビット線ドライバがビット線又は反転ビット線をハイ状態にするときに、ビット線ドライバは、第1の電圧よりも一つのトランジスタのしきい値電圧だけ低い電圧をビット線又は反転ビット線に供給するビット線ドライバを提供する。

### [0010]

一実施の形態において、書込み回路がビット線をハイ状態にするときに、書込み回路は 、第1の電圧よりも一つのトランジスタのしきい値電圧だけ低い電圧をビット線に供給し

20

30

40

50

、書込み回路が反転ビット線をハイ状態にするときに、書込み回路は、第1の電圧よりも 一つのトランジスタのしきい値電圧だけ低い電圧を反転ビット線に供給する。

## [0011]

書込み回路は、一対のプルアップ回路と、各々が一対のプルアップ回路の反対の側のプルアップ回路のゲートに交差結合したゲートを有する一対のプルダウン回路と、各々がプルアップ回路の対応するものと一対のプルダウン回路の同一の側のプルダウン回路との間に介在した一対のアクセス回路と、を有してもよく、書込み回路は、データ信号及び高いの一次のでは、まれて、一対のプルアップ又はプルダウンしてもよい。一実施の形態において、一対のプルアップ回路は、第1の電源とビット線との間に結合した第2の目に結合した第1のトランジスタと、第1の電源と反転ビット線との間に結合した第2のトランジスタと、第2の電源と反転ビット線との間に結合した第2のトランジスタと、第3のトランジスタとにット線との間に介在した第6のトランジスタと、第3のトランジスタと反転ビット線との間に介在した第6のトランジスタと、を有する。のトランジスタと反転ビット線との間に介在した第3のトランジスタと、を有する。

## [0012]

第1のトランジスタ及び第4のトランジスタを、共にオン及びオフにしてもよく、第2のトランジスタ及び第3のトランジスタを、共にオン及びオフにしてもよく、第5のトランジスタ、第6のトランジスタ、第7のトランジスタ及び第8のトランジスタを、共にオン及びオフにしてもよい。第1のトランジスタ及び第4のトランジスタを、データ信号に従ってオン及びオフにしてもよく、第2のトランジスタ及び第3のトランジスタを、データ信号の反転である反転データ信号に従ってオン及びオフにしてもよく、第5のトランジスタ、第6のトランジスタ、第7のトランジスタ及び第8のトランジスタを、書込み信号に従ってオン及びオフにしてもよい。

## [0013]

第1のトランジスタ及び第3のトランジスタの少なくとも一方及び第2のトランジスタ及び第4のトランジスタの少なくとも一方は、SRAMセルの行アクセストランジスタと同一の型のトランジスタである。一実施の形態において、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第6のトランジスタ、第7のトランジスタ及び第8のトランジスタは、n型トランジスタである。他の実施の形態において、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ、第3のトランジスタ、第3のトランジスタである。タ、第4のトランジスタ、第7のトランジスタ及び第8のトランジスタは、n型トランジスタであり、第5のトランジスタ及び第6のトランジスタは、p型トランジスタである。【0014】

一実施の形態において、プリチャージ回路がビット線をハイ状態にするときに、プリチャージ回路は、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧をビット線に供給するように構成され、プリチャージ回路が反転ビット線をハイ状態にするときに、

プリチャージ回路は、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧を 反転ビット線に供給する。

## [0015]

プリチャージ回路は、プリチャージ信号に従って、ビット線を、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第1のプルアップ回路と、プリチャージ信号に従って、反転ビット線を、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第2のプルアップ回路と、反転プリチャージ信号に従ってビット線の電圧と反転ビット線とのバランスをとるバランス回路と、を有してもよい。一実施の形態において、第1のプルアップ回路は、第1の電源とビット線との間に介在した第1のトランジスタを有し、第2のプルアップ回路は、第1の電源と反転ビット線との間に介在した第2のトランジスタを有する。路は、ビット線と反転ビット線との間に結合した第3のトランジスタを有する。

#### [0016]

第1のトランジスタ及び第2のトランジスタは、SRAMセルの行アクセストランジスタと同一の型のトランジスタであってもよい。一実施の形態において、第1のトランジスタ及び第2のトランジスタは、n型トランジスタであってもよい。

## [0017]

さらに、本発明の他の実施の形態の態様は、スタティックランダムアクセスメモリ(S RAM)アレイであって、行配置された複数のワード線であって、ワード線の各々が複数 のワード信号のうちの対応するワード信号を供給する複数のワード線と、列配置された複 数のビット線であって、ビット線の各々が複数のビット信号のうちの対応するビット信号 を供給する複数のビット線と、ビット線と共に列配置された複数の反転ビット線であって 、反転ビット線の各々が複数の反転ビット信号のうちの対応する反転ビット信号を供給し 、対応する反転ビット信号は、同一の列においてビット線のうちの対応するビット線によ って供給されるビット信号の反転である複数の反転ビット線と、第1の電圧を供給する第 1の電源と、第1の電圧よりも低い第2の電圧を供給する第2の電源と、行列配置された 複数のSRAMセルであって、SRAMセルの各々は、ワード線、ビット線及び反転ビッ ト線の各々の一つに対応する複数のSRAMセルと、ワード線を駆動するように構成され たワード線ドライバと、ビット線及び反転ビット線を駆動するように構成されたビット線 ドライバと、を備え、ビット線ドライバがビット線の一つをハイ状態にするときに、ビッ ト線ドライバは、第1の電圧よりもビット線ドライバの一つのトランジスタのしきい値電 圧だけ低い電圧をビット線の一つに供給し、ビット線ドライバが反転ビット線の一つをハ イ状態にするときに、ビット線ドライバは、第1の電圧よりもビット線ドライバの一つの トランジスタのしきい値電圧だけ低い電圧を反転ビット線の一つに供給するように構成さ れるSRAMアレイを提供する。

#### [0018]

ビット線ドライバは、複数の書込み回路を備えてもよく、書込み回路の各々は、ビット線のうちの一つのビット線、反転ビット線のうちの一つの反転ビット線及びSRAMセルの一つの列に対応し、書込み回路の各々は、一対のプルアップ回路と、各々が一対のプルアップ回路の反対の側のプルアップ回路のゲートに交差結合したゲートを有する一対のプルダウン回路と、各々がプルアップ回路の対応するものと一対のプルダウン回路の同一の側のプルダウン回路との間に介在した一対のアクセス回路と、を有してもよく、書込み回路の各々は、データ信号及び書込み信号に従ってビット線及び反転ビット線を選択的にプルアップ又はプルダウンしてもよい。

#### [0019]

一実施の形態において、一対のプルアップ回路は、n型トランジスタを有する。

## [0020]

ビット線ドライバは、複数のプリチャージ回路を有してもよく、プリチャージ回路の各々は、ビット線のうちの一つのビット線、反転ビット線のうちの一つの反転ビット線及びSRAMセルの一つの列に対応し、プリチャージ回路の各々は、プリチャージ信号に従って、ビット線を、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第1のプルアップ回路と、プリチャージ信号に従って、反転ビット線を、第1の電圧よりも一つのトランジスタのしきい値だけ低い電圧にプルアップするように構成された第2のプルアップ回路と、反転プリチャージ信号に従ってビット線の電圧と反転ビット線とのバランスをとるバランス回路と、を有してもよい。

## [0021]

一実施の形態において、第1のプルアップ回路及び第2のプルアップ回路は、 n 型トランジスタを有する。

#### [0022]

SRAMセルの各々は、対応するワード線に結合したゲート、対応する反転ビット線に結合したソース、及び、ドレインを備える第1のトランジスタと、対応するワード線に結合したゲート、対応するビット線に結合したソース、及び、ドレインを備える第2のトラ

10

20

30

40

ンジスタと、第2のトランジスタのドレインに結合したゲート、第2の電源に結合したソース、及び、第1のトランジスタのドレインに結合したドレインを備える第3のトランジスタと、第1のトランジスタのドレインに結合したゲート、第2の電源に結合したソース、及び、第2のトランジスタのドレインに結合したドレインを備える第4のトランジスタび、第1のトランジスタのドレインに結合したドレインを備える第5のトランジスタと、第1のトランジスタのドレインに結合したドレインを備える第5のトランジスタと、第1のトランジスタのドレインに結合したドレインを備える第6のトランジスタと、を有してもよく、第1のトランジスタ、第2のトランジスタ、第3のトランジスタ及び第4のトランジスタは、n型トランジスタであってもよく、第5のトランジスタ及び第6のトランジスタは、p型トランジスタであってもよい。

[0023]

添付図面は、本発明の例示的な実施の形態を示し、明細書と共に、本発明の原理を説明する役割を果たす。

【図面の簡単な説明】

[0024]

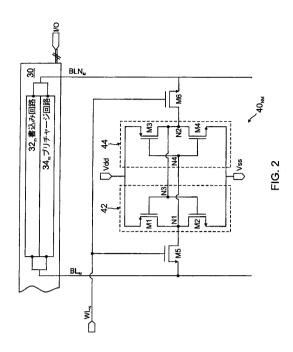

【図1】図1は、本発明の一実施の形態による低電力SRAMアレイの回路図である。

【図2】図2は、図1のSRAMアレイのSRAMセルの回路図である。

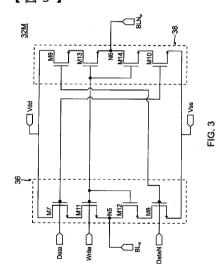

【図3】図3は、図1のSRAMアレイのビット線ドライバの書込み回路の回路図である。

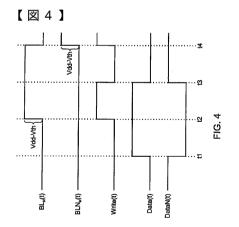

【図4】図4は、図3の書込み回路のタイミング図である。

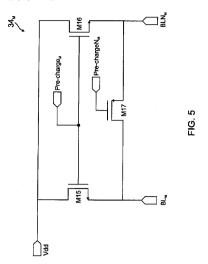

【 図 5 】 図 5 は、 図 1 の S R A M アレイのビット線ドライバのプリチャージ回路の回路図である。

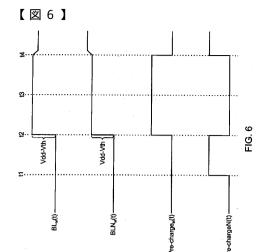

【図6】図6は、図5のプリチャージ回路のタイミング図である。

【発明を実施するための形態】

[0025]

本発明の実施の形態の態様は、ビット線を電源電圧よりもトランジスタのしきい値電圧だけ低い電圧にすることができる書込み回路及び / 又はプリチャージ回路を有する低電力スタティックランダムアクセスメモリ(SRAM)アレイを提供する。

[0026]

本発明の実施の形態によれば、SRAMセルは、対応するビット線を介してビット線ドライバに結合される。ここでは、ビット線ドライバは、書込み回路及びプリチャージ回路を有する。書込み回路は、差動的にビット線を駆動することによって論理状態をSRAMセルに書き込むために設けられる。プリチャージ回路は、センス増幅器によってSRAMセルを読み出す前にビット線をハイ状態にプリチャージするように構成される。書込み回路及び/又はプリチャージ回路は、ビット線電圧を電源電圧よりもトランジスタのしきい値だけ低い電圧にすることによってビット線をハイ状態にしてもよい。

[0027]

書込み回路及びプリチャージ回路はそれぞれ、複数のトランジスタを有する。ビット線に結合された書込み回路及び/又はプリチャージ回路のトランジスタの少なくとも二つは、SRAMセルの行アクセストランジスタと同一の型(例えば、NMOS型トランジスタ)としてもよい。同一の型のトランジスタを用いることによって、ビット線の電圧振幅は、行アクセストランジスタの動作電圧(例えば、電源電圧から行アクセストランジスタの動作電圧(例えば、電源電圧から行アクセストランジスタの動作電圧を引いた電でに振幅は、信頼性のある動作を提供するが、(電源電圧でビット線を駆動する場合に比べて)電力を著しく低減する。例えば、1・8 V電源及び0・8 Vしきい値電圧を有する180nmプロセスに対して、電力の低減は、3・24(すなわち、1・8²/(1・8・0・8)²)の倍数となる。したがって、本発明の実施の形態によるSRAMアレイを用いるとき、領域を増大することがで、追加の外部電圧なしで又はクロック動作を増大することなく電力を低減することがで

10

20

30

40

きる。

## [0028]

以下の詳細な説明において、本発明の所定の実施の形態のみを、例示のために示すとともに説明する。当業者が認識するように、発明を、多数の異なる形式で実施してもよく、ここで説明する実施の形態に限定されるものと解釈すべきでない。代わりに、詳細な説明を、添付した特許請求の範囲及びその等価物を含むものと解釈すべきである。また、本発明において、要素が他の要素に「結合」(例えば、電気的に結合又は接続)されているものとして言及するとき、要素を、他の要素に直接結合することができ、又は、介在する一つ以上の介在要素によって間接的に他の要素に結合することができる。以後、同様な参照番号は同様な要素を言及する。

[0029]

図1は、本発明の一実施の形態による低電力SRAMアレイの回路図を示す。図1において、SRAMアレイ10は、行列配置された複数のSRAMセル40を有する。SRAMアレイは、行方向に延在する複数のワード線WL0~WLnを駆動するワード線ドライバ20と、列方向に延在するとともにワード線WL0~WLnと交差する複数のビット線BL0~BLm及び複数の反転ビット線BLN0~BLNmを駆動するビット線ドライバ30と、を有する。

## [0030]

SRAMセル40は、行及び列に配置され、ワード線WL0~WLn、ビット線BL0~BLm及び反転ビット線BLN0~BLNmの交差領域に位置する。各SRAMセル40は、ワード線WL0~WLn、ビット線BL0~BLm及び反転ビット線BLN0~BLNmの対応するものに結合される。SRAMセル40を、行アドレス及び列アドレスを有する固有のメモリアドレスによって識別してもよい。特定のワード線WL0~WLnを作動させるためにワード線ドライバ20を制御するとともに特定のビット線対BL0/BLN0~BLm/BLNmを作動させるためにビット線ドライバ30を制御することによって、固有のSRAMセル40を読み出し又は書き込んでもよい。

#### [0031]

SRAMアレイ10は、第1の電圧Vdd(すなわち、電源電圧)を供給する第1の電源50と、第1の電圧より低い第2の電圧Vssを供給する第2の電源55と、を有する。本発明の実施の形態において、第1の電圧Vddは、約1.8Vであり、第2の電圧Vssは、約0V(すなわち、接地)である。第1の電圧Vdd及び第2の電圧VssをSRAM40、ワード線ドライバ20及びビット線ドライバ30にそれぞれ供給してもよい

[0032]

さらに、SRAMアレイ10は、入力/出力バスI/Oを介して入力/出力データを送信及び受信してもよい。入力/出力データは、格納されるデータ、検索されたデータ、メモリアドレス情報、クロック信号等を含んでもよい。入力/出力バスを、外部装置(図示せず)、例えば、マイクロコントローラに結合してもよい。入力/出力バスI/Oを、ワード線ドライバ20及びビット線ドライバ30に結合してもよいが、本発明はそれに限定されず、入力/出力バスI/Oを、ワード線ドライバ20及びビット線ドライバ30を制御することができるSRAMコントローラ(図示せず)に結合してもよい。

[0033]

したがって、本発明の態様によるSRAMアレイ10は、アドレス(すなわち、行及び列)によりデータのビットをSRAMセル40に格納するとともにSRAMセル40のデータのビットを検索する。

## [ 0 0 3 4 ]

SRAMセルの動作を、図2を参照しながら詳細に説明する。図2は、図1のSRAM アレイのSRAMセルの回路図を示す。図2のSRAMセル40nmは、n番目の行及び m番目の列のSRAMセル40に対応する(ここで、n及びmは、正の実数である。)。

[0035]

10

20

30

20

30

40

50

図 2 の S R A M セル 4 0 n m は、 6 個のトランジスタの低電圧かつ低電力の S R A M セル 7 0 n m は、 第 1 のインバータ 4 2 を有し、 第 1 のインバータ 4 2 は、 第 1 の電圧 V d d (すなわち、電源電圧)と第 1 のインバータ 4 2 の出力ノード N 1 との間に結合した第 1 のプルアップトランジスタ M 1 を有する。 第 1 のインバータ 4 2 は、出力ノード N 1 と第 2 の電圧 V s s (すなわち、接地)との間に結合した第 1 のプルダウントランジスタ M 2 も有する。 S R A M セル 4 0 n m は、 第 2 のインバータ 4 4 も有し、 第 2 のインバータ 4 4 は、 第 2 のプルアップトランジスタ M 3 及び第 2 のプルダウントランジスタ M 4 を有する。 第 2 のプルアップトランジスタ M 3 は、 第 1 の電圧 V d d と 第 2 のインバータ 4 4 の出力ノード N 2 との間に結合される。 第 2 のプルダウントランジスタ M 4 は、 出力ノード N 2 と第 2 の電圧 V s s との間に結合される。

[0036]

第1のインバータ42及び第2のインバータ44は交差結合される。すなわち、第1のインバータ42の入力ノードN3は、第2のインバータ44の出力ノードN2に結合され、第2のインバータ44の入力ノードN4は、第1のインバータ42の出力ノードN1に結合される。交差結合されたインバータ42及び44は、双安定ラッチ回路としての機能を果たす。双安定ラッチは、二つのあり得る状態の一方をとることができるようにするためにトランジスタ利得及び増強帰還(reinforcing feedback)に依存する。双安定ラッチがなる状態は、データのビット、すなわち、1又は0を表す。双安定ラッチを、外部信号を加えることによってのみ一方の状態から他方の状態にプログラムする(又は変化させる)ことができる。したがって、双安定ラッチに対するアクセスは、外部信号を加えるとともに現在の状態を保存するように制御される。

[0037]

双安定ラッチに対するアクセスを制御するために、SRAMセル40nmは、第1のアクセストランジスタM5及び第2のアクセストランジスタM6を有してもよい。第1のアクセストランジスタM5を、第1のインバータ42の出力ノードN1とm番目の列のビット線BLmとの間に結合してもよい。第2のアクセストランジスタM6を、第2のインバータ44の出力ノードN2とm番目の列の反転ビット線BLmとの間に結合してもよい。第1のアクセストランジスタM6のゲートは、n番目の行のワード線WLnに結合される。

[0038]

双安定ラッチへのアクセスがアクセストランジスタ(例えば、行アクセストランジスタ)を介するので、SRAMセル40nmによって格納される電圧は、第1の電圧(すなわち、電源電圧)よりも低くなる。例えば、アクセスが(図2に示すように)第1の電圧Vdddをn型トランジスタのゲートに印加することによって制御される場合、ソースは、ゲート電圧からアクセストランジスタのしきい値電圧Vthまでしか上昇しない。すなわち、アクセストランジスタの出力は、第1の電圧Vddよりもしきい値電圧Vthだけ低い電圧となる。例えば、電源電圧(すなわち、ドレイン及びゲートの電圧)が1.8Vであり、しきい値電圧Vthが0.8Vである場合、SRAMセルに格納される電圧(すなわち、ソース電圧)は、1Vとなる。

[0039]

ワード線W L n を、 n 番目の行の S R A M セル 4 0 n に対応するワード線ドライバ 2 0 の部分によって作動させてもよい。 S R A M セル 4 0 n m に対するアクセスは、ワード線 W L n によってイネーブルされ、これによって、第 1 のアクセストランジスタ M 5 及び第 2 のアクセストランジスタ M 6 を制御し、そして、第 1 のインバータ 4 2 及び第 2 のインバータ 4 4 をビット線 B L N m に結合するか否かの制御を行う。

[0040]

SRAMセル40nmは、三つの異なる状態:待機、書込み及び読出しを有する。これらの状態の動作は、以下の通りである。

[0041]

待機中には、ワード線WLnはアサートされず、第1のアクセストランジスタM5及び

20

30

40

50

第2のアクセストランジスタM6は、第1のインバータ42及び第2のインバータ44をビット線BLm及び反転ビット線BLNmから切り離す。二つの相互結合されたインバータ42及び44は、これらが第1の電圧Vdd及び第2の電圧Vssに接続されている限り互いに強化(reinforce)し続ける。このようにして、SRAMセル40nmに格納されたデータビットが保存される。

## [0042]

書込みサイクルは、書き込まれる値をビット線に加えることによって開始される。ビット線が相補的な対すなわちビット線BLm及び反転ビット線BLNmとして設けられるので、ビット線BLmは、書き込まれる値を表す論理状態にされ、反転ビット線BLNmは、相補的な値にされる。例えば、書き込まれる値が0である場合、ビットラインBLmは、論理レベル0にされ、反転ビット線は、論理レベル1にされる。次に、ワード線WLnは、第1のアクセストランジスタM5及び第2のアクセストランジスタM6をオンにするためにアサートされる。したがって、ビット線BLm及びBLNmは、交差結合されたインバータ42及び44に結合される。ビット線ドライバ30が、SRAMセル40nmの比較的弱い(relatively weak)トランジスタよりも著しく強くなるように設計されているので、SRAMセル40nmの以前の状態が上書きされる。したがって、値が格納される

## [0043]

本発明の実施の形態によれば、ビット線BL0~BLm及び反転ビット線BLN0~BLNmは、ビット線ドライバ30に含まれる複数の書込み回路32によって駆動される。書込み回路32は、SRAMセル40の列に対応する。したがって、SRAMセル40mのm番目の列は、m番目の書込み回路32mによって駆動される。書込み回路32を、1の論理レベルをビット線BL0~BLm及び反転ビット線BLN0~BLNmに書き込むときにビット線BL0~BLm及び反転ビット線BLN0~BLNmを第1の電圧Vddよりもトランジスタのしきい値電圧だけ低い電圧にするように設計してもよい。したがって、ビット線対を駆動することによって消費される電力を低減することができる。書込み回路32の詳細な説明を、図3及び図4に関連して後に行う。

#### [0044]

読出しサイクルは、ビット線BLmと反転ビット線BLNmの両方を論理レベル1にプリチャージすることによって開始される。その後、対応するワード線WLnは、アクセストランジスタM5及びM6の両方をイネーブルするワード線ドライバ20によってアサートされる。その後、SRAMセル40nmに格納された値は、0論理レベルを有する出力ノードに結合された相補的なビット線対の線の一方をプルダウンすることによって、ビット線BLm及び反転ビット線BLNmに転送される。その後、相補的なビット線対は、格納されたビット値を検出するためにセンス増幅器(図示せず)によって検知される。

## [0045]

本発明の実施の形態によれば、ビット線BL0~BLm及び反転ビット線BLN0~BLN0は、ビット線ドライバ30に含まれる複数のプリチャージ回路によってプリチャージされる。プリチャージ回路34は、SRAMセル40の列に対応する。したがって、SRAMセル40mのm番目の列は、m番目のプリチャージ回路34mによってプリチャージされる。プリチャージ回路を、ビット線BL0~BLm及び反転ビット線BLN0~BLNmをプリチャージするときに第1の電圧よりもトランジスタのしきい値電圧だけ低い電圧までビット線BL0~BLm及び反転ビット線BLN0~BLNmをプリチャージするように設計することができる。したがって、ビット線対をプリチャージすることによって消費される電力を低減することができる。プリチャージ回路34mの詳細な説明を、図5及び図6に関連して後に行う。

#### [0046]

SRAMセル40nmを、n型アクセストランジスタを有する6T SRAMセルに関連して図示及び説明したが、本発明は、それに限定されない。例えば、本発明の実施の形態は、8T又は10T SRAMセル及び/又はp型アクセストランジスタを有するSR

20

30

40

50

AMセルを提供してもよい。

## [0047]

本発明の実施の形態による書込み回路32を、図3及び図4に関連して説明する。図3は、図1のSRAMアレイのビット線ドライバの書込み回路の回路図を示す。図4は、図3の書込み回路のタイミング図である。図3に示す書込み回路32mは、SRAMアレイ10のm番目の列に関連するSRAMセル40m、ビット線BLm及び反転ビット線BLNmに対応する。

## [0048]

上述したように、SRAMセル40は、第1の電圧Vddよりもトランジスタのしきい値電圧Vthだけ低い電圧として論理1を格納してもよい。ビット線対によって消費される電力がビット線対の電圧振幅の2乗に比例するので、第1の電圧Vddよりもしきい値電圧Vthだけ低い電圧よりも高い電圧をビット線対に供給すると、必要以上に多い電力を消費しうる。したがって、本発明の実施の形態による書込み回路32が、ビット線BL0~BLM又は反転ビット線BLN0~BLNmのいずれかに論理レベル1を書き込むとき、本発明の実施の形態による書込み回路32は、第1の電圧Vddよりもトランジスタのしきい値電圧Vthだけ低い電圧を供給することによってそのような書込みを行う。したがって、電力消費を低減する。

### [0049]

図3において、書込み回路32mは、m番目のビット線BLm及び反転ビット線BLNmに結合される。書込み回路32mは、データ信号Data、(Dataに対する相補的な信号である)反転データ信号DataN及び書込み信号Writeに従ってSRAMセル40mの列にビット情報を送信してもよい。データ信号Data、反転データ信号DataN及び書込み信号Writeを、入力/出力バスI/Oから受信する入力/出力データに含めてもよい。

## [0050]

図3の書込み回路32mは、8個のトランジスタの低電圧及び低電力の書込み回路である。書込み回路32は、第1のインバータ36を有してもよく、第1のインバータ36は、第1の電圧Vdd(すなわち、電源電圧)と第1のインバータ36の出力ノードN5との間に結合された第1のプルアップトランジスタM7を有する。第1のインバータ36は、第1のインバータ36の出力ノードN5と第2の電圧Vss(すなわち、接地)との間に結合された第1のプルダウントランジスタM8を有してもよい。第1のインバータ36の出力ノードN5は、対応するビット線BLmに結合される。書込み回路32は、第2のプルアップトランジスタM9及び第2のプルダウントランジスタM10を有する第2のインバータ38を有してもよい。第2のプルアップトランジスタM9を、第1の電圧Vddと第2のインバータ38の出力ノードN6との間に結合してもよい。第2のプルアップトランジスタM10を、第2のインバータ38の出力ノードN6と第2の電圧Vssとの間に結合してもよい。第2のインバータ38の出力ノードN6は、対応する反転ビット線BLNmに結合される。

## [0051]

第1のプルアップトランジスタM7及び第2のプルダウントランジスタM10は、共にオン及びオフされるように構成される。したがって、第1のプルアップトランジスタM7のゲートを、第2のプルダウントランジスタM10のゲートに結合してもよい。さらに、第1のプルアップトランジスタM7及び第2のプルダウントランジスタM10は、データ信号Dataに結合されるとともにデータ信号Dataに従ってオン及びオフに切り替わってもよい。

# [0052]

第2のプルアップトランジスタM9及び第1のプルダウントランジスタM8は、共にオン及びオフされるように構成される。したがって、第2のプルアップトランジスタM9のゲートを、第1のプルダウントランジスタM8のゲートに結合してもよい。さらに、第2のプルアップトランジスタM9及び第1のプルダウントランジスタM8は、反転データ信

20

30

40

50

号 DataNに結合されるとともに反転データ信号 DataNに従ってオン及びオフに切り替わってもよい。

## [0053]

したがって、第1のインバータ36及び第2のインバータ38は、データ信号Data及び反転データ信号DataNに従って出力ノードを相補的に駆動するように構成される。例えば、データ信号Dataがハイであるとともに反転データ信号DataNがローであるとき、第1のインバータ36の出力はハイになるとともに第2のインバータ38の出力はローになる。

## [0054]

書込み回路32mは、書込み信号Writeに従ってビット線BLNm及び反転ビット 線BLNmに対するアクセスを制御する一対のアクセス制御回路を更に有してもよい。す なわち、インバータ36及び38は、書込み信号Writeがイネーブルされたときにの みビット線BLNm及び反転ビット線BLNmを駆動してもよい。各アクセス回路を、書 込み回路32の対応するインバータに関連させてもよい。第1のアクセス回路は、第1の アクセストランジスタM11及び第2のアクセストランジスタM12を有してもよい。第 1 のアクセストランジスタM11を、第1のインバータ36の第1のプルアップトランジ スタM7と出力ノードN5との間に介在させてもよく、第2のアクセストランジスタM1 2 を、 第 1 のインバータ 3 6 の第 1 のプルダウントランジスタ M 8 と出力ノード N 5 との 間に介在させてもよい。さらに、第2のアクセス回路は、第3のアクセストランジスタM 13及び第4のアクセストランジスタM14を有してもよい。第3のアクセストランジス タM13を、第2のインバータ38の第2のプルアップトランジスタM9と出力ノードN 6 との間に介在させてもよく、第4のアクセストランジスタM14を、第2のインバータ 38の第2のプルダウントランジスタM10と出力ノードN6との間にとの間に介在させ てもよい。第1~4のアクセストランジスタのゲートを、書込み信号Writeがイネー ブルされたときにビット線BLm及び反転ビット線BLNmへのアクセスをイネーブルに するために書込み信号Writeに結合してもよい。

#### [0055]

第 1 のインバータ 3 6 及び第 2 のインバータ 3 8 のトランジスタの少なくとも一つは、 SRAM セル 4 0 mのアクセストランジスタM 5 及びM 6 と同一型であってもよい。例えば、第 1 のプルアップトランジスタM 7 及び第 2 のプルアップトランジスタM 9 は、SRAM セル 4 0 mのアクセストランジスタM 5 及びM 6 と同一型であってもよい。しかしながら、本発明は、それに限定されず、第 1 のアクセストランジスタM 1 1 及び第 3 のアクセストランジスタM 1 3 は、SRAM セル 4 0 mのアクセストランジスタM 5 及びM 6 と同一型であってもよく、書込み回路 3 2 mのトランジスタM 7 ~ M 1 4 の全ては、SRAM セル 4 0 mのアクセストランジスタM 5 及びM 6 と同一型であってもよい。

## [0056]

図3において、トランジスタM7~M14のそれぞれを、n型トランジスタとして表現する。さらに、上述したように、図3の書込み回路32mを、アクセストランジスタM5及びM6をn型トランジスタとして表現する図2のSRAMセル40mとともに用いてもよい。本実施の形態において、アクセストランジスタM5及びM6がn型トランジスタであるので、アクセストランジスタM5及びM6は、ゲート電圧よりもしきい値電圧Vthだけ低い電圧のみをソースにおいて出力してもよい。例えば、ゲート及びドレインが第1の電圧Vddで駆動される場合、出力電圧(例えば、SRAMセル40mに格納される電圧)は、第1の電圧Vddからしきい値電圧Vthを減算した電圧となる。

## [0057]

また、本実施の形態において、書込み回路32mの第1のプルアップトランジスタM7及び第2のプルアップトランジスタM9がn型トランジスタであるので、第1のプルアップトランジスタM7及び第2のプルアップトランジスタM9も、ゲート電圧よりもしきい値電圧だけ低い電圧までのみをパスしてもよい。したがって、ゲート電圧が第1の電圧Vddcあり、しきい値電圧がSRAMセル40mのアクセストランジスタM5及びM6と

20

30

40

50

同一である場合、ビット線BLm及び反転ビット線BLNmに供給されるハイレベルの電圧は、SRAMセル40mにパスすることができるレベルと同一レベルまでとしてもよい。したがって、書込み回路32mからのハイの電圧出力を低減することができ、そして、電圧の減少の2乗に比例するSRAMアレイ10の消費を低減することができる。例えば、1.8V電源電圧及び0.8Vしきい値電圧を有するSRAMアレイ10に対して、電力の低減は、3.24(すなわち、1.8²/(1.8-0.8)²)の倍数となる。

書込み回路32mの動作を、図4を参照しながら更に説明する。図4は、書込みドライバ32mに関連するタイミング図の一例を示す。図に示すように、書込み回路32mは、書込み信号Writeがイネーブルされたときにのみ信号をビット線BLm及び反転ビット線BLNmに信号を出力する。例えば、データ信号Dataがハイであり、反転データ信号Dataがハイであり、反転データの番32mは、ビット線BLm及び反転ビット線BLNmに信号を出力しない。しかしながら、データ信号がハイであり、反転データ信号DataNがローであり、かつ、書込み信号Writeがハイであるとき、書込み回路32mは、論理ハイをビット線BLmに出力するとともに論理ローを反転ビット線BLNmに出力する。ここでは、論理ハイは、第1の電圧Vddよりも書込み回路32mの第1のプルアップトランジスタM7のしきい値電圧Vthだけ低い電圧によって表される。

[0059]

プリチャージ回路 3 4 のプリチャージ回路 3 4 mを、図 5 及び図 6 に関連して説明する。図 5 は、図 1 の S R A M アレイのビット線ドライバのプリチャージ回路の回路図を示す。図 6 は、図 5 のプリチャージ回路のタイミング図である。上述した書込み回路と同様に、本発明の実施の形態によるプリチャージ回路は、ビット線対を、エネルギー消費を減少するために供給電圧からトランジスタのしきい値電圧を減算した電圧まで充電する。

[0060]

プリチャージ回路34mは、m番目の列のSRAMセル40m並びにm番目のビット線BLm及び反転ビット線BLNmに結合される。上述したように、プリチャージ回路は、読出しサイクルの開始時にビット線BLm及び反転ビット線BLNmをプリチャージする。プリチャージ回路34mを、プリチャージ信号Pre‐charge及びプリチャージ信号Pre‐charge及びプリチャージ信号Pre‐charge及び反転プリチャージ信号Pre‐charge及び反転プリチャージ信号Pre‐charge及び反転プリチャージ信号Pre‐charge及び反転プリチャージ信号Pre‐charge及び反転プリチャージ信号Pre‐chargeNで、各々がSRAMセル40の列に対応する複数のプリチャージ信号及び反転プリチャージ信号の一つとしてもよい。

[0061]

プリチャージ回路 3 4 m は、第 1 のプルアップトランジスタ M 1 5 及び第 2 のプルアップトランジスタ M 1 5 は、第 1 の電圧 V d d とビット線 B L m との間に結合される。第 2 のプルアップトランジスタ M 1 6 は、第 1 の電圧 V d d と反転ビット線 B L N m との間に結合される。プルアップトランジスタは、プリチャージ信号 P r e - c h a r g e に従ってオンに切り替えられる。

[0062]

第 1 のプルアップトランジスタM 1 5 及び第 2 のプルアップトランジスタM 1 6 は、 S R A M セル 4 0 n m のアクセストランジスタM 5 及びM 6 と同一型であってもよい。したがって、プリチャージ回路 3 4 m は、ビット線 B L m 及び反転ビット線 B L N m を、 S R A M セル 4 0 m のアクセストランジスタM 5 及びM 6 が S R A M セル 4 0 m にパスすることができる電圧又はその付近まで充電してもよい。例えば、 S R A M セル 4 0 m のアクセストランジスタ M 5 及び M 6 が n 型トランジスタであるとき、第 1 のプルアップトランジスタ M 1 5 及び第 2 のプルアップトランジスタ M 1 6 も n 型トランジスタであってもよい。したがって、 S R A M セル 4 0 m のアクセストランジスタ M 5 及び M 6 並びにプリチャ

20

30

40

ージ回路のプルアップトランジスタM 1 5 及びM 1 6 が全て、ゲートにおいて第 1 の電圧 V d d で駆動されるとともに同一のしきい値電圧 V t h を有する場合、読出しサイクル中に S R A M セル 4 0 mにパスされる電圧は、ビット線 B L m 及び反転ビット線 B L N m に プリチャージされた電圧と同一である、すなわち、第 1 の電圧 V d d からしきい値電圧 V t h を減算した電圧と同一である。したがって、S R A M アレイ 1 0 の電力消費は低減される。

#### [0063]

さらに、プリチャージ回路 3 4 m は、バランストランジスタ M 1 7 を有してもよい。バランストランジスタは、ビット線 B L m を反転ビット線 B L N m に結合して二つの線の電圧のバランスを取ってもよい。バランストランジスタ M 1 7 は、反転プリチャージ信号 P r e - c h a r g e N がイネーブルされたときにオンに切り替わってもよい。

## [0064]

プリチャージ回路34mの動作を、図6を参照しながら更に説明する。図6は、書込み ドライバ34mに関連するタイミング図の一例を示す。特に、図6は、ビット線BLm及 び反転ビット線BLNmの信号、プリチャージ信号Pre‐charge並びに反転プリ チャージ信号Pre‐chargeNの関係を時間と共に示す。時刻t0において、全て の信号は接地電圧である(これを読出しサイクル直前としてもよい。)。時刻t1におい て、プリチャージ信号Pre‐chargeはローであり、反転プリチャージ信号Pre - chargeNはハイである。ここでは、ビット線対は、バランストランジスタM 1 7 を通じて結合されるが、電圧レベルが接地レベルであるので、観察できる電圧のバランス の保持が生じない。時刻t3において、プリチャージ信号Pre-chargeはハイ( すなわち、第1の電圧Vdd)であり、反転プリチャージ信号Pre‐chargeNは ローである。ここでは、第1のプルアップトランジスタM15及び第2のプルアップトラ ンジスタM16は、第1の電圧Vddよりもしきい値電圧Vthだけ低い電圧を出力する ためにオンに切り替えられる。この状態は、時刻t3で保持されるが、時刻t4において 、プリチャージ信号Pre‐chargeはローになり、反転プリチャージ信号Pre‐ c h a r g e N はハイになる。ここでは、バランストランジスタM17はオンであり、ビ ット線対の電圧はバランスが保たれる。電圧の差は、例えば、トランジスタのしきい値電 圧の差に起因する。

# [0065]

したがって、本発明の実施の形態は、低電力ビット線ドライバを有する低電力かつ低電圧のSRAMセルを提供する。電力を低減するために、ビット線ドライバは、相補的なビット線対の電圧振幅を低減する。この電圧振幅を低減することによって、SRAMセルアレイによって消費される電力を、電圧低減の2乗に従って低減することができる。

# [0066]

本発明による低電力 S R A M アレイの実施の形態を所定の例示的な実施の形態に関連して図示及び説明したが、発明は上述した実施の形態に限定されるものではなく、添付した特許請求の範囲の精神及び範囲内に含まれる種々の変形及び同等な配置をカバーすることを意図するものと理解すべきである。例えば、本発明の実施の形態を、ビット線ドライバに本発明によるプリチャージ回路と書込み回路の両方を有するものとして説明したが、本発明の実施の形態は、それに限定されるものではなく、ビット線ドライバに一方、他方又は両方を有してもよい。

Vess So Vess S

【図2】

【図3】

【図5】

## フロントページの続き

(72)発明者 ミッキー ハリス

アメリカ合衆国,カリフォルニア 93436,ロンポク,ライジェル アベニュ 4063

(72)発明者 ワシム カルド

アメリカ合衆国,テキサス 78717,オースティン,オールド ボールディ ドライブ 16 225

審査官 後藤 彰

(56)参考文献 特開2007-066509(JP,A)

特開平02-146188(JP,A)

特開平04-102294(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 11/412

G11C 11/413

G11C 11/417