(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FI

(11)特許番号

特許第3987659号 (P3987659)

(45) 発行日 平成19年10月10日(2007.10.10)

(24) 登録日 平成19年7月20日 (2007.7.20)

(51) Int.C1.

HO1L 23/12 (2006.01) HO1L 25/04 (2006.01) HO1L 23/12 3O1Z HO1L 25/04 Z

HO1L 25/04 (2006.01) HO1L 25/18 (2006.01)

請求項の数 1 (全 10 頁)

(21) 出願番号 特願平11-208188

(22) 出願日 平成11年7月22日 (1999.7.22)

(65) 公開番号 特開2001-35967 (P2001-35967A)

(43) 公開日 平成13年2月9日 (2001.2.9) 審査請求日 平成18年1月16日 (2006.1.16) (73)特許権者 000006633

京セラ株式会社

京都府京都市伏見区竹田鳥羽殿町6番地

(72) 発明者 前谷 麿明

京都府相楽郡精華町光台3丁目5番地 京セラ株式会社 中央研究所

内

審査官 菅野 智子

最終頁に続く

#### (54) 【発明の名称】高周波半導体装置

## (57)【特許請求の範囲】

#### 【請求項1】

誘電体基板の上面に高周波半導体素子を収容する凹部を有し、該凹部の開口周辺に線路導体が形成されるとともに、下面および前記凹部底面に接地導体が形成された配線基板と、該配線基板上に前記凹部の開口を覆うように取着され、下面周辺部に形成された接続電極が前記線路導体に当接接続された実装用配線基板と、該実装用配線基板の下面に形成された実装電極に導体バンプを介して電気的に接続された高周波半導体素子とを具備する高周波半導体装置であって、前記実装用配線基板は、前記凹部の開口寸法より大きく、かつ前記主誘電体層と、その下面に積層された前記開口寸法より小さく、かつ前記主誘電体層より比誘電率が小さい副誘電体層と、前記主誘電体層の下面周辺部に形成された前記接続電極から前記主誘電体層および前記副誘電体層間にかけて形成された実装用線路導体と、該実装用線路導体を前記副誘電体層の下面に形成された前記実装電極に電気的に接続する貫通導体とから成ることを特徴とする高周波半導体装置。

【発明の詳細な説明】

[0001]

### 【発明の属する技術分野】

本発明はマイクロ波もしくはミリ波を用いた通信機器もしくはセンサ等に使用される高周波半導体装置に関し、特に高周波半導体素子の実装構造を改善した高周波半導体装置に関する。

[0002]

20

#### 【従来の技術】

従来、マイクロ波もしくはミリ波帯において動作する高周波半導体素子を主な回路素子とする高周波電子回路モジュールにおいては、高周波半導体素子が誘電体基板を用いた高周波半導体実装基板に実装され、さらに金属シャーシ内にこの高周波半導体実装基板を他の回路基板等とともに収納する形態であった。

#### [00003]

### [0004]

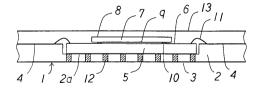

なお、図 8 において、12は実装用配線基板 5 の下面を配線基板 1 の下面の接地導体 3 に凹部 2 a の底面を介して電気的に接続するための接地用貫通導体、13はこの高周波半導体装置に用いられたメタルシールドである。

#### [0005]

しかしながら、高周波半導体素子 7 の動作周波数が高くなるにつれて接続用のボンディングワイヤ11による寄生特性の影響が顕著になるために、近年は実装用配線基板 5 の実装用線路導体 6 と配線基板 1 の線路導体 4 とについても導体バンプを用いて電気的かつ機械的に接続を行なうフリップチップ実装を採用し、このような寄生特性を抑制することが提唱されている。

## [0006]

通常、このようなフリップチップ実装は、高周波半導体素子およびこれが搭載される高周波半導体実装基板におけるそれぞれの入出力用の電極が形成された各主面を対向させ、高周波半導体素子上の電極とこの電極に対応する実装基板上の電極とを導体バンプにより電気的に接続する構造を有している。

### [0007]

### 【発明が解決しようとする課題】

しかしながら、高周波半導体素子はその表面における配線構造にマイクロストリップ線路等の線路導体を用いたプレーナ型伝送線路を採用しており、そのインピーダンス設計は半導体素子単体において最適化されているが、フリップチップ実装を行なった際には、半導体素子表面の配線部下方に比較的高い比誘電率を有する実装基板の誘電体が配置されることになるために、配線のインピーダンスが設計値と異なる値になり、所望の回路動作が保証されなくなってしまうという問題点があった。

### [0008]

また、半導体素子と実装基板とが重なり合う領域においては、線路導体の上下に半導体素子の誘電体と実装基板の誘電体とが配される構造となるために、インピーダンスを整合させるためには線路導体の線路幅を狭くする必要があるが、このような線路幅の変化は高周波信号の反射を引き起こす不連続点に相当するため、特に高周波帯域においては信号伝送特性を劣化させる要因となるという問題点があった。

#### [0009]

また、フリップチップ実装は元来高速ディジタル回路素子の実装において実装面積の縮小

20

10

30

40

20

30

40

50

化と不良素子の交換性を向上させる技術として発展してきたが、高周波半導体素子に対してベアチップによるフリップチップ実装を行なった際には、機械的強度等の観点から不良素子の実装後の交換が難しいため、マルチチップモジュールを組み立てた際の良品率を高めることが困難であるという問題点もあった。

#### [0010]

本発明はかかる従来技術の問題点に鑑みて案出されたものであり、その目的は、高周波半導体素子の実装後における配線のインピーダンスの変動を抑えるとともに、線路幅の変化による高周波信号の反射をなくすことができ、さらに実装後の不良素子の交換を容易に行なうことができる、高周波特性面でも製造工程面でも改善された実装構造を有する高周波半導体装置を提供することにある。

#### [0011]

#### 【課題を解決するための手段】

本発明の高周波半導体装置は、誘電体基板の上面に高周波半導体素子を収容する凹部を有し、この凹部の開口周辺に線路導体が形成されるとともに、下面および前記凹部底面に接地導体が形成された配線基板と、この配線基板上に前記凹部の開口を覆うように取着と、下面周辺部に形成された接続電極が前記線路導体に当接接続された実装用配線基板と、この実装用配線基板の下面に形成された実装電極に導体バンプを介して電気的に接続された高周波半導体素子とを具備する高周波半導体装置であって、前記実装用配線基板は前記凹部の開口寸法より大きく、かつ前記誘電体基板より比誘電率が大きい主誘電体層と、行い直にである。かつ前記主誘電体層の下面に形成された前記接続電極から前記主誘電体層の下面周辺部に形成された前記接続電極から前記主誘電体層がよび前記副誘電体層間にかけて形成された実装用線路導体と、この実装用線路導体を前記副誘電体層の下面に形成された前記実装電極に電気的に接続する貫通導体とから成ることを特徴とするものである。

#### [0012]

本発明の高周波半導体装置によれば、開口周辺に線路導体が形成され、底面に接地導体が形成された、高周波半導体素子を収容する凹部を有する配線基板に、実装用配線基板にフリップチップ実装された高周波半導体素子を、実装用配線基板の実装用線路導体を介む配線基板の線路導体に電気的に接続するとともに凹部に収容するようにして実装してのまま用配線基板が凹部の開口に取着される比誘電率が大きい主誘電体層とその高周波半導体素子側に積層された比誘電率が小さい副誘電体層とから成ることから高周波半導体素子の内部および/または表面に形成された配線部の上方には従来の実装基板に下の高周波半導体素子における配線本来のインピーダンス設計からのインピーダンスのずれにの高周波半導体素子における配線本来のインピーダンス設計からのインピーダンスのずれに比誘電率を有する誘電体が配置されることになるために配線のインピーダンスが設計値と比較電率を有する誘電体が配置されることになるために配線のインピーダンスが設計値と異なる値になり所望の回路動作が保証されない場合と比較して、高周波半導体素子の特性について本来の設計値を保証することができるものとなる。

### [0013]

また、実装用配線基板における内層配線の線路導体の線路幅は、主誘電体層および副誘電体層の層厚みならびに副誘電体層の表面から配線基板に形成された凹部底面の接地導体までの距離を用いることにより、インピーダンス設計における自由度が増すこととなる。その結果、線路導体の線路幅の変化量を極めて小さく抑えることが可能となり、高周波信号の反射を引き起こすような不連続点に相当する部分をなくすことができ、信号伝送特性を劣化させることがなくなるので、高周波信号に対する良好な伝送特性を有する高周波半導体装置となる。

#### [0014]

さらに、高周波半導体素子を機械的強度の高い実装用配線基板に実装した上でこの実装用配線基板を配線基板に実装することから、実装後に不良素子が発生した場合にもこの実装 用配線基板を交換すればよいため、従来のようなベアチップ実装により実装後の不良素子

20

30

40

50

の交換が困難な実装構造のものと比較して、マルチチップモジュールを構成した場合に全体の良品率を向上させることが容易に達成できるものとなる。

[0015]

【発明の実施の形態】

以下、図面に基づいて本発明の高周波半導体装置について説明する。

[0016]

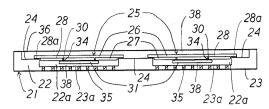

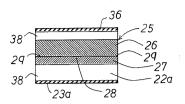

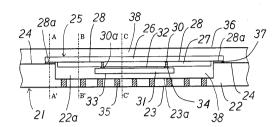

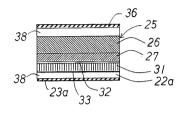

図1は本発明の高周波半導体装置の実施の形態の一例を示す断面図、図2はその要部拡大断面図である。また、図3は図2のA-A'線における要部断面図、図4は図2のB-B'線における要部断面図、図5は図2のC-C'線における要部断面図である。

[0017]

これらの図において、21は配線基板であり、誘電体基板22の上面に高周波半導体素子を収容する凹部22 a を有し、この凹部22 a の開口周辺に線路導体24が形成されるとともに、下面および凹部22 a 底面に接地導体23および23 a が形成されている。

[0018]

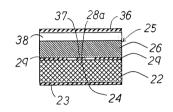

25は実装用配線基板であり、配線基板21の凹部22aの開口寸法より大きく、かつ誘電体基板22より比誘電率が大きい主誘電体層26と、その下面に積層された凹部22aの開口寸法より小さく、かつ主誘電体層26より比誘電率が小さい副誘電体層27と、主誘電体層26の下面周辺部に形成された接続電極28aから主誘電体層26および副誘電体層27間にかけて形成された実装用線路導体28と、この実装用線路導体28を副誘電体層27の下面に形成された実装電極30aに電気的に接続する貫通導体30とから成り、配線基板21上に凹部22aの開口を覆うように取着され、主誘電体層26の下面周辺部に形成された接続電極28aが線路導体24に当接接続されている。

[0019]

31は高周波半導体素子であり、実装用配線基板25の副誘電体層27の下面に形成された実装電極30aに導体バンプ34を介して端子電極(図示せず)が電気的に接続されている。32は高周波半導体素子31の上面に形成された配線部としての配線導体、33は高周波半導体素子31の下面に形成された素子接地導体である。

[0020]

なお、29は実装用配線基板25の主誘電体層26と副誘電体層27との間で実装用線路導体28と同一面に形成された実装用同一面接地導体であり、この実装用同一面接地導体29と実装用線路導体28とでコプレーナ線路を構成している。また、この実装用同一面接地導体29は配線基板21の上面において線路導体24と同一面に形成された同一面接地導体(図示せず)と電気的に接続されることによって、配線基板21から実装用配線基板25にかけてコプレーナ線路で接続された高周波回路が構成されることとなる。

[0021]

35は配線基板21の下面の接地導体23と凹部22a底面の接地導体23aとを電気的に接続するための接地用貫通導体である。36は必要に応じて配線基板21に搭載実装された実装用配線基板25を覆うように配線基板21に取着される蓋体であり、ここではメタルシールドである。37は線路導体24と接続電極28aとを電気的に接続するための例えば半田である。そして、38は凹部22a内あるいは配線基板21および実装用配線基板25と蓋体36との間に存在する空気層を示している。

[0022]

このような構成により、本発明の高周波半導体装置は、上面に端子電極を有する高周波半導体素子31と、この高周波半導体素子31の端子電極に対応してフリップチップ実装を行なうための実装電極30 a および外部電気回路としての配線基板21との入出力用の接続電極28 a を有する実装用配線基板25と、この接続電極28 a に対応して実装を行なうための線路導体24を有するとともにフリップチップ実装された高周波半導体素子31および実装用配線基板25の一部(副誘電体層27の部分)を収納するための凹部22 a を有する配線基板21とから成る実装構造を有し、実装用配線基板25は比誘電率の異なる主誘電体層26と副誘電体層27とを積層した多層構造を有しており、その基体となる主誘電体層26の露出面(上面)には

接地導体が形成されておらず、主誘電体層26の比誘電率が配線基板21を構成する誘電体基板22の比誘電率および副誘電体層27の比誘電率よりも大きく、主誘電体層26の寸法が配線基板21の誘電体基板22に設けられた凹部22aの開口寸法よりも大きく、かつ副誘電体層27の寸法が凹部22aの開口寸法よりも小さく形成されており、高周波半導体素子31とのフリップチップ実装用の実装電極30aはこの副誘電体層27の表面(下面)に形成されており、配線基板21との接続電極28aは主誘電体層26の下面周辺部において副誘電体層27が積層されていない領域に形成されており、接続電極28a間の配線は主誘電体層26と副誘電体層27との界面に形成された実装用線路導体28および副誘電体層27内に形成された貫通導体30から成り、実装用配線基板25副誘電体層27およびこの副誘電体層27の下面にフリップチップ実装された高周波半導体素子31を配線基板21に設けられた凹部22aに収容しつつ配線基板21と実装用配線基板25との対応する電極同士を接続する構成を有している。

[0023]

このような構成の本発明の高周波半導体装置において、実装用配線基板25を形成する主誘電体層26および副誘電体層27は、いずれも単一の誘電体材料から成る単層のものであってもよく、それぞれ複数の誘電体層を積層して所望の比誘電率やその他の特性となるようにした多層構成のものであってもよい。このような主誘電体層26および副誘電体層27としては、例えば主誘電体層26には酸化アルミニウム質焼結体や窒化アルミニウム質焼結体等のセラミックス材料を用い、副誘電体層27にはポリイミドやポリテトラフルオロエチレン(PTFE)・ベンゾシクロブテン(BCB)等の誘電体樹脂材料を用いればよい。

[0024]

そして、主誘電体層26を誘電体基板22より比誘電率が大きいものとし、一方、副誘電体層27を主誘電体層26よりも比誘電率が小さいものとする場合には、例えばこれらを形成する実用的な誘電体材料から比誘電率が2前後の小さいもの、4~6程度のもの、8以上の大きいものを選択し、これらの誘電体材料を比誘電率の大きさに応じて適宜組み合わせて使用するようにすればよい。その際、誘電体基板22の比誘電率と副誘電体層27の比誘電率とは、それぞれ主誘電体層26よりも小さいものであれば、同等の比誘電率のものを用いても、異なる比誘電率のものを用いてもよく、高周波半導体装置の仕様に応じてそれぞれの材料を適宜選択すればよい。

[0025]

また、主誘電体層26の寸法を凹部22 a の開口寸法よりも大きくする場合、概ね開口寸法よりもそれぞれ高周波信号の波長の4分の1程度かそれ以下程度で大きいものとすればよく、副誘電体層27の寸法を凹部22 a の開口寸法よりも小さくする場合、実装の工作精度に影響がない程度で、なるべく開口寸法に近い大きさとすればよい。

[0026]

なお、配線基板21を形成する誘電体基板22についても、主誘電体層26よりも比誘電率が小さい誘電体材料であれば実装用配線基板25と同様の材料を用いればよく、同様に単層としても多層構成としてもよい。

[0027]

また、配線基板21の誘電体基板22の凹部22 a の底面に形成された接地導体23 a は、実装用配線基板25に形成された線路導体28および高周波半導体素子31の上面に形成された配線導体32に対して高周波信号に対するグランドとして機能するものである。

[0028]

この接地導体23 a を始めとして接地導体23・線路導体24・実装用線路導体28・接続電極28 a・実装用同一面接地導体29・貫通導体30・実装電極30 a・配線導体32・素子接地導体33・接地用貫通導体35には、高周波用の導体として使用される種々の導体材料を使用すればよく、その形状や寸法等もその仕様に応じて適宜選択すればよい。

[0029]

また、導体バンプ34・半田37にも同様に高周波用の導体バンプおよび実装用の半田として使用される種々の材料を使用すればよく、メタルシールド等の蓋体36にも同様に蓋体として使用される種々の材料・形状・寸法等を選択して適用すればよい。

20

30

40

30

40

50

#### [0030]

次に、本発明の高周波半導体装置について具体例を示す。

#### [0031]

まず、厚み200 μmのアルミナセラミックス(比誘電率9.6 )から成る主誘電体層26上に実装用線路導体28としての銅配線および厚み100 μmのポリイミド(比誘電率3.4 )から成る副誘電体層27を薄膜形成し、ポリイミド層表面において高周波半導体素子31の端子電極に対応する個所に実装電極30aを設け、内層配線となる実装用線路導体28と貫通導体30により接続させて実装用配線基板25を作製した。

#### [0032]

また、厚み150 μm のガラスセラミックス(比誘電率4.8)を3層積層し、その内の2層分をくり抜くことにより、凹部22a すなわちキャビティを有する構造の誘電体基板22から成る配線基板21を作製した。なお、この配線基板21においては3層目の表面に配線基板21の配線としての線路導体24および入出力電極が、また1層目表面すなわち凹部22a底部に接地導体23aが、それぞれ銅ペーストを印刷して誘電体基板22と同時焼成することにより厚膜として形成されており、接地導体23aは1層目を貫通する接地用貫通導体35により配線基板21の下面の接地導体23と電気的に接続されて接地をとる構造となっている。

#### [0033]

また、配線基板21において、3層目の表面から上方300 µmの位置には、配線基板21全体を被覆するメタルシールドとしての鉄 - ニッケル - コバルト合金から成る蓋体36を設けた

#### [0034]

そして、フリップチップ実装の特性評価用として、厚み100 μmのガリウムひ素基板に線路幅80μmのマイクロストリップ線路導体を形成し、入出力電極部は信号線路の両端から各々70μm間隔のところに80μm×80μmの接地用電極を有するコプレーナ線路構造となっている高周波半導体素子31としての評価用基板を作製し、高さ20μmの金から成る導体バンプ34を介して実装用配線基板25に対してフリップチップ実装を行なった。

### [0035]

また、実装用配線基板25の副誘電体層27であるポリイミド層および高周波半導体素子31としての評価用基板を凹部22a内に収容しつつ、主誘電体層26であるアルミナセラミックス層において露出している接続電極28aと配線基板21の線路導体24とを半田37により接続することにより、本発明の高周波半導体装置における実装構造を実現した。

### [0036]

また一方、比較例として、厚み200 μmのアルミナセラミックス基板上に線路幅200 μmのマイクロストリップ線路および高周波半導体素子31としての評価用基板の端子電極に対応する実装電極を有する実装用配線基板を作製し、同一の条件で評価用基板をフリップチップ接続したものを作製した。

## [0037]

上記のような本発明の高周波半導体装置における実装構造によれば、図3に示したA-A / 線断面においては、配線基板21上の線路導体の接続部とそれに対応させて実装用配線基板25の主誘電体層26の下面に形成された接続電極28 a が半田37により接合されており、実装用線路導体28の線路幅は80 μ m、実装用線路導体28と接地導体23 a との間隔は130 μ m となる。また図4に示したB-B / 線断面は、実装用配線基板25の主誘電体層26と副誘電体層27との界面に形成された実装線路構造であり、実装用線路導体28の線路幅は80 μ m、実装用線路導体28と接地導体23 a との間隔は80 μ m となる。

#### [0038]

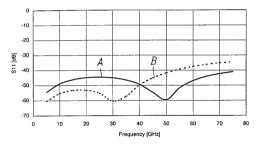

このような本発明の高周波半導体装置における A - A '線断面構造および B - B '線断面構造の反射特性を図 6 に線図で示す。図 6 において、横軸は周波数(単位:G H z )を、縦軸は反射係数 S 11 (単位:d B) を表しており、実線で示した特性曲線 A は A - A '線断面における反射係数 S 11の周波数特性を、破線で示した特性曲線 B は B - B '線断面における反射係数 S 11の周波数特性を示している。これによれば、いずれの伝送線路構造も

30

40

50

広帯域にわたって低い反射係数を実現できていることが示されている。すなわち、いずれの伝送線路構造においても、インピーダンス整合を取りつつ高周波半導体素子31の配線導体32の線路幅と同程度の線路幅を実現することが可能となっている。これにより、実装用線路導体28における線路幅の変化を抑えることが可能となるため、実装構造全体としての伝送においても良好な伝送特性を実現することが可能となる。

### [0039]

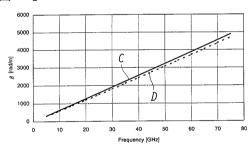

また、図1におけるC - C , 線断面構造および高周波半導体素子31の設計値の伝搬特性を図7に線図で示す。ここでは、図4に示すB - B , 線断面と同様の主誘電体層26および副誘電体層27からなる実装用配線基板25の下方20μmに高周波半導体素子31としての評価用基板が配置されている。図7において、横軸は周波数(単位:G H z )を、縦軸は伝搬定数の虚部、すなわち位相定数 (単位:rad/m)を表している。実線で示した特性曲線Cは、評価用基板の直上に評価用基板と副誘電体層27との間の空気層・副誘電体層27・主誘電体層26・空気層38が分布しているが、主誘電体層26の下面に積層した副誘電体層27に比誘電率の比較的低い材料を選択しているために、図7に示されるように、破線で示した特性曲線Dで示される高周波半導体素子の特性では位相特性にほとんど変化は見られなかった。

#### [0040]

また、図1は本発明の高周波半導体装置の全体図を示す断面図であるが、図2からも明らかなように、高周波半導体素子31は各々実装用配線基板25にフリップチップ実装されているために、ある高周波半導体素子31が不良であることが実装後に判明した場合においても、配線基板1および実装用配線基板13の主誘電体層26には、高周波半導体素子31に比べて機械的強度が強い材料を選択することができ、その結果、製造における樹脂の選択の自由度を高めるとともに、実装用配線基板13毎に交換することが可能となり、半導体装置全体としての良品率をも向上させることが可能となる。

#### [0041]

なお、以上はあくまで本発明の実施の形態の例示であって、本発明はこれらに限定される ものではなく、本発明の要旨を逸脱しない範囲で種々の変更や改良を加えることは何ら差 し支えない。

### [0042]

## 【発明の効果】

以上のように、本発明の高周波半導体装置によれば、開口周辺に線路導体が形成され、底面に接地導体が形成された、高周波半導体素子を収容する凹部を有する配線基板に、実装用配線基板にフリップチップ実装された高周波半導体素子を、実装用配線基板の実装用線路導体を介して配線基板の線路導体に電気的に接続するとともに凹部に収容するように実装しており、この実装用配線基板が凹部の開口に取着される比誘電率が大きい主誘電体層とその高周波半導体素子側に積層された比誘電率が小さい副誘電体層とから成ることが高周波半導体素子の内部および/または表面に形成された配線部の上方には従来実装を行なった際の高周波半導体素子における配線本来のインピーダンス設計からのインピーダンスのずれ量を低く抑えることができ、従来のように、高周波半導体素子の配線のインピーダンスのずれ量を低く抑えることができ、従来のように、高周波半導体素子の配線のインピーダンスのずれ量を低く抑えることができ、だまなるために配線のインピーダンスが設計値と異なる値になり所望の回路動作が保証されない場合と比較して、高周波半導体素子の特性について本来の設計値を保証することができるものとなる。

## [0043]

また、実装用配線基板における内層配線の線路導体の線路幅は、主誘電体層および副誘電体層の層厚みならびに副誘電体層の表面から配線基板に形成された凹部底面の接地導体までの距離を用いることにより、インピーダンス設計における自由度が増すこととなる。その結果、線路導体の線路幅の変化量を極めて小さく抑えることが可能となり、高周波信号の反射を引き起こすような不連続点に相当する部分をなくすことができ、信号伝送特性を劣化させることがなくなるので、高周波信号に対する良好な伝送特性を有する高周波半導

体装置となる。

#### [0044]

さらに、高周波半導体素子を機械的強度の高い実装用配線基板に実装した上でこの実装用配線基板を配線基板に実装することから、実装後に不良素子が発生した場合にもこの実装用配線基板を交換すればよいため、従来のようなベアチップ実装により実装後の不良素子の交換が困難な実装構造のものと比較して、マルチチップモジュールを構成した場合に全体の良品率を向上させることが容易に達成できるものとなる。

#### [0045]

以上により、本発明によれば、高周波半導体素子の実装後における配線のインピーダンスの変動を抑えるとともに、線路幅の変化による高周波信号の反射をなくすことができ、さらに実装後の不良素子の交換を容易に行なうことができる、高周波特性面でも製造工程面でも改善された実装構造を有する高周波半導体装置を提供することができた。

【図面の簡単な説明】

- 【図1】本発明の高周波半導体装置の実施の形態の一例を示す断面図である。

- 【図2】図1の要部拡大断面図である。

- 【図3】図2のA-A′線における要部断面図である。

- 【図4】図2のB-B'線における要部断面図である。

- 【図5】図2のC-C′線における要部断面図である。

- 【図6】本発明の高周波半導体装置におけるA A '線断面構造およびB B '線断面構造の反射特性を示す線図である。

- 【図7】本発明の高周波半導体装置におけるC-C'線断面構造および高周波半導体素子の位相定数の周波数特性を示す線図である。

- 【図8】従来の高周波半導体装置の例を示す要部拡大断面図である。

#### 【符号の説明】

- 21・・・・配線基板

- 22・・・・誘電体基板

- 22 a · · · · 凹部

- 23、23 a · · 接地導体

- 24・・・・線路導体

- 25・・・・・実装用配線基板

- 26・・・・主誘電体層

- 27・・・・副導体層

- 28・・・・実装用線路導体

- 28 a・・・・接続電極

- 30・・・・貫通導体

- 34・・・・導体バンプ

20

10

【図1】

# 【図4】

【図2】

【図5】

【図3】

【図6】

【図7】

【図8】

# フロントページの続き

# (56)参考文献 特開平05-166957(JP,A)

特開昭64-013755(JP,A)

特開平11-074416 (JP,A)

特開2000-261214(JP,A)

特開平04-361559(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 23/12

H01L 25/04

H01L 25/18