# **FEATS**

# Framework for Explorative, Analog Topology Synthesis

Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich Informatik und Mathematik der Goethe-Universität in Frankfurt am Main

von

Markus Meissner aus Heydebreck

Frankfurt (2015) (D 30)

#### ABSTRACT

The presented work inside this thesis aims to raise the degree of automation in analog circuit design. Therefore, a framework was developed to provide the necessary mechanisms in order to carry out a fully automated analog circuit synthesis, i.e., the construction of an analog circuit fulfilling all previously defined (electrical) specifications.

Nowadays, analog circuit design in general is a very time consuming process compared to a digital design flow. Due to its discrete nature, the digital design process is highly automated and thus very efficient compared to analog circuit design. In modern Very-Large-Scale integration (VLSI) circuits the analog parts are mostly just a small portion of the overall chip area. Although this small portion is known to consume a major part of the needed workforce. Paired with product cycles which constantly get shorter, the time needed to develop the analog parts of an integrated circuit (IC) becomes a determinant factor. Apart from this, the ongoing progress in semiconductor processing technologies promises more speed with less power consumption on smaller areas, forcing the IC developers to keep track with the technology nodes in order to maintain competitiveness. Analog circuitry exhibits the inherent property of being hard to reuse, as porting from one technology node to another imposes critical changes for operating conditions (e.g., supply voltage) - mostly leading to a full redesign for most of the analog modules. This productivity gap between digital and analog design resembles the primary motivation for this thesis.

Due to the availability of commercial sizing tools, this work deliberately focuses on the construction of circuit topologies in distinction to parameter synthesis, which can be obtained with a dedicated sizing tool. The focus on circuit construction allows the development of a framework which allows a full design space exploration. This thesis describes the needed concepts and methods to realize a deterministic, explorative analog synthesis framework. Despite this, a reference implementation is presented, which demonstrates the applicability in current analog design flows.

## ZUSAMMENFASSUNG (GERMAN ABSTRACT)

Die in dieser Dissertation vorgestellten Arbeiten verfolgen das Ziel, den Grad der Automatisierung des Entwurfs von integrierten analogen Schaltungen zu erhöhen. Hierfür wurde ein Framework entwickelt, welches die benötigten Mechanismen bereitstellt, um eine voll automatisierte analoge Schaltungssynthese durchführen zu können, d.h. die Konstruktion einer analogen Schaltung, welche alle zuvor definierten (elektrischen) Spezifikationen erfüllt.

Der analoge Entwurfsprozess ist heutzutage ein sehr zeitintensives Unterfangen, insbesondere im Vergleich mit dem digitalen Entwurfsprozess. Durch seine diskrete und damit etwas abstraktere Natur ist der digitale Entwurfsprozess sehr effizient, u.a. da dem Designer Werkzeuge zur Verfügung stehen, die ein hohes Maß an Automatisierung ermöglichen. In modernen integrierten Schaltungen mit einem hohen Integrationsgrad machen die analogen Schaltungsteile zumeist nur einen kleinen Anteil der gesamten Fläche aus. Trotzdem sind der Aufwand und somit die Kosten des Entwurfs unverhältnismäßig groß verglichen mit den digitalen Teilen. Einhergehend mit immer kürzer werdenden Entwurfszeiten wird der analoge Teil auf einem Mikrochip zunehmend der beherrschende Kosten- und Zeitfaktor. Darüber hinaus verspricht der Fortschritt der Prozesstechnologien höhere Geschwindigkeiten mit geringerem Energieverbrauch bei kleinerer Fläche, was die Hersteller dazu zwingt, Schritt zu halten, um weiterhin konkurrenzfähig zu bleiben. Analoge Schaltungen haben die inhärente Eigenschaft schwer wiederverwertbar zu sein, da das Portieren von einem Technologieknoten zum Nächsten nicht selten einher geht mit veränderten Betriebsbedingungen, wie bespielsweise verringerten Versorgungsspannungen. Dies führt zumeist zu einem vollständigen Neuentwurf der meisten analogen Schaltungsteile. Diese daraus entstehende Produktivitätslücke bei der Synthese zwischen analogen und digitalen Schaltungen ist die Hauptmotivation für diese Arbeit. In Letzterer werden neuartige, deterministische Verfahren zur vollautomatischen Synthese von analogen Schaltungen vorgestellt und demonstriert. Dabei konzentriert sich das hier vorgestellte Framework mit dem Namen FEATS überwiegend auf die Topologiesynthese.

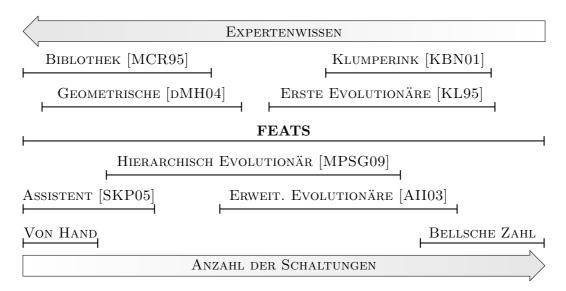

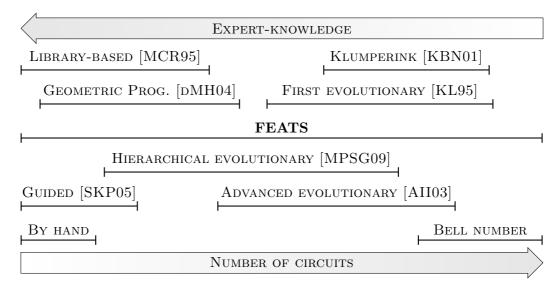

Die in Abbildung 2 dargestellte Relation zwischen eingebrachtem Expertenwissen und der Anzahl der Schaltungen ist eine weitere Kernmotivation für den Entwurf des hier vorgestellten Frameworks. Hierbei werden verschiedene vorgestellte Konzepte in Bezug zueinander gesetzt. Wichtig ist insbesondere der Handentwurf von Schaltungen, der sich am linken Rand der Abbildung befindet; dabei kommt ausschließlich Expertenwissen in Form eines Analogdesigners zum Einsatz. Dem gegenüber steht der absolut naive Ansatz (Bellsche Zahl), welcher alle möglichen

Abbildung 1: Illustration des Zusammenhangs zwischen eingebrachtem Expertenwissen und der Anzahl der generierten Schaltungen. FEATS bezeichnet das hier vorgestellte Syntheseframework.

Schaltungen generiert und die *richtige* in dieser Menge zu finden versucht. Dieser rein theoretische Ansatz wird ausführlich beleuchtet und definiert zusätzlich den sogenannten *Entwurfsraum für Schaltungen*. Die Abbildung soll darüber hinaus das Ziel veranschaulichen, welches in dieser Dissertation verfolgt wird. Eine Diskussion der Konzepte, welche sich darüber hinaus in der Abbildung befinden, ist auch der vorliegenden Arbeit zu entnehmen.

Im Mittelteil werden die wesentlichen Konzepte und Algorithmen präsentiert, die Verwendung finden. Dabei werden zunächst die benötigten Eingabedaten beleuchtet:

Komponenten entsprechen den atomaren Bauteilen einer elektrischen Schaltung. Diese werden in einer abstrakten Form beschrieben (z.B.: hochohmiger Widerstand, präzise Kapazität oder Schalttransistor) und für die Synthese mit einem entsprechend Bauteil aus der Zieltechnologie verknüpft.

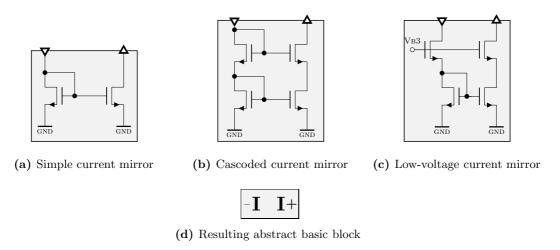

Basisblöcke bestehen aus einer oder mehreren Komponenten und können auch als funktionale Blöcke gesehen werden. Diese können ebenfalls vom Benutzer frei angepasst, hinzugefügt und ersetzt werden.

Schaltungstemplates repräsentieren die Hierarchien in dem vorgestellten Framework. Dieses sehr ausdrucksstarke Element des Framework erlaubt die Beschreibung von beliebig tiefen Hierarchien, hierbei liegt der Fokus auf der Wiederverwendbarkeit, d.h. ein zuvor entwickeltes Schaltungstemplate kann ohne weitere Anpassungen in ein anderes Schaltungstemplate eingebettet werden, um so beliebig komplexe analoge Module zu beschreiben und zu synthetisieren.

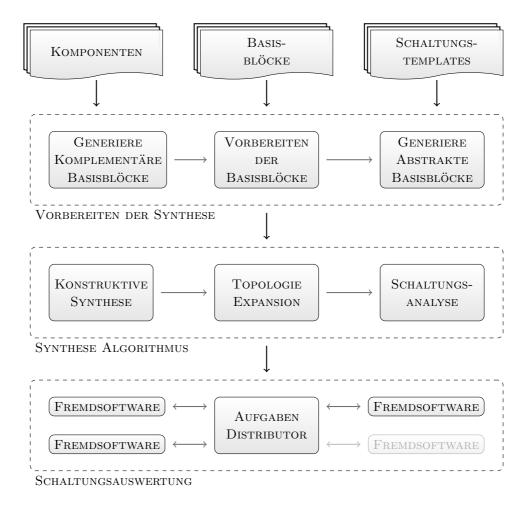

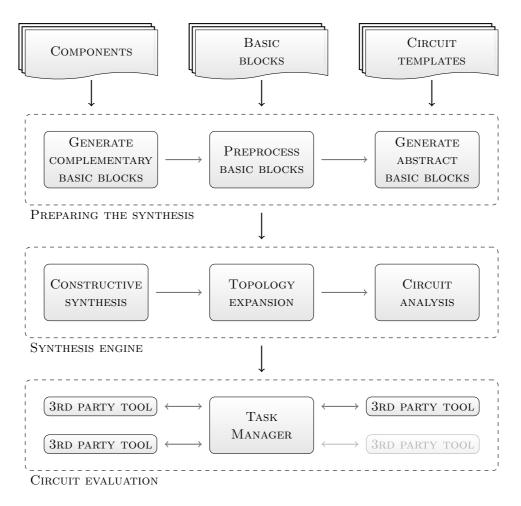

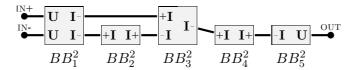

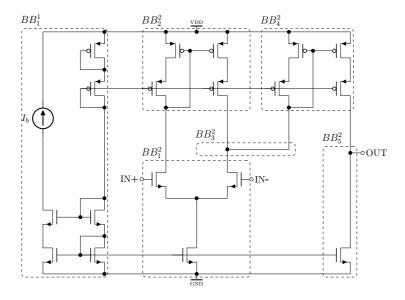

Der Syntheseablauf ist im Wesentlichen in drei Schritte unterteilt, welche man in Abbildung 2 sehen kann. Zunächst werden die Eingabedaten für die Synthese vorbereitet. Hierbei

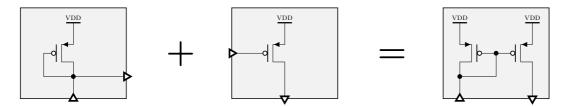

werden primär die Basisblöcke betrachtet, die zunächst als Grundlage zum Generieren weiterer Basisblöcke benutzt werden. Daraufhin werden abschließende Konsistenzprüfungen an den Basisblöcken vorgenommen und zusätzliche (automatisch zu generierende) Informationen in eben diesen untergebracht. Schließlich folgt noch ein wichtiger letzter Schritt: Die Klassifizierung der vorliegenden Basisblöcke in sogenannte abstrakte Basisblöcke. Es werden mehrere Basisblöcke zu einem abstrakten Basisblock zusammengelegt, abhängig von dessen Eingangs- bzw. Ausgangsspezifikationen. Dieser Schritt zielt darauf ab, die Berechnugskomplexität des Synthesealgorithmuses zu verringern und entspricht im weitesten Sinne einem Verhaltensmodell getriebenen Analogentwurf.

Abbildung 2: Vollständiger Syntheseablauf mit allen wesentlichen Bestandteilen

Der Synthesealgorithmus sowie dessen Schritte auf dem Weg zu einer fertigen Schaltung werden ausführlich besprochen, um dem Leser einen genauen Einblick in die internen Algorithmen und Konzepte zu ermöglichen. Hierbei werden (Synthese-)Regeln eingesetzt, die verschiedene Entwurfsschritte (möglichst abstrakt) realisieren und darüber hinaus eine konsistente Schnittstelle für die Manipulation und Analyse von Schaltungen darstellen.

Konstruktive Synthese benutzt konstruktive Regeln sowie destruktive Regeln um Topologien zu generieren, welche ausschließlich aus abstrakten Basisblöcken bestehen. Der gesamte Entwurfsraum wird dabei exploriert und wird in seiner Ausdehnung nur von den destruktiven Regeln begrenzt.

**Topologie Expansion** ist der nächste Schritt, in dem die zuvor generierten Topologien zu realen Schaltungen expandiert werden.

Schaltungsanalyse realisiert einen sehr wichtigen Vorauswahlschritt. Hierbei ist das Ziel die Schaltungen möglichst frühzeitig aus der Synthese auszuschließen, falls sich Eigenschaften finden lassen, die diese mit einer hohen Wahrscheinlichkeit als untauglich klassifizieren.

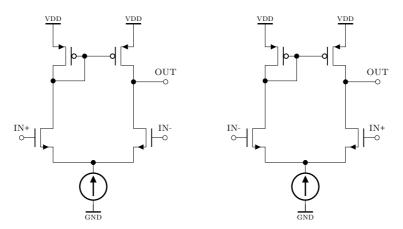

Der Letzte dieser drei Schritte ist ebenso im Detail beschrieben. Dabei handelt es sich einerseits um einen Isomorphiealgorithmus, welcher zuverlässig Schaltungen aussortiert, die mehrfach vorhanden sind. Andererseits wird eine schnelle Analyse präsentiert, welche Schaltungen mit invertierter Verstärkung identifiziert und von der folgenden Dimensionierung ausschließt. Darüber hinaus werden in diesem Schritt die propagierten elektrischen Nebenbedingungen in ein System von Ungleichungen zusammengefasst. Dieses lässt sich im Folgenden auf nicht-Lösbarkeit überprüfen und liefert in diesem Fall eine zuverlässige Voraussage, ob dies bei einer tatsächlichen Realisierung der Schaltung ebenso eintreten wird.

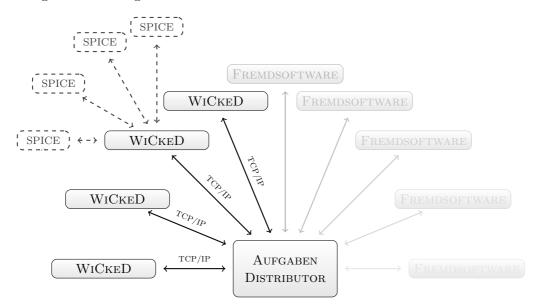

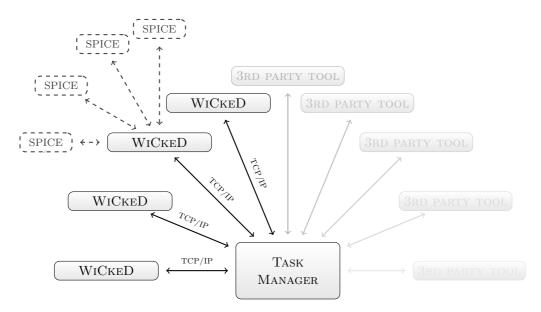

Abbildung 3: Illustration der asynchronen Aufgabendistribution.

Die automatisierte Dimensionierung der Schaltungen ist unabdingbar um Analogsynthese zu betreiben. In FEATS wird dies durch ein kommerziell verfügbares Produkt namens WiCkeD realisiert. Letzteres ermöglicht eine automatisierte, Skript-getriebene Dimensionierung einer Schaltung. Die hierfür benötigten Daten werden vollautomatisch vom Framework erzeugt und bereitgestellt. Ein wichtiges Merkmal des realisierten Konzeptes ist die asynchrone Verteilung von (Dimensionerungs-) Aufgaben an eine beliebige Anzahl von Fremdsoftwareinstanzen, d.h. der

Aufgaben Distributor dient nicht nur der Evaluierung respektive, Dimensionierung der Schaltungen, sondern ist wie in Abbildung 3 zu sehen auch noch für das transparente Skalieren der verfügbaren Softwarekapazitäten verantwortlich.

Abschließend werden umfangreiche Analysen und Ergebnisse des vorgestellten Frameworks präsentiert. Hierbei wird die Möglichkeit ergriffen, anhand von realen Schaltungssynthese Beispielen den Ablauf des Syntheseprozesses im Detail zu beleuchten. Die hier gewählten Beispiele sollen eine möglichst breite Abdeckung der möglichen Einsatzgebiete von FEATS repräsentieren:

Operationsverstärker dienen als Referenzschaltung, entsprechend wird demonstriert wie das Framework mit Leichtigkeit eine Vielzahl von Lehrbuchschaltungen sowie ungewöhnliche Schaltungen generiert und erfolgreich bzgl. gewünschter Spezifikationen dimensioniert.

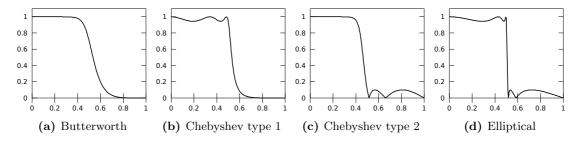

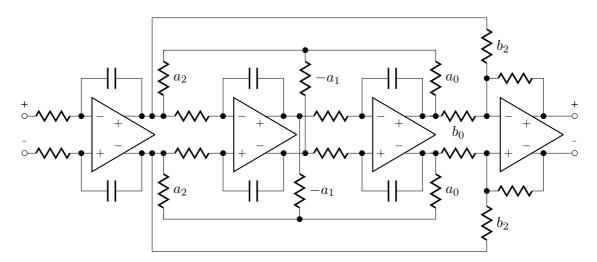

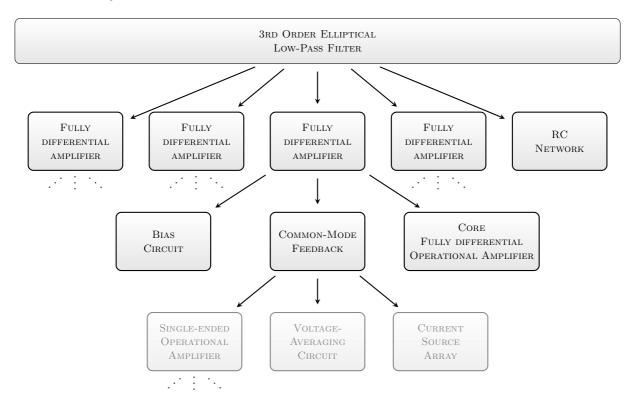

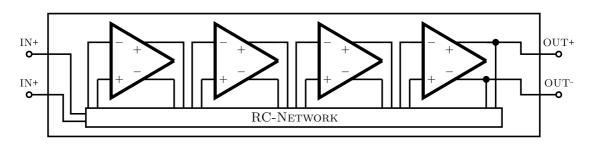

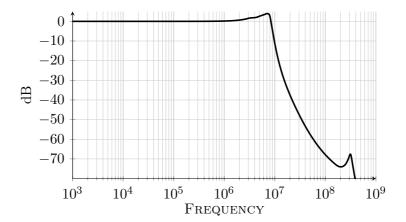

Elliptischer Tiefpass Filter 3. Ordnung präsentiert die Skalierbarkeit des vorgestellten Frameworks. Dabei wird die Synthese in mehreren Hierarchien ausgeführt, um in der höchsten Hierarchie eine fertige Schaltung zusammensetzen zu können. Das hierbei vollständig automatisiert synthetisierte Analogmodul enthält mehr als 200 Transistoren und präsentiert eindrucksvoll die Leistungsfähigkeit der hier vorliegenden Methode.

Zusammengefasst läßt sich feststellen, dass die hier vorgestellten Konzepte die Möglichkeit bieten, den Entwurf von analogen Schaltungen um signifikante Größenordnungen zu beschleunigen. Darüber hinaus wird demonstriert, dass die analoge Schaltungssynthese während des Entwurfsprozesses zahlreiche Vorteile bieten kann, die dazu führen, dass schneller bessere Schaltungen erzeugt werden, die Produktivität des Designers wird massiv erhöht und schließlich kann dieser seine Fähigkeiten gezielter einsetzen und auf die echten Probleme des Analogentwurfs richten, anstatt Tage oder sogar Wochen auf den manuellen Schaltungsentwurfprozess zu verschwenden.

#### LIST OF ABBREVIATIONS

AAHS analog artificial hormone system

ABB abstract basic block

${f AC}$  alternating current, also analysis type in SPICE simulators

ADC analog to digital converter

**API** application programming interface

BB basic block

**BLR** block length rule

**CAP** capacitor

CAS computer algebra system

CMFB common-mode feedback amplifier

**CMOS** a technology or configuration utilizing nMOS and pMOS devices

CMRR common-mode rejection ratio

CNT carbon nanotubes

**CPU** central processing unit

CTR circuit template rule

**DAC** digital to analog converter

**DC** directed current, also analysis type in SPICE simulators

**DUT** device under test

EDA electronic design automation

**EER** elementary electric rule

**ELIPLP** elliptical low pass filter

**EXPROPS** extract properties rule

**FD** fully differential

FDA fully differential operational amplifier

**FEATS** framework for explorative analog topology synhtesis

GI graph isomorphism complexity class

I/O input and output

IBR initial block rule

IC integrated circuit

${\bf IEEE}$  Institute of Electrical and Electronics

Engineers

IIP3 third-order intercept point

ISO (circuit) isomorphism rule

ITRS International Technology Roadmap for

Semiconductors

IVR input voltage range

LIB library rule

LU decomposition algorithm to solve a

square system of linear equations

${f MOS}$  metal-oxide-semiconductor field-effect

transistor

**NB2R** no block twice rule

nMOS a MOS device with a channel contain-

ing mostly electrons

NP nondeterministic polynomial time com-

plexity class

**OFET** organic field-effect transistor

**OMR** output match rule

**OP** single-ended operational amplifier

OPCORE operational amplifier core

OTA operational transconductance amplifier

OTFT organic thin film transistor

OVR output voltage range

P polynomial time complexity class

P1db 1db gain compression point

pMOS a MOS device with a channel containing mostly holes

PSRR power supply noise rejection ratio

${f RC ext{-}net}$  resistor and capacitor network, mostly in the context of (active) filters

**RES** resistor

**SKLP** Sallen-Key low pass filter **SNDR** signal-to-noise and distortion ratio

SoC system on chip

**SPICE** simulation program with integrated circuit emphasis

SYM EER symmetric elementary electric rule

SYM FEAS symbolic feasibility rule

SYM GAIN symbolic gain rule

SYM PRE pre symbolic rule

$\begin{array}{ccc} \mathbf{TCP/IP} & \mathrm{transmission} & \mathrm{control} & \mathrm{proto-} \\ & \mathrm{col/internet} & \mathrm{protocol} \end{array}$

TIR topology isomorphism rule

${f TRAN}$  transient analysis in SPICE simulators

${f VLSI}$  very-large-scale integration

VVOER voltage-to-voltage only at end rule

w.l.o.g. without loss of generality

## LIST OF SYMBOLS

- abstract basic block (abb) a black box containing one or more BBs sharing the identical I/O characteristic

- **basic block** (bb) an electrical basic building block representation with an actual transistor-level implementation

- **big O**  $(\mathcal{O})$  landau symbol to describe asymptotic behavior of algorithms

- **circuit** (c) a circuit representing a physical realization

- **circuits** (C) an unordered set of circuits

- **design space** (DS) design space seen as crossproduct of PS and STS

- **devices** (M) an unordered set of devices

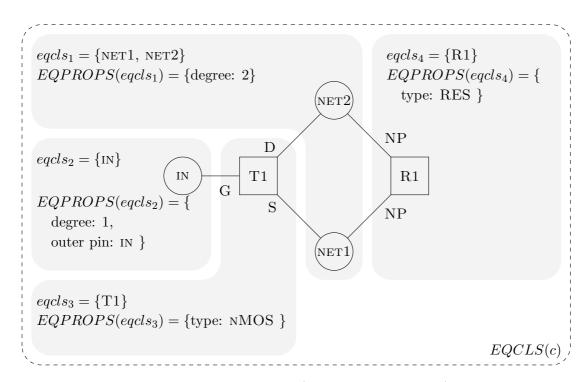

- **equivalence class** (*eqcls*) an unordered set of objects sharing the combination set of invariant properties

- equivalence classes (EQCLS(c)) set of equivalence classes associated with the circuit c

- **graph** (G) a representation of object vertices connected through edges

- **ground**  $(V_{GND})$  name of the reference net or simply ground

- **hash** (hash(x)) hash associated with object x

- integer  $(\mathbb{N})$  integer numbers

- invariant properties (EQPROPS(x)) set of invariant properties associated with x

- invariant property (p) a property associated with a specific  $IV^i$

- invariants ( $\mathbb{IV}$ ) an unordered set of invariants

- **label** (L(x)) label associated with object x

- **nets** (N) an unordered set of nets

- parameter space (PS) n-dimensional space spanned by the number of parameters n

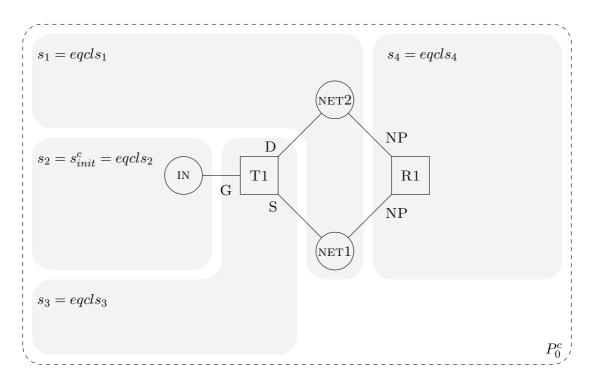

- **partition**  $(P^c)$  a partition of circuit c into subsets s

- **performance space** (PERF) n-dimensional space spanned by the number of performances n

- **power set**  $(\mathcal{P}(x))$  power set of a set x

- structure space (STS) a set of circuit structures

- subset (s) subset, which may contain vertices supply  $(V_{DD})$  name of the net the supply voltage is made available

- threshold voltage  $(V_{TH_{p/n}})$  CMOS threshold voltage voltage for either p or n type devices

- **topologies** (T) an unordered set of topologies **topology** (t) a topology (containing ABBs exclusively)

- **vertex** (u) another vertex inside a graph

- $\mathbf{vertex}(v)$  a vertex inside a graph

- **vertices** (V) an unordered set of vertices

## CONTENTS

| A        | bstra                                    | act                                                  | 1          |  |  |  |

|----------|------------------------------------------|------------------------------------------------------|------------|--|--|--|

| Zι       | ısam                                     | menfassung (German Abstract)                         | iii        |  |  |  |

| Li       | st of                                    | Abbreviations                                        | ix         |  |  |  |

| Li       | st of                                    | Symbols                                              | xi         |  |  |  |

| Ta       | able                                     | of Contents                                          | xiii       |  |  |  |

| 1        | 1.1                                      | roduction (Traditional) Analog Circuit Design Flow   | <b>1</b> 2 |  |  |  |

|          | 1.2<br>1.3                               | Contributions and Publications                       | 4<br>5     |  |  |  |

| <b>2</b> | Analog Circuit Representation as a Graph |                                                      |            |  |  |  |

| 3        | Analog Circuit Synthesis                 |                                                      |            |  |  |  |

|          | 3.1                                      | State-of-the-Art in Analog Synthesis                 | 10         |  |  |  |

| 4        | Introspection of the Analog Design Space |                                                      |            |  |  |  |

|          | 4.1                                      | Enumerating the Design Space Using the Bell Number   | 15         |  |  |  |

| 5        | A F                                      | Framework for Explorative Analog Topology Synthesis  | 21         |  |  |  |

|          | 5.1                                      | Methodological Considerations and Design Targets     | 22         |  |  |  |

|          | 5.2                                      | Inputs for a Circuit Synthesis                       | 23         |  |  |  |

|          |                                          | 5.2.1 Components                                     | 23         |  |  |  |

|          |                                          | 5.2.2 Basic Blocks                                   | 25         |  |  |  |

|          |                                          | 5.2.3 Circuit Templates                              | 26         |  |  |  |

|          | 5.3                                      | Preparing the Synthesis Process                      | 27         |  |  |  |

|          |                                          | 5.3.1 Complementary-Symmetric Basic Blocks           | 27         |  |  |  |

|          |                                          | 5.3.2 Deduction of Additional Basic Block Properties | 28         |  |  |  |

|          |                                          | 5.3.3 Abstract Basic Blocks                          | 29         |  |  |  |

## CONTENTS

|   | 5.4            | Circuit  | Synthesis Engine                                             |

|---|----------------|----------|--------------------------------------------------------------|

|   |                | 5.4.1    | Constructive Synthesis                                       |

|   |                | 5.4.2    | Topology Expansion                                           |

|   |                | 5.4.3    | Circuit Analysis                                             |

|   | 5.5            | Rules –  | Circuit Manipulation API                                     |

|   |                | 5.5.1    | Constructive Rules                                           |

|   |                | 5.5.2    | Destructive Rules                                            |

|   |                | 5.5.3    | Topology Expansion Rules                                     |

|   |                | 5.5.4    | Analyzing Rules                                              |

| 6 | Fast           | t Analy: | zing Techniques for Huge Circuit Amounts 37                  |

|   | 6.1            | Circuit  | Isomorphism                                                  |

|   |                | 6.1.1    | Graph Isomorphism                                            |

|   |                | 6.1.2    | From Graph to Circuit Isomorphism                            |

|   |                | 6.1.3    | Filtering Phase                                              |

|   |                | 6.1.4    | Core Circuit Isomorphism Algorithm(s)                        |

|   |                |          | 6.1.4.1 Backtracking-based Isomorphism Algorithm             |

|   |                |          | 6.1.4.2 Labeling-based Isomorphism Algorithm 47              |

|   | 6.2            | Fast Se  | mi-Symbolic Preselection                                     |

|   |                | 6.2.1    | Electrical Constraints                                       |

|   |                |          | 6.2.1.1 Feasibility Analysis                                 |

|   |                |          | 6.2.1.2 Output Voltage Range                                 |

|   |                | 6.2.2    | System Analysis                                              |

|   |                |          | 6.2.2.1 Gain Approximation                                   |

| 7 | Una            | attende  | d Circuit Sizing 55                                          |

|   | 7.1            | Task A   | llocation                                                    |

|   | 7.2            | Sizing   |                                                              |

| 8 | $\mathbf{Pre}$ | sentatio | on of Selected Circuit Classes 59                            |

|   | 8.1            | Utility  | Circuit Templates                                            |

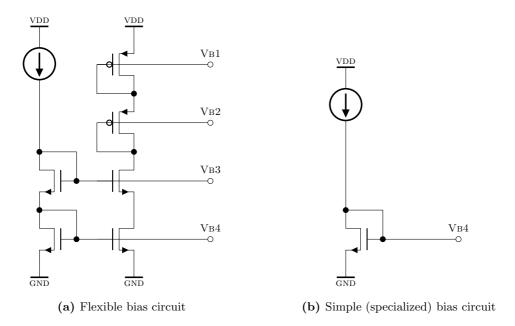

|   |                | 8.1.1    | Bias Circuit                                                 |

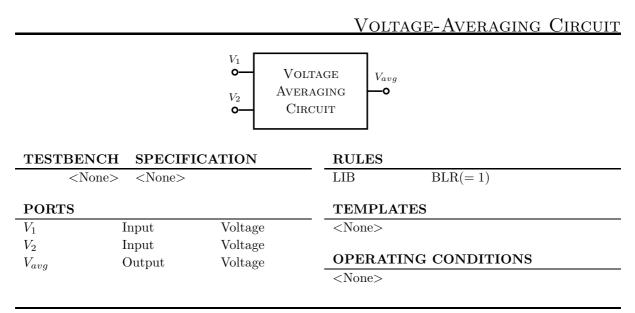

|   |                | 8.1.2    | Voltage-Averaging Circuit                                    |

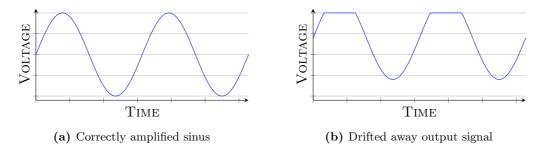

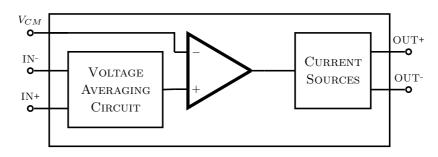

|   |                | 8.1.3    | Common-Mode-Feedback-Amplifier Circuit                       |

|   | 8.2            | Circuit  | Templates for Complex Circuit Classes                        |

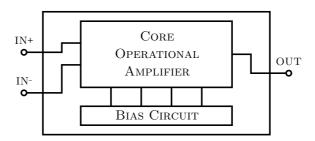

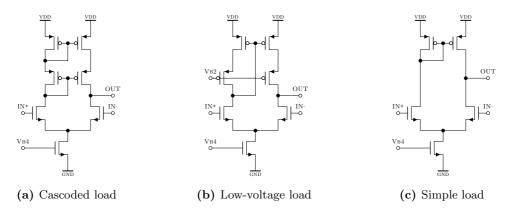

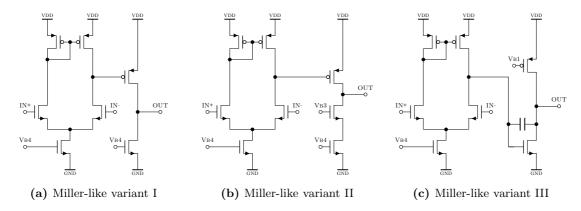

|   |                | 8.2.1    | Single-Ended Operational Amplifier (OP)                      |

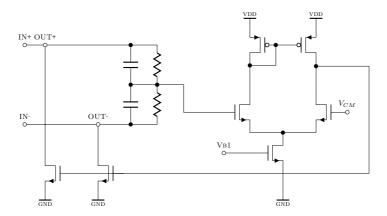

|   |                | 8.2.2    | Core Operational Amplifier (COREOP)                          |

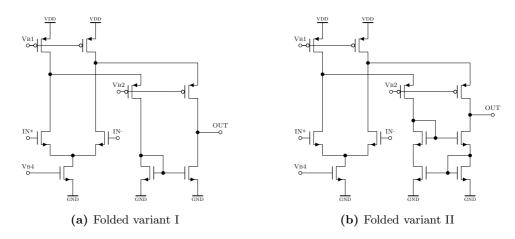

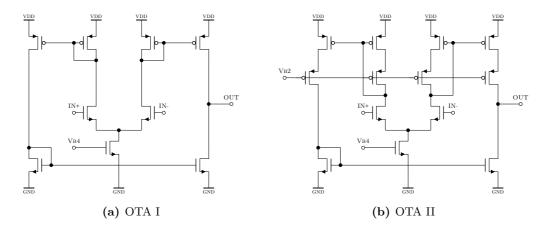

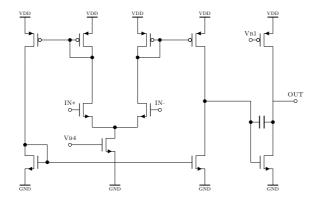

|   |                | 8.2.3    | Single-Ended Operational Transconductance Amplifier (OTA) 71 |

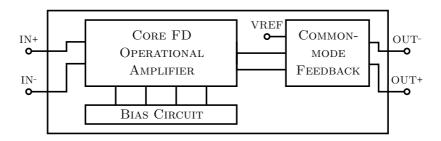

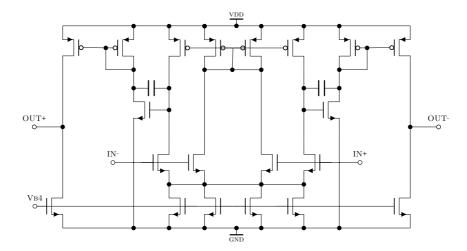

|   |                |          | Fully Differential Operational Amplifier (FDA)               |

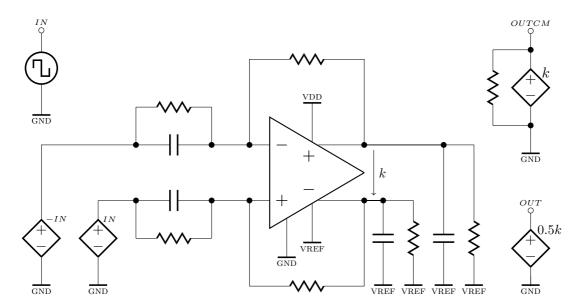

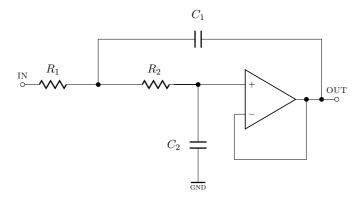

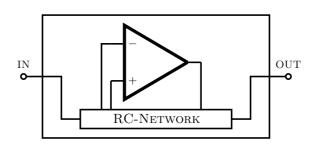

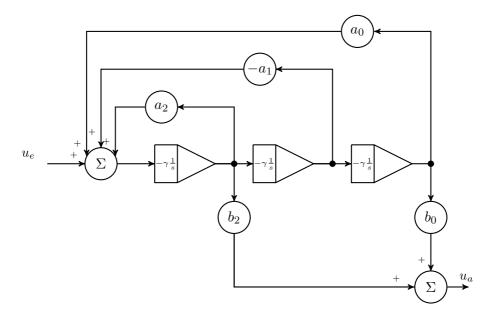

|   |                | 8.2.5    | Sallen-Key 2nd-Order Low-Pass Filter (SKLP)                  |

|   |                | 8.2.6    | Elliptical 3rd-Order Low-Pass Filter (ELIPLP)                |

| 9                 | Fiel                  | ds of Application for Analog Synthesis             | 81 |  |  |  |  |  |  |

|-------------------|-----------------------|----------------------------------------------------|----|--|--|--|--|--|--|

|                   | 9.1                   | Single-ended Operational Amplifiers                | 81 |  |  |  |  |  |  |

|                   | 9.2                   | Application Inside a System Design                 | 85 |  |  |  |  |  |  |

|                   | 9.3                   | Elliptical 3rd-Order Low-Pass Filters              | 86 |  |  |  |  |  |  |

|                   | 9.4                   | Computed Creativity—Current Stealer Design Pattern | 89 |  |  |  |  |  |  |

| 10                |                       | clusion                                            | 91 |  |  |  |  |  |  |

|                   | 10.1                  | Outlook                                            | 92 |  |  |  |  |  |  |

| Appendices        |                       |                                                    |    |  |  |  |  |  |  |

| $\mathbf{A}$      | Circ                  | cuit Class Testbenches                             | 97 |  |  |  |  |  |  |

| В                 | Basic Block Libraries |                                                    |    |  |  |  |  |  |  |

| List of Tables 10 |                       |                                                    |    |  |  |  |  |  |  |

| List of Figures   |                       |                                                    |    |  |  |  |  |  |  |

| Li                | List of Algorithms    |                                                    |    |  |  |  |  |  |  |

CHAPTER

ONE

## INTRODUCTION

Analog circuit synthesis is inevitably a long term goal for the industry. To accomplish this, various ideas have been investigated and brought to publications (see Section 3.1). The ongoing advances in processing technologies introduces this very need. The current scientific community around analog circuit synthesis may merely be divided into *circuit construction*, *parameter synthesis* and *layout generation*. The presented methodology focusses on the construction of circuits, which involves the generation of the circuits themselves (see Chapter 5) and despite that, the preselection (see Chapter 6) of feasible circuits for the following sizing.

**Figure 1.1:** Illustration of the trade-off between expert-knowledge and circuit count—due to the nature of the underlying problem this is a subjective view and based on the best knowledge of the author. The bell number is a theoretical synthesis approach described in Chapter 4.

The ideas for the construction of circuits span a very wide range and are further illuminated in Section 3.1. In this work the presented methodology aims to deliver a maximum amount of expandability and flexibility in terms of circuit sizes, circuit classes and potential applications. This originates in a theoretical analysis of the analog design space (see Chapter 4), which illustrates the non-applicability of a brute-force approach in synthesis by enumerating all possible circuits for a given number of components. This approach resembles the naive synthesis without blending in any (expert-) knowledge and thus may be found on the rightmost side in Figure 1.1. On the opposing side of Figure 1.1 the traditional manual design—in Section 1.1 further discussed—is to be found. FEATS introduces the necassary concepts to include and selectivly apply expert-knowledge, thus determine the amount of generated circuits. By utilizing an extendable circuit analysis (see Section 5.4.3) circuits are reliably discarded in an early stage of the synthesis. This not only reduces the runtimes of the whole synthesis, but furthermore the rate of good circuits (see Chapter 9).

## 1.1 (Traditional) Analog Circuit Design Flow

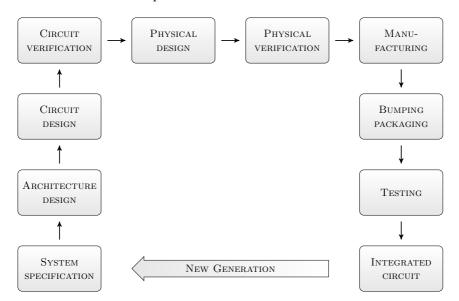

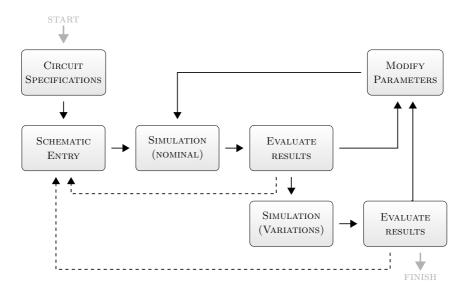

The current practice in analog circuit design, especially compared to the digital flow, is mainly driven by highly experienced engineers and mostly lacks automated design steps. Figure 1.2 presents a simplification of a typical design flow for an analog circuit module. The extremely time consuming task *circuit design* consists of several tasks as illustrated in Figure 1.3, which both from an automation point of view contain nearly no automatic steps. The tedious *modify* parameters, simulate circuit, evaluate results iteration—which easily eats up days to several weeks—still dominates the landscape.

**Figure 1.2:** A (simplified) illustration of the design flow for integrated circuits. The arrows do not imply a constant advancing towards this part—nowadays the step back may be of any distance, thus the backwards pointing arrows were omitted.

The digital design flow is widely dominated by design tools delivering high levels of automation and abstraction, which support the designer towards a finished design. This leads to a less repetitive design flow, where the designer may focus on the more important (higher-

level) tasks and thus avoids the overly tedious circuit design tasks. In particular the digital designer mostly focuses on Register-Transfer-Level design, which hides the used circuits into more abstract building blocks.

The challenges of designing an analog circuit inherently exhibit a much higher level of (computational) complexity due to the continuous nature of analog circuits. Designing an analog circuit from scratch commonly starts with the circuit construction, which usually involves a software for schematic entry, testing and evaluation, i.e., simulation. The schematic entry imposes the time consuming task of realizing an initial guess of the circuit by drawing and placing symbols or wires. Once an initial guess was realized as a schematic, the designer starts with the parameter synthesis in order to reach the specified performances for the circuit, while the former step (circuit construction) resembles a more or less discrete process: include the device? Interconnect net A with net B? The amount of combinations for a given set of devices is clearly countable and computable (see Chapter 4), thus the amount of possible circuits is still very huge. Contrary to this, the parameter synthesis (sizing) of an analog circuit totally lacks its counterpart inside the digital design flow. Digital modules are designed once and during synthesis, cloned thousands of times, leaving the parameter synthesis to the analog cell designer. Analog designers need to develop a new set of device parameters for each new analog circuit. This is mostly done with uncountable iterations of modify parameter and simulate circuit, which involves the interpretation of the results (see Figure 1.3). The results are mostly delivered through waveforms, which additionally means, it is not easily adaptable for others except the designer himself. For the parameter synthesis—one of the big challenges of analog circuit synthesis—some commercial tools lately started to successfully sustain inside the analog design software ecosystem. Multiobjective-optimization with additional constraints and a very high dimensional parameter space has widely been addressed with various numerical optimization techniques. Section 3.1 gives a short overview regarding the current state of parameter synthesis.

**Figure 1.3:** Simplified analog circuit design flow—zooming into the CIRCUIT DESIGN node from Figure 1.2.

Eventually, the designer identifies a set of parameters, which exhibit the required specifications. But, increasingly often the designer has to forfeit and restart from scratch, as the chosen circuit topology may not always be sufficiently parametrized towards the specified performances. This problem is constantly growing bigger up to a point at which the analog designer is forced to do statistical massaging, in other words: repeatedly (fine-) tune the parameters to get the best possible yield, while still fulfilling the specifications, provided he has found a suitable (nominal) circuit topology. Remarkably, the question whether another, better circuit topology - in terms of yield and/or reached specifications - exists or even could outperform the taken circuit in all aspects, is rarely asked.

In the final stage of development a (mostly dedicated) engineer receives the circuit in form of a schematic to realize the circuit on the physical level. This layout generation process requires as much additional information as possible, which could be extremely beneficial for the layout engineer. But usually it is carried out ranging from a handwritten sheet of paper to an informative phone call between the designer and the layouter. This traditionally grown handing over has recently shown its flaws. The rising complexity, mean variation, shrinking supply voltages and device sizes of recent technology nodes nowadays forces the layout engineer to create a layout, which involves by far more experience and insight into the circuit, as ever before. Matching devices, folding devices using various methods and different priorities of reliability for (groups of) devices lead to reduced process variations, if they are applied correctly.

For sake of completeness the *specification*, deliberately including the evaluation and storing of (simulation) results, recently gets increased awareness. Machine readable, standard-driven specifications, results and the evaluation of those do nearly not exist in industrial environments. Many analog design flows still rely on unstructured, *design documents* providing no insight and documentation about an ongoing or passed design project. Unfortunately, the development in this field is crucial for the applicability of analog circuit synthesis. Most of the analog circuit design automation tools suffer from the fact that almost no machine readable specifications are available, leaving the designer the responsibility to formalize and enter all necessary information into an analog circuit design automation tool.

## 1.2 Contributions and Publications

The first ideas towards the current methodology were published in [WH06, MMH11c, MMH11d], which are used as a blueprint for the core synthesis algorithm, although all rules were reformulated, some of the basic concepts still exist inside the presented work.

The synthesis core engine was one of the first addressed issues due to the limited string-based approach. The realized concepts where first published in [MMH11b, MMH11a] and are now based on graphs as circuit representations, which lead to a necessary increase in flexibility.

The whole methodology was further improved and extended to a more generic approach, while still maintaining a reasonable amount of generated circuits. Due to the application of a highly sophisticated isomorphism algorithm the methodology was enhanced and published in [MMLH12]. With the introduction of *circuit templates*, hierarchical synthesis gets feasible and opens up a wide range of possibilities for the methodology, which was published in [MH15].

Finally, various application studies also have been published. The impact of aging on different operational amplifier topologies was studied in [SHM13] and the applicability of ASDEX, a machine readable specification standard, on automated synthesis has been analyzed in [MMH12]. The (silicon proven) realization of a whole system has also been investigated in [vRMH15]. Furthermore, the methodology was presented in the form of invited talks at various conferences [Mei14, HM13].

#### 1.3 Overview

After providing a short introduction into the integrated circuit analog design process in this chapter, the following Chapter 2 provides the necessary formal representation used for circuits inside this thesis. Chapter 3 illustrates the analog circuit synthesis in general and the current scientific landscape—followed by Chapter 4 a theoretical analysis of the (analog) design space, which additionally introduces some important terms and distinctions for synthesis-driven analog design.

A technical in depth presentation of FEATS is given in Chapter 5 to pinpoint the most important concepts and features. Chapter 6 continues to describe the framework internals by illuminating one of the most distinguishing features, the preselection concepts. The middle part is closed with the inspection of the mechanisms for sizing (see Chapter 7) used inside the framework.

A selection of basic blocks and testbenches used throughout the whole framework is shown in Appendix B respectively Appendix A, together with the presentation of selected circuit classes (see Chapter 8) the framework is enabled to synthesize circuits. The application of the latter to actually generate circuits is demonstrated in Chapter 9. Finally, the thesis is finished with a conclusion in Chapter 10.

CHAPTER

**TWO**

## ANALOG CIRCUIT REPRESENTATION AS A GRAPH

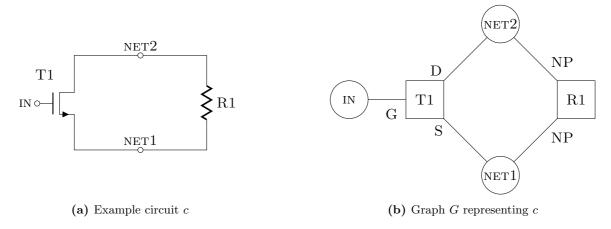

A circuit is represented through devices and nets—to encode them into an algorithmically processable representation—first we denote the set N as the *nets* and the set M as the *devices* of the circuit:

$$N := \{ \operatorname{net}_1, \operatorname{net}_2, \dots, \operatorname{net}_n \}$$

(2.1)

$$M := \{ \text{device}_1, \text{device}_2, \dots, \text{device}_m \}$$

(2.2)

The devices and nets are interconnected through k not directed edges.

$$E := \{e_1, e_2, \cdots, e_k\} \tag{2.3}$$

$$e = (u, v) \Leftrightarrow (v, u) : e \in E, u \in M, v \in N$$

(2.4)

The sets N and M are disjunct and summarized into V:

$$V = N \cup M : N \cap M = \emptyset \tag{2.5}$$

This allows the definition of the strict, bipartite graph G [Asr98] using Equation 2.1 to Equation 2.5:

$$G = (V, E) \tag{2.6}$$

The property *strict* is enforced by the fact that all nodes are only connected to their respective counterparts:

Figure 2.1: A circuit c represented as a bipartite-graph G

A set of basic blocks  $D^{bb}$  is also referred as a basic block library, similarly a set of abstract basic blocks  $D^{abb}$  is denoted as a abstract basic block library (see Section 5.2.2).

$$D^{bb} := \{bb_1, bb_2, \cdots, bb_n\}$$

$$D^{abb} := \{abb_1, abb_2, \cdots, abb_m\}$$

(2.9)

$$D^{abb} := \{abb_1, abb_2, \cdots, abb_m\} \tag{2.10}$$

Throughout this contribution a circuit c is a graph containing only basic blocks and their interconnections as defined in Equation 2.1 to Equation 2.6:

$$c = (V, E) : V = N \cup D^{bb}$$

(2.11)

A topology t solely consists of abstract basic blocks and resembles a more generic representation of (possibly) multiple circuits and is denoted as:

$$t = (V, E) : V = N \cup D^{abb}$$

(2.12)

Finally, a set of circuits C or topologies T will be named as followed:

$$C := \{c_1, c_2, \cdots, c_n\} \tag{2.13}$$

$$T := \{t_1, t_2, \cdots, t_m\} \tag{2.14}$$

CHAPTER

## THREE

## ANALOG CIRCUIT SYNTHESIS

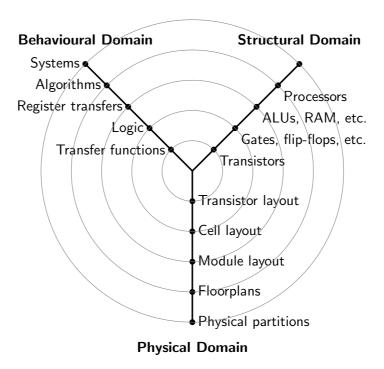

Analog circuit synthesis is a widely used term and therefore often also misused. Formally synthesis describes a step towards the middle inside the Y-diagram (see Figure 3.1), which leads to a reduction of the abstraction level and therefore a less virtual, more physical representation of the module is generated. While technically the understanding of synthesis in digital design significantly differs from the analog design approach. The general idea still remains identical: An (automated) design step, which converts the module one step further towards the physical realization.

Figure 3.1: Gajski-Kuhn Y-chart (from [YCh], license [LPP], unchanged)

The analog synthesis landscape differs massively compared to the digital. While the digital market is near saturation and highly heterogeneous in terms of (automated) digital circuit design software, the typical analog designer workstation nearly has not changed a little during the last years. The established analog design flow has not changed significantly since the advent of the SPICE simulator. According to various scientific contributions during the last years, one might get the impression, the problem is already solved [Rut10]. But a closer look reveals that parameter synthesis slowly achieves more acceptance and is used by a much bigger user base as it was only some years ago. But opposed to this, persistent tools, which allow automated circuit construction or layout generation could not sustain inside the semiconductor ecosystem yet. One of the reasons for this development may be the lack of flexibility among the synthesis tools seen on the market. Section 3.1 provides an extensive overview about the evolution of analog circuit synthesis in science and industry during the last years. As previously stated, the high specialization of the analog synthesis tools could be one of the reasons for the still very low acceptance inside the analog design community. Noticeably, the existing commercial parameter synthesis tools may technically be applied to any circuit in order to optimize the circuit for performance and/or yield, without inherent limitations in circuit size and classes.

## 3.1 State-of-the-Art in Analog Synthesis

In analog circuit design one might split the process into the *construction of circuits* and the *sizing*. This distinction has always existed (see [GR00]), but publications in analog circuit synthesis did not always fulfill this—admittedly this was not possible for a long time due to the lack of commercial sizing tools, which nowadays have successfully sustained inside the analog design ecosystem (e.g., [Mun, Cad]). Analog (structure) synthesis tools did not reach this state for various reasons, which are illuminated inside this section.

Early concepts for analog synthesis can be found in the late 80s, early 90s [HRC89, KSG90, MCR95, AB95]. Mostly the term "analog circuit synthesis" was used to actually describe circuit selection based ideas, which were closely coupled to their circuit libraries and carried out sizings based on pre-assembled parameter to performance rules or equations. While this approach lead to circuits which deliver a high degree of trust, these methods rise and fall with their accompanied libraries and sizing templates. Each new process node will always force a refinement of the library and its sizing templates. This refinement inherently leads to an enormous amount of work, which must be done upfront. The development of such libraries, i.e., the circuits and their individual sizing templates, may only be done by highly experienced analog design engineers—it is by far more difficult to design a generic circuit and its sizing templates than a regular circuit design towards a specific set of constant performances.

These methods retained a few process nodes, but as the effects of Moore's law get stronger, the aforementioned refinement gets increasingly complicated in terms of consumed time. Furthermore, the operating conditions have massively changed, i.e., the supply voltage has dropped significantly. This by itself is highly desirable—mainly due to the reduced power consumption—paired with a reduced voltage range, which will inevitably lead to changed circuit structures. Particularly this means various circuit constructions may not be used anymore, e.g., (multiple)

cascodes. This, together with 2nd-order effects due to the ongoing geometrical scaling (i.e., short channel effects) has largely lead to the fact that most of the research in this field has stalled. However, the selection, or library-based circuit synthesis approaches delivered very *trustful* circuits, inherently by the fact that solely circuit topologies are used which were previously designed from scratch by experienced analog designers.

Consequently, the natural next step is the opposing extreme. This was primarily done with brute-force like approaches by Klumperink et al. [KBN01, BKN00]. Remarkably, this approach has an explorative nature, which is maybe the first of its kind. The circuit generation is based on the idea of modeling a MOS-device as a voltage-controlled current-source, which seems reasonable as long as one solely aims to generate circuits containing exclusively MOS-devices in saturation and strong inversion. This approach already encounters the challenges of exploration based circuit synthesis. By generating all possible interconnections between a very limited number of MOS-devices this approach generates a vast amount of circuits already for device counts of three. Notably, this methodology exposed the challenges of exploration-based analog circuit synthesis to the scientific community:

- Vast amounts of circuits with very small component counts show the need for a preselection methodology

- Even well performing circuits lack trust

- Sizing has to be considered during analog circuit synthesis

- Analog circuit synthesis without blending in any (expert) knowledge will never be feasible (see Chapter 4)

While the explorative idea itself looks very promising, the computational effort to actually apply a full design exploration—without introducing (knowledge-based) bounds for the design space—is huge.

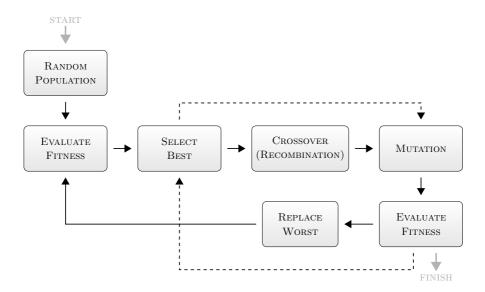

During the same time the evolutionary algorithms (see Figure 3.2) were first applied for circuit synthesis. Evolutionary algorithms try to mimic the evolution—inspired by nature itself. Therefore, a chromosome represents the circuit (or the building instructions for a circuit), which is also called the genotype of the circuit, whilst the incarnation of the latter is noted as phenotype. An initial population, i.e., a set of chromosomes, is generated randomly. For each of them the fitness is calculated by a specific fitness function. Based on this, the best individuals are chosen (parents) which are now being used for crossover and/or mutation in order to generate a new generation. The fitness function is now applied to the new individuals. Finally, the least-fit population is replaced with new random individuals and the process is repeated until a specified end condition is reached. This could be a maximum generation count or a desired fitness function target.

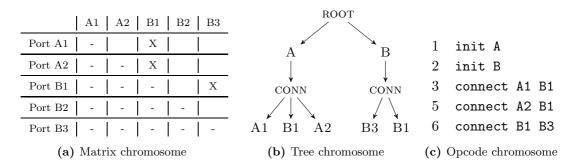

Kruiskamp et al. [KL95] presented *DARWIN*, which introduced a matrix representation of the circuits as in Figure 3.3a to be synthesized. In particular the rows and columns of the matrix represent a component and each cell is either true or false, which translates to a connection between those two components. This method introduces an approach which allows easy insight

**Figure 3.2:** The typical—biological inspired—evolutionary algorithm flow. Various modifications are known to this flow—dashed lines resemble alternate flows.

into the evolutionary process, as crossover and mutation operations may be visualized with ease. This method introduces various very circuit class specific properties, which may not be easily adapted for other circuit classes, thus it inherently restricts the application scope.

Koza et al. [KBL<sup>+</sup>97] proposed a tree structure chromosome as shown in Figure 3.3b to represent circuits. Starting with a so-called embryonic circuit the circuit gets evolved using component-creating functions, connection-modifying functions and arithmetic-performing subtrees which may solely be applied to components. Each group has several specific functions realizing design steps, which are highly specialized on specific components, which significantly reduces the flexibility and expandability of this approach. Furthermore, the memory footstep and thus the computational overhead is significant (see [AII03]). Despite this, these properties implicitly introduce restrictions for the size of the circuits to be synthesized.

Another approach tailors the genotype description of the circuit by means of *opcodes* (see Figure 3.3c) similar to what happens during translation of assembler code. Lohn et al. [LC99] thus represent a circuit as a set of chronologically executed operations, which finally construct a circuit. This approach is quite similar to what has been done by Ando et al. [AII03], but is here explicitly named as *variable length chromosome*. Strictly seen, except for the matrix approach (see [KL95]), most evolutionary synthesis methodologies use some kind of variable length chromosomes. Although it is worth to be mentioned, as the natural blueprint is obviously based on a constant length chromosome. On the other side, a variable length chromosome for circuit synthesis is clearly the correct representation due to the fact that circuits themselves have a variable length, respectively size.

A major drawback for the previously discussed methods is the integrated sizing mechanism. While on the first view the integration of sizing into circuit construction allows a higher circuit throughput due to the tighter coupling between circuit construction and sizing, the comparability and the reliability of the methodology strongly correlates with the quality of the sizing methods

**Figure 3.3:** Simplified illustrations of various used chromosomes for evolutionary synthesis for two example devices A and B with two, respectively three ports.

and algorithms. Admittedly this was the only way to generate any presentable results, as commercial sizing software emerged during the last ten years at least, making it impossible to use a state-of-the-art sizing tool during the time of these contributions. Another issue arises once a closer look is taken at the generated circuits, which are often very uncommon and thus lack trust, leading to a reduced acceptance of these among the analog design community.

A widespread solution for the lack of trust is the concept of basic blocks. First introduced by [DCR05] and Wang et al. [WH06] the concept has been widely used (see [MPSG09, DV08]) to overcome the trust drawbacks and to reduce the computational complexity of analog circuit synthesis.

The latest incarnations of the evolutionary methods are resembled through the contributions by Das et al. [DV08] and McConaghy et al. [MPSG09]. While the former employs hierarchies indirectly, the latter explicitly uses an hierarchical approach to propagate properties of building blocks from bottom to top. This leads to so-called *flexible* and *compound blocks*, which may contain several *atomic blocks*. This approach exhibits similar properties, in terms of full design space exploration, but limits itself as it is not truly exploring the design space, due to the stochastic nature of the underlying evolutionary algorithm.

Furthermore the analog circuit synthesis landscape is full of (semi-)automated methodologies aiming to be applicable for specific circuit classes only. Starting with passive filter synthesis (see [DV07, CHS06]), switched capacitor filter synthesis [AEBD00], low noise amplifier synthesis [TB08, BKN04, TB05], low drop out circuits [DM09] to  $\Delta\Sigma$ -synthesis [TD06]. Assistant based tools were also investigated, which support and guide the designer through the development of an analog circuit [SKP05]. Inherently those methodologies suffer from their limited applicability, which may be one of the primary reasons why, to the best knowledge of the author, none of them emerged into an actual commercial tool.

In contrast to the analog circuit synthesis, the analog parameter synthesis, i.e., automated sizing has successfully reached and sustained inside the industrial analog design ecosystem. The most prominent and successful ones are based on worst-case distances (see [AGW94, AEG+00]). Further ideas have been developed in this field based on support vector machines [DBNV05], geostatistics performance modeling [YL07], downhill-driven stochastic parallel recombination [KPH+01], discretized sizing [JCK12], spline center and range methods [BKV09] and hybrid evolutionary-driven methods like presented in Lourenço et al. [LH12]. Especially, the concepts

based on *geometric programming* have been applied in various forms to the parameter synthesis problem. Even selection-based synthesis methods—by sizing a library of circuits and returning the *best* one—have been brought to publications. Generally, a geometric program is an optimization problem of the form:

$$f_i(x) \le 1 \quad i = 1, \cdots, m \tag{3.1}$$

$$h_i(x) = 1 \quad i = 1, \cdots, p \tag{3.2}$$

$f_0, \dots, f_m$  are posynomials and  $h_0, \dots, h_p$  are monomials. By formulating the specifications to be reached as posynomial functions the geometric program may be converted into a convex optimization problem. This is done by taking the logarithm of the input variables, objectives and constraints. The very same posynomial formulations are the self induced limitations as the handwritten posynomials mostly rely on first-order models as in [MV01, dMH04]. Geometric programming promises a very fast calculation of a global optimum using interior point methods. Still, the applicability is questionable due to the fact that most posynomials are handwritten and not easily deducted in an automated process. An approach to overcome these drawbacks is presented by Aggarwal et al. [AO07], they focus on the automated generation of posynomial equations. Though the current ideas are applied only on transistor model parameters (implicitly assuming saturation and inversion), they do not (yet) address full circuit level specifications. Eventually, geometric programming has also been applied to model and include layout-dependent effects into the sizing process [ZLY+12].

Generating a layout from a given circuit is the obvious final step to tackle in order to accomplish a higher degree of automation in analog circuit design. Graupner et al. [GJW11] presented a generator based approach, which is based on executable design flow descriptions. This translates to a programming inspired analog circuit design approach by providing a set of procedures and functionalities, which may be used to describe the steps to be taken in order to generate a target circuit. Although this method allows automated circuit and layout generation, the description of design steps using a programming language is not the most intuitive way for an analog design engineer. Other methodologies to automatically layout an analog circuit have been proposed (like [LVGH06, ESL<sup>+</sup>11]), which mostly have to pre-process the target circuit by means of symmetry, matching and partitioning. This inherently is a hard challenge due to the fact that the previously included design knowledge during circuit sizing and construction gets lost and has to be extracted from the circuit schematic. Thus an automated layout would benefit massively from the (formalized) information, which could be delivered by an automated circuit generation methodology.

Finally, this work addresses the problem of isomorphic circuits during circuit construction. This is, by the best knowledge of the author, the first approach handling this inevitable problem. There have been contributions addressing the automated extraction of similarities and symmetries (see [LVGH06, ESL+11, Eic13, EG12]) but isomorphism by itself was never illuminated. Generally a similar problem occurs during the layout vs. schematic design step and is fully solved inside the commercial design automation environments. First contributions in this field are found in the 90s and serve as a base for current realizations [Ebe88, OE93].

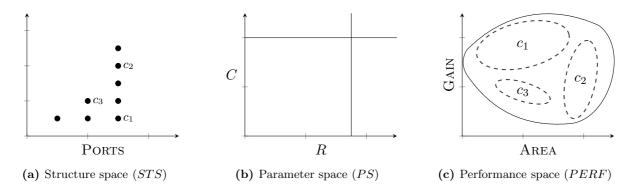

#### INTROSPECTION OF THE ANALOG DESIGN SPACE

The increasingly often abused term design space is mostly used in conjunction with circuit synthesis. Thus sometimes misused in the context of sizing, where obviously parameter space should have been used. The aim of this chapter is to provide an exact enumeration of all possible circuits for a given number of ports, and furthermore to put this into relation with the presented analog synthesis framework. Finally the following excerpts should provide a precise distinction between the terms structure space, parameter space, design space, and performance space.

## 4.1 Enumerating the Design Space Using the Bell Number

Before analyzing, or even enumerating, the structure space, it has to be defined. As a preparation, it is worth taking a look at nets and components. In fact the components, i.e., the type of the component has, despite of its number of connections (i.e., ports), no influence on the *size* of the structure space. Translating this formalism to reality means, a circuit containing two nMOS components, opens up a structure space, which has exactly the same size as the resulting structure space for three simple (bipole) resistors—in distinction to the design space, which includes the parameter space and thus differs.

While this seems unintuitive, this is a direct consequence of the absence of an (easily) computable mapping between functionality and circuit structure in analog circuits. The following investigations of the analog design space is thus a very important step to further understand the challenges of analog circuit synthesis. Furthermore the possibility to state the opposing: "It is impossible to synthesize the specified circuit." <sup>1</sup>.

The following Lemma will support these thoughts and first denote an important property of the structure space:

**Lemma 4.1** (Structure Space Size/Dimensions). The structure space has w.l.o.g. only one dimension, this translates to an unordered set of items, all without any particular order or direct

$<sup>^{1}</sup>$  Impossible is to be understood as a simplification for "Mathematically not computable, using all computing power on earth for the next 1,000,000 years."

relation to each other. The size of structure space STS will be noted as |STS| and is strictly defined by the number of circuits inside the structure space.

Once the size |STS| is well defined, the circuits inside STS can be further illuminated. A hypothetical circuit synthesizer, which fills the structure space with circuits, does w.l.o.g. not take any circuits' functionalities or electrical properties into account during circuit synthesis, thus making no assumptions about the (potential) functions of a circuit.

In contrast, there are various structural characteristics, which will be defined in the following:

**Definition 4.2** (Circuits Inside The Structure Space). For each circuit c associated with a structure space STS the following applies:

- a) For each circuit c there is no other circuit c' inside the analog design space  $DS_A$ , which is structurally identical.

- b) Outer pins for each circuit are omitted.

- c) All circuits have the exact same amount of component ports.

Given these preconditions, the *structure space* starts to get manageable. But first a quick explanation, why these definitions are very helpful without introducing unnecessary simplifications, i.e., they do not reduce the complexity of the analyzed problem. Item a) is pretty self-explanatory, as identical circuits inside the structure space set would not be helpful for a formal analysis. Furthermore Item b) is, at least, easily approximated in terms of how many circuits are forked from one. Omitting the outer pins sounds more infringing as it actually is. Given n outer ports and m nets inside a specific circuit  $c_i$  (with m being the total number of nets and n a portion of it), the number of forked circuits  $|C_{c_i}|$  is easily calculated, assuming no outer port is shorted with another outer port.

$$|C_{c_i}| = \frac{m!}{(m-n)!}$$

:  $m > n$ ,  $m \in \mathbb{N}^+$ ,  $n \in \mathbb{N}^+_{\geq 0}$  (4.1)

During analog synthesis the outer pins are actually very important and ignoring them would generate enormous amounts of useless circuits. Nevertheless in this context, the amount of circuits generated through the Equation 4.1 is compared to the structure space, just a little fraction. Especially, from the complexity point of view, i.e., the asymptotic behavior is very good natured. Equation 4.1 would usually rise in a very steep fashion with respect to m and n—fortunately only m is getting (significantly) bigger with larger circuits. In contrast to n, which represents the number of outer ports of the circuit. For analog circuitry the outer pins can be nearly seen as constant in the context of asymptotic behavior. Additionally, Equation 4.1 rises at the fastest rate if the denominator gets smaller, until it reaches 1, what resembles the nonexistence of the denominator, thus the equation would rise equally fast as any other factorial. Summarized, this means Item b) from Definition 4.2 may safely be applied. Finally, Item c) has no actual impact on the methodology or the analysis, moreover it emphases the fact that in the context of analog design space analysis the number of component ports inside a circuit determines the complexity and dominates the growth.

Given the previous observations the following definition of a structure space may be given:

**Definition 4.3** (Structure Space). Let K be a specific set of components and P(K) the set of all ports provided by the components. The number of ports will be denoted as |P(K)| with  $f \mapsto \mathbb{N}$  being the function to determine the actual size. This allows the definition of the structure space for a given number of ports:

$$STS(K) := f(|P(K)|)$$

The following challenge is to actually determine f. Therefore a simple reinterpretation of the circuit and its contents is needed. Let's assume the *circuit* consists solely of a tripole device (e.g., an nMOS-device) with three pins named D, G and S. As previously stated, the outer connections of this circuit are omitted, thus the task is to determine how the three pins may be interconnected. For this example all possible interconnections are easily enumerated:

$$\{D, G, S\} \rightarrow \{(D, G, S)\} \tag{4.2}$$

$$\rightarrow \{(D), (G, S)\} \tag{4.3}$$

$$\rightarrow \{(G), (S, D)\} \tag{4.4}$$

$$\rightarrow \{(S), (D, G)\} \tag{4.5}$$

$$\rightarrow \{(D), (G), (S)\} \tag{4.6}$$

A net—the set of shorted pins—is described by all pins inside one pair of parenthesis (right hand side). Although this notation is very uncommon in electrical engineering, it perfectly matches the common notation of partitions of a set. As the name suggests: on the left side of Equation 4.2 is the set and the partitions on the right Equation 4.2 to Equation 4.6 resemble all possible interconnections of the pins.

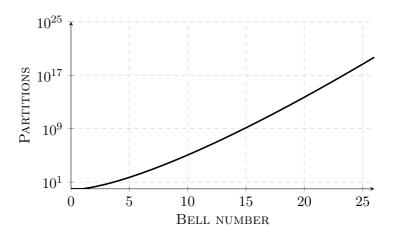

In math partitions of a set is a widely known and analyzed concept. Furthermore, the number of partitions of a set can easily be calculated using the  $Bell\ number$  [Aig99]. Knowing this, it is now possible to define f from Definition 4.3 and thus the exact size of the structure space for a given set of components respectively pins.

Each circuit resembled as a dot in Figure 4.1a, furthermore spans a parameter space, which dimensionality is equal to the number of freely adjustable design variables. The example in Figure 4.1b therefore shows a C (capacity) and an R (resistance) with their boundaries. It is worth mentioning that the parameter space, opposing to the design space it is nearly continuous. Nearly because in real process technologies there is a manufacturing grid, which technically allows only discrete steps for a particular design variable (component parameter).

**Definition 4.4** (Parameter Space). Each circuit c spans its own parameter space PS(c). The degrees of freedom for this parameter space is determined by the number of design variables for this particular circuit c.

**Definition 4.5** (Design Space). The cross product of the structure space STS with the parameter space PS resembles all possible circuits including the sizing.

$$STS(K) \times PS(c) = DS(K)$$

Figure 4.1: An illustration of the degrees of freedom within a circuit development process.

Noticeably, the design space by itself is not bound and grows infinitely. To restrict it and to provide understandable limits, the Definition 4.3 may and should by applied in order to get a manageable enumeration of the design space. Eventually, the design space is mapped into the performance space (PERF) as shown in Figure 4.1c.

**Definition 4.6** (Performance Space). Let DS(K) be the design space spawned by the structure space STS(K) and the parameter space PS(c). Each (sized) circuit inside DS(K) maps to a point inside the performance space PERF. The dimensionality of the performance space is determined by the number of performances.

$$DS(K) \mapsto PERF$$

Unfortunately, the mapping is not bijective, i.e., it is not possible to directly derive the parameters and the design of a circuit from a given set of performances. So the only way to fulfill a given set of performances is to *qo from left to right*.

The following Table 4.1 should provide an orientation for the reader how complex this task may be without including *expert knowledge* into the process. One may instantly see the very steep increase of the number of possible circuits, which undeniably leads to the fact that circuit synthesis without blending in expert knowledge is unfeasible (see Chapter 1). This should moreover serve as a motivation to include this aforementioned expert knowledge into the framework.

Table 4.1

Bell Numbers from 1 to 16

| Ports | $B_N$ | Ports | $B_N$                  |

|-------|-------|-------|------------------------|

| 1     | 1     | 9     | 21,147                 |

| 2     | 2     | 10    | 115,975                |

| 3     | 5     | 11    | 678,570                |

| 4     | 15    | 12    | 4,213,597              |

| 5     | 52    | 13    | 27,644,437             |

| 6     | 203   | 14    | 190,899,322            |

| 7     | 877   | 15    | $1,\!382,\!958,\!545$  |

| 8     | 4,140 | 16    | $10,\!480,\!142,\!147$ |

Figure 4.2: Graph showing Bell numbers

Table 4.1 and Figure 4.2 impressively show the steep rise of the bell number. The Bell number may be calculated using a recursive expression, with  $B_0 = 0$  being defined previously.

$$B_{n+1} = \sum_{k=0}^{n} \binom{n}{k} B_k \tag{4.7}$$

There are various other possibilities to calculate the Bell number and even more approximations, which are not further investigated, as they deliver nothing beneficial for the current analysis.

Nevertheless, these numbers impose a suitable—moreover, even a precise upper boundary for the number of structures to be generated from a given set of components. Fortunately, this is a theoretical analysis and is primarily presented to highlight the capabilities of an analog design engineer. Based on experience, simple calculations and elementary electrical rules for voltage and current, a designer develops circuits without even remotely exploring the full structure space. In other words, the designer utilizes expert knowledge (see Chapter 1) to implicitly discard the vast majority of the structure space. Some, but not all, are directly applicable to the here presented net-based circuit representation, e.g., the amount of ports connected to a net is, except for the supply and ground nets, rarely above four.

By imitating and formalizing the methods the analog circuit designer uses to develop circuits, the presented framework is able to reduce the number of circuits to be evaluated down to a reasonable amount—Chapter 9 aims to provide empirical proof for this statement.

CHAPTER

# **FIVE**

# A FRAMEWORK FOR EXPLORATIVE ANALOG TOPOLOGY SYNTHESIS

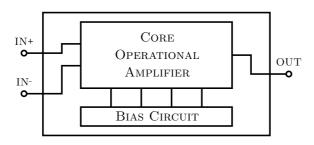

Figure 5.1: FEATS' top-level flow

The framework consists of several steps, which are visualized in Figure 5.1. Inside the current chapter the various steps and inputs of the synthesis are explained in detail to allow a clear view into the internals of the presented methodology.

As discussed in Chapter 4, the *design space* for analog circuits grows rapidly for rising numbers of used components. Although an analog design engineer is able to build circuits with large component counts, one might get the impression an algorithmic approach may never get even near to this point. The actual number of somehow useful circuits inside this huge design space resembles only a tiny portion.

The primary design goal of the presented explorative topology synthesis engine is the possibility to precisely control how much knowledge is included into the synthesis process. As described in Chapter 3, the process of *circuit construction* may range from pure brute force approaches (see Chapter 4) to hand crafted, experience based circuit creation. The presented framework aims to provide both extrema and additionally anything in between. Clearly the framework itself may not—out of the box—provide this functionality, but moreover it provides the, literally spoken, *framework of tools and hooks* to allow the user to tweak and configure the software in order to get the desired results.

# 5.1 Methodological Considerations and Design Targets

The primary design targets for an analog synthesis framework are easily enumerated:

- Flexibility / genericity

- Process independence

- Circuit(-class) independence

- Arbitrary hierarchy

- (Hardware) platform independent

- Optimizer / simulator independent

- Good-natured scaling

- Semantically rich

While the claimed *flexibility* and *genericity* are more a product of the whole framework itself and are not so easily explained and pinpointed. The other points may be directly matched with features provided by the framework.

The previous enumeration does not imply any kind of ordering, but process independence is most likely one of the most important points to fulfill. A synthesis framework without a strong emphasis on process independence will most likely be obsolete at the moment the target process will be replaced. The presented synthesis framework considers changing process parameters and other process dependent changes throughout the whole implementation. Starting with the components (see Section 5.2.1) the framework already abstracts the atomic building block. In application this means there is an arbitrary count of different atomic components to be used inside the synthesized circuits. Preparing the framework for current (and following) technology nodes, which already exhibit various different components like resistances, capacitances, and a wide variety of MOS-components, which mostly target specific use cases. By giving a component a semantically rich description, like: driving MOS-component, high capacity capacitor, high precision resistance etc. the component may easily be mapped to an equivalent component

provided by a specific technology node. By additionally measuring different properties of the target process node, various *numerical properties* are extracted, which are taken into account during the semi-symbolic circuit evaluation (see Chapter 6) executed by the *analyzing rules* (see Section 5.5).

A circuit class independence goes hand-in-hand with the need to have the possibility to describe arbitrary hierarchies. The presented synthesis framework allows hierarchies of arbitrary depths with circuit templates, these may contain any number of circuit templates themselves, which allows the user to create circuits and hierarchies of any depth. By further allowing to assign different libraries of basic blocks, as shown in Appendix B, to any circuit template type—the user moreover gets the possibility to combine different types of circuits together to construct circuits of arbitrary complexity and size.

By platform independence it is not specifically meant to be independent from ARM, x86 or any other hardware architecture (although it is), moreover the aim is to not be dependent on big computing capacitances. In simple terms, the framework should work with a reasonable speed on a decent enterprise scale workstation. But additionally, it should scale well to an arbitrary number of servers and/or workstations. Therefore various levels of abstraction were realized, which are partly observable as clearly distinguished inputs (see Section 5.2), but additionally the synthesis framework internally does an extensive preprocessing of the inputs in order to further reduce the needed computational effort (see Section 5.3).

Optimizer independence is ultimately also essential for a synthesis framework, to state flexibility and genericity. The framework provides a construct named application server (see Chapter 7), which allows the execution and control of any tool, which may perform any desired circuit evaluation. This includes the simulator independence, as this is a part of the aforementioned. Furthermore this realizes the good-natured scaling, as there may be any number of application servers, which are all handled by the task manager. This manager (see Chapter 7) is additionally able to distribute evaluation tasks in an asynchronous manner, which enables the framework to scale very efficiently across any number of servers and/or workstations.

# 5.2 Inputs for a Circuit Synthesis

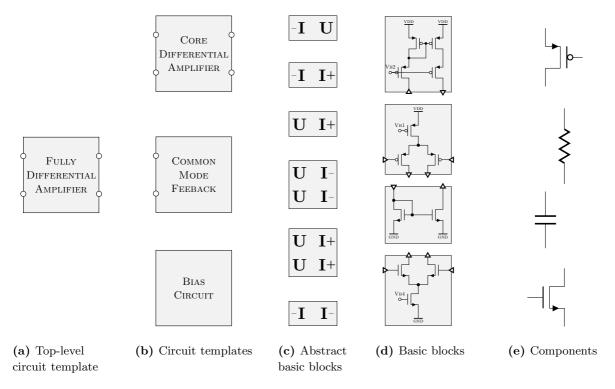

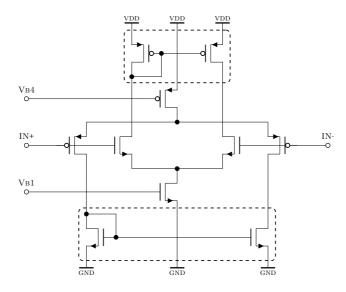

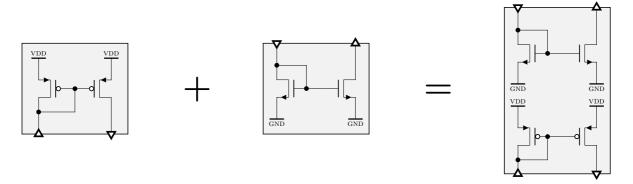

Apart from a configuration file for the synthesis process, which handles the administrative details of the synthesis and the configuration files for the various application servers, there are exactly three types of inputs. Each of these serving a specific degree of abstraction. The framework clearly divides those three types of inputs, in order to maintain a clean and consistent hierarchy. Figure 5.2 illustrates the supported levels of abstraction, which will be described in the following sections.

#### 5.2.1 Components

To describe the *atomic* building elements of circuits, *components* are used inside the framework. The here presented concept of component abstraction was not yet published and represents

**Figure 5.2:** Examples for the various levels of the hierarchy used in FEATS. From left to right, each one representing a level descent. Further descriptions of each level are to be found in this chapter.

another recent consistency addition to the framework to further increase the genericity. The following enumeration lists a selection of possible components and their variants:

- Current source (independent)

- Voltage-controlled current source

- Current-controlled current source

- Voltage source (independent)

- (High-precision) resistance

- (Low-precision) capacity

- Switching nMOS/pMOS device

- Driving nMOS/pMOS device

- nMOS/pMOS device (in saturation)

- (Zener) diode

- Two/three port short

Each component may provide a variety of different properties to actually describe the component's behavior. The following attributes may be used to describe a component:

- Unique name (type of the component)

- Number and naming of connections

- Constraints as inequalities

• Process dependent attributes (e.g., min/max/typical dimensions, area approximation factor, manufacturing grid)

Components serve as the atomic building elements of each synthesized circuit, thus this leads to some implications. A component may never be divided somehow and it always resembles exactly one (physical) *part*, which may be mapped directly to a counterpart provided by the technology node. In particular, components do not exhibit any kind of behavioral description or functionality.

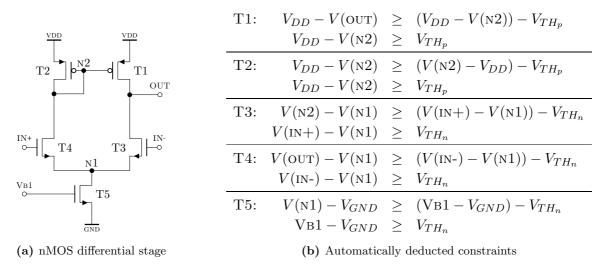

#### 5.2.2 Basic Blocks

Functional building elements inside the framework are characterized through basic blocks, which may also be called basic functional blocks. These serve as building blocks inside a circuit, which exhibit functional properties. They exclusively contain components, which are interconnected and annotated in order to describe a specific functionality. A brief selection of some predefined—but easily expandable—basic blocks follows:

- nMOS/pMOS current mirror

- nMOS/pMOS differential stage

- Rail-to-rail differential stage

- (Cascoded) current source

- nMOS/pMOS common-source stage

- Inverter

- Push-pull output stage

- (Four level) bias circuit

- nMOS/pMOS gain-booster stage

In contrast to components, basic blocks may contain additional information of functional nature. Primarily these are attributes related to the I/O characteristics and generic port attributes. Additionally, relations between the components contained inside the basic block, but also global relations which can later be used as hints for a successful sizing.

- Number of ports and their properties

- Input, output, local reference, or global reference

- Nature of the port: current or voltage

- If applicable, the bias current direction: *positive* or *negative*

- Sizing hints

- Local sizing variable

- Global sizing variable

- Fixed numerical value

- Fixed maximum/minimum value

Especially, the distinction of the *(global)* reference and local reference port property needs some explanation. Generally any port which does not carry a signal may be handled as a reference, therefore FEATS transparently adds reference ports to the next higher hierarchy once they are needed. This features comes very handy for smaller circuit templates, as long as there is no other instance of a single circuit template inside the same level. Assuming both contain e.g., an enable circuit, or a bias circuit, which differ in both instances of the circuit template. Once inserted into the top-level circuit template, implicit interconnections between those two instances occur, as obviously their reference ports' names match. This challenge can easily

be mastered by introducing *local reference* ports, which automatically rename themselves once there are identically named *local reference* ports inside the same hierarchy-level.

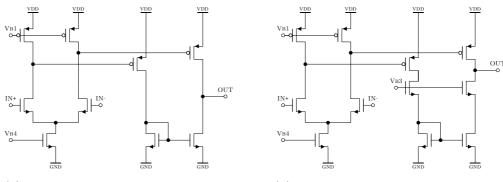

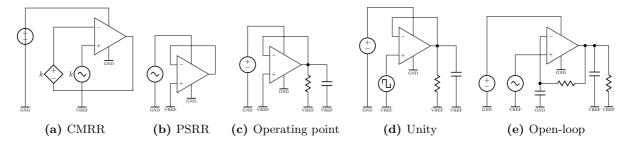

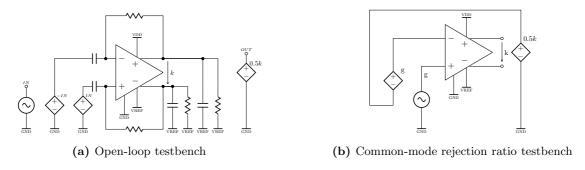

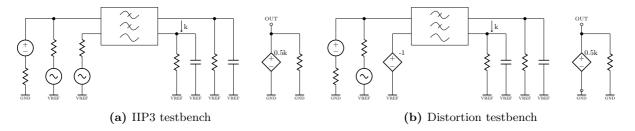

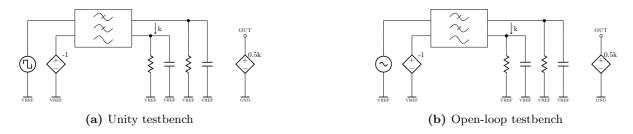

## 5.2.3 Circuit Templates