# Verifiable computation using multiple provers

Andrew J. Blumberg\* Justin Thaler<sup>†</sup> Victor Vu<sup>‡</sup> Michael Walfish<sup>§</sup>

#### **Abstract**

The increasing ubiquity of the cloud computing paradigm has renewed focus on the classical problem of allowing weak clients to check the results of computation *delegated* to powerful servers. Recent advances in proof-based verifiable computation have led to several near-practical protocols. Protocols based on *interactive proofs* (IPs) work with highly restrictive models of computation and are thus efficient only for a limited class of computations. In contrast, protocols based on *argument systems* apply to a much larger class of computations, but efficiency requires amortization of very expensive setup costs.

This paper initiates the study of the practical efficiency of *multiprover interactive proofs* (MIPs). We present a new MIP for delegating computation that extends insights from a powerful IP protocol (Goldwasser et al., STOC, 2008). Without reductions or amplification, our protocol uses only two provers (departing from prior work on MIPs), and achieves both the efficiency of interactive proof-based protocols and the generality of argument system-based protocols. Also, this result, together with recently developed machinery, creates a potential avenue toward concretely efficient arguments *without* setup costs.

We describe Clover, a built system for verifiable computation, based on our protocol. Although Clover does not implement the full theory (it has setup costs), it applies to problems that existing IPs cannot efficiently handle, and achieves performance comparable to, or better than, the best argument systems.

<sup>\*</sup>The University of Texas at Austin

<sup>&</sup>lt;sup>†</sup>Yahoo! Labs. The majority of this work was performed while the author was a graduate student at Harvard University. Supported by an NSF Graduate Research Fellowship.

<sup>&</sup>lt;sup>‡</sup>Sandia National Laboratories

<sup>§</sup>New York University

## 1 Introduction

In recent years, the rise of cloud computing has renewed interest in the problem of how a weak client can verifiably outsource computation to a powerful but untrusted server. As a motivating example, suppose that a client wants to use the cloud to perform an expensive computation. There are many potential sources of error in the results, including bugs in the server, hardware failures, and malicious behavior. In such applications, it is often infeasible for the client to locally verify the correctness of the results.

There are many solutions to this problem (e.g., replication [6, 29, 45, 50, 55], trusted hardware [30, 65], attestation [5, 56, 62, 66, 67, 73], or auditing [45, 47, 59]) that make strong assumptions about the usage model or setup (e.g., uncorrelated errors, a chain of trust, intermediate results amenable to checking, etc.).

It has long been known that there are theoretical solutions to this problem that make no such assumptions other than perhaps standard cryptographic ones [8, 9, 40, 40, 42, 46, 51, 54, 72]. Roughly speaking, the client, or *verifier*, and server, or *prover*, represent a high-level program as a circuit; verification consists of the prover using cryptographic or complexity-theoretic machinery to convince the verifier that it holds a valid assignment to the wires of the circuit. Recently, there has emerged a new area of secure systems research, called proof-based verifiable computation [78], that strives to build real systems using refinements of the theory [17, 18, 26, 31, 61, 68–71, 75, 76]. Principal goals of these systems are to have minimal overhead for the prover and for verification to be cheaper for the verifier than doing the computation locally.

Three approaches have been implemented. The first is based on *interactive proofs* (IPs) [11, 40, 42, 54, 72] and is due to Cormode et al. (CMT) [31, 74, 75], who refined the GKR protocol [40]. The second approach combines cryptographic commitments [51] with probabilistically checkable circuit encodings (of the kind that appear in probabilistically checkable proofs, or PCPs [8, 9]) to obtain efficient *argument systems* [25] (i.e., interactive proofs secure only against polynomial-time provers). Setty et al. [26, 69–71] build on work of Ishai et al. [46] and GGPR [37]. The third approach is based on *non-interactive* arguments (also known as SNARGs [39] or SNARKs [21]). Parno et al. describe a system [61] that realizes the full promise of GGPR [37]; Ben-Sasson et al. [17, 18] likewise build on GGPR and several other works [15, 24].

The IP-based approach of CMT has a number of advantages. Most notably, for circuits with *regular* wiring patterns (defined formally in §4.5.3; roughly, the circuit consists of repeated, structurally similar blocks [31, 74]), CMT does not require preprocessing, has a highly efficient verifier, and achieves extremely low overhead for the prover [74] (small constant factors over native execution). By contrast, the argument systems require an expensive preprocessing stage for the verifier and have very high prover overhead. On the other hand, CMT is less general. It applies only to small-depth circuits (i.e., parallelizable computation). And it does not support *non-deterministic circuits*, which can be extremely useful for representing high-level programs as circuits [15, 17, 26, 61, 69, 71]; operations such as random memory access and comparisons, among others, are problematic for interactive proofs but not argument systems.

Our goal in this paper is to develop a protocol that simultaneously achieves the efficiency of CMT and the generality of the argument systems. To accomplish this, we give up on the single prover of prior built systems. Instead, we develop a practical implementation of *multi-prover interactive proofs* (MIPs), using CMT as a base. Specifically, our protocol uses *two* provers, and provided that the provers do not communicate once the interrogation phase of the protocol begins, the verifier will detect arbitrary error or misbehavior on their part.

**Motivation.** We have two reasons to study the practical efficiency of MIPs. First, although the MIP model (stated above) is not always appropriate, it does correspond to some realistic scenarios: namely, those in which there is replication but in which we do not want to assume that at least one of the replicas functions correctly. (Indeed, if we are willing to assume that at least one of the replicas performs correctly, one can use Refereed games and related protocols [27, 28, 52], as noted in Section 2.) Examples include the growing use of efficient yet unreliable hardware, or a single cloud provider with a homogenous platform. In these cases, many nodes (and hence both "provers") can fail simultaneously. More broadly, the MIP model applies whenever one would use (Byzantine Fault-Tolerant) replication [4, 6, 29, 55]; however, unlike replication, the

MIP model tolerates correlated error.

Our second motivation stems from intense recent interest in non-interactive and succint arguments [17, 21, 22, 24, 32, 33, 37, 41, 43, 53, 58, 61], especially SNARKs (succinct non-interactive arguments of knowledge) without preprocessing. Bitansky and Chiesa [23] give a powerful technique for obtaining such SNARKs; using fully-homomorphic encryption (FHE) [38], they compile any complexity preserving MIP that also has a proof-of-knowledge (PoK) property into a complexity preserving SNARK (under a natural but non-standard assumption). This reduction (and other closely related ones [3, 35, 48, 49]) creates a potential avenue toward a concretely efficient SNARK: (1) develop a more practical compiler (in particular, one not based on FHE), and (2) develop a complexity preserving MIP with PoK that has inexpensive concrete costs (few provers, few queries, etc.). In this work, we focus on the second of these prongs, in the hope that future work will target the first. Of course, Bitansky and Chiesa also describe a complexity preserving MIP with PoK, but it has substantially higher quantitative costs, as discussed in Sections 2 and 4.5.3.

Summary of contributions. This paper contains both theoretical contributions and systems innovations. As our primary contribution, we describe a new MIP (with PoK) for the problem of non-deterministic circuit evaluation (§3–§4). Our MIP improves on prior work by several logarithmic factors (which reduces concrete costs substantially). Also, ours is the first complexity preserving MIP that has two provers and requires only one protocol repetition. Our protocol combines several new ideas (a new circuit arithmetization and a soundness analysis that avoids repetition, as outlined in Section 4), with existing ideas [12, 31, 40, 76].

We also describe a built system, called *Clover* (Section 5); given code written in a subset of C, Clover produces a verifier and provers that implement the protocol. This system allows us to perform a preliminary evaluation of the concrete efficiency properties of our MIP (§6). We find that Clover has better applicability than existing IP-based approaches (i.e., CMT) and better efficiency than existing argument-based approaches. However, Clover does not implement our MIP in full generality; specifically, Clover requires preprocessing (also known as setup costs for the verifier). The reason for the discrepancy is that our MIP avoids preprocessing only for regular circuits and Clover does not yet produce such circuits for general-purpose computations. (However, such circuits exist in principle: we show that the RAM-into-circuit techniques of Ben-Sasson et al. [15] can be modified to yield regular circuits.) Instead, Clover applies techniques [70, 71, 76] that produce *ir* regular circuits. Amortizing the resulting setup costs requires working over a *batch* of computation instances (the same computation, with different inputs). While not ideal, the restriction is not disastrous: this model is encountered in realistic applications of cloud computing (MapReduce, other data parallel computations, etc.).

## 2 Related work

Although there has been a great deal of classical systems work on verifiable computation, the majority of the literature either makes strong assumptions about the usage model (e.g., trusted hardware) or is special-purpose. See for example [61, 62, 70] for partial surveys of the area. Herein we focus on the recent body of work on proof-based verifiable computation, and the tools it draws on.

**GKR-CMT.** We described GKR-CMT [31, 40, 74, 76] in the introduction; our MIP extends several ideas from this protocol, achieving the following advantages. First, our protocol's costs depend logarithmically on the circuit's size, with no dependence on the depth. In GKR-CMT, by contrast, the verifier's costs grow logarithmically in the circuit's size and *linearly* in the depth, rendering the protocol inapplicable to deep circuits. Second, our protocol does not require circuits to be layered, leading to much smaller circuit representations. Third, our protocol requires fewer rounds, improving over GKR-CMT by a factor equal to the circuit depth. Fourth, our protocol handles non-deterministic circuits; this permits the use of efficient reductions from high-level programs to circuits [15, 61, 69, 76], a point we elaborate on below.

An argument system or MIP is *complexity preserving* if when applied to a computation that can be solved by a (non-deterministic) Random Access Machine that runs in time T(n) and space S(n), the verifier runs in time  $\tilde{O}(n)$ , and the provers run in total time  $\tilde{O}(T(n))$  and space  $\tilde{O}(S(n))$ . Here, n is the size of the input to the RAM, and the  $\tilde{O}$  notation hides factors polylogarithmic in T(n).

**Fast reductions from RAMs to circuits.** Ben-Sasson et al. [15], building on foundational work by, e.g., Gurevich and Shelah [44] and Robson [63], develop efficient methods for turning high-level programs (non-deterministic RAMs) into non-deterministic circuits. We adapt the techniques of [15] to construct circuits that compose with our MIP.

**Prior work on MIPs.** Babai et al. famously proved that MIP=NEXP [12]: the class of problems solvable by multi-prover interactive proofs with a polynomial-time verifier equals the class of languages solvable in non-deterministic exponential time. The protocol that they use in their proof inspired a number of our techniques. In both protocols, the verifier runs a sum-check protocol (§3.3) with one prover to determine whether some polynomial identity holds, and then asks another prover for help in performing the final check.

The actual polynomial identity that we use differs substantially from that of Babai et al. Moreover, their analysis assumes that provers are non-adaptive. While a protocol secure against non-adaptive provers can always be transformed into one secure against adaptive provers [14, 36], these transformations either use many provers or require repeating the protocol many times, leading to unacceptable concrete costs.

As stated in the introduction, Bitansky and Chiesa also do foundational work in MIPs, in particular giving the first (and, prior to our work, the only) complexity preserving MIP [23]. However, their MIP has substantially higher quantitative costs than ours, particularly for the provers. In our MIP, both provers run in  $O(|\mathcal{C}|\log^2|\mathcal{C}|)$  time for a given circuit  $\mathcal{C}$ . While [23] does not include a careful accounting of logarithmic factors, we estimate that even an optimized implementation of the MIP described in [23] requires total runtime at least  $\tilde{\Omega}(|\mathcal{C}|\log^6|\mathcal{C}|)$  for the provers, where  $\tilde{\Omega}$  hides factors of  $\log\log(|\mathcal{C}|)$ . (In Section 4, we briefly describe the reasons for these higher costs.) In addition, the MIP of [23] requires either hundreds of provers or else thousands of repetitions.<sup>2</sup>

One might wonder whether state of the art PCPs, together with parallel repetition, would lead to 2-prover complexity preserving MIPs. The answer is no, because the work required to construct the PCP does not preserve the prover's space complexity.

**Refereed games and refereed delegation of computation.** Recent work in the setting of *refereed games* [28, 52] and *refereed delegation of computation* (RDoC) [27] has provided verifiable computation protocols using two provers. These approaches assume that at least one of the provers is honest (the difference between them is that refereed games provide information-theoretic security, while RDoC protocols are secure against polynomial time provers). By contrast, MIPs do not assume that *either* of the provers is honest.

Canetti et al. [27] report on an RDoC implementation that, for some computations, achieves a slowdown for the prover of a factor of 8. While our MIPs cannot compete with this efficiency, the assumption of a correct and honest prover is not suitable for all cryptographic settings, as noted in the introduction. Moreover, it is MIPs' combination of information-theoretic security and security, even when all provers are dishonest, that allows them to be compiled into single-prover arguments [23, 49].

Argument systems without pre-processing. A standard technique for producing argument systems is to compile one from a short PCP [8, 9, 19, 20, 34], using collision-resistant hash functions [13, 51, 57]. Ben-Sasson et al. [15, 16] focus on reducing the concrete costs of short PCPs, toward a potentially practical solution. On the one hand, such an approach is appealing: there is no preprocessing for the verifier. On the other, although we do not know the concrete costs (existing work on this topic is still theoretical, though implementation efforts are reportedly underway), they are likely to be quite high: the short PCPs in [16] require many repetitions for soundness amplification.

**Argument systems with pre-processing.** Ishai et al. [46] obtain interactive argument systems, using *long* PCPs (short PCPs are complicated and often a bottleneck); however, the verifier requires pre-processing. Gennaro et al. (GGPR) [37], working in a similar model to [43, 53], use an ingenious encoding of circuits to

<sup>&</sup>lt;sup>2</sup>The reason for this tradeoff is that a generic reduction [14] from m to 2 provers yields a soundness error of 1 - 1/m, which in turn would require thousands of repetitions to drive the soundness error below, say, one part in one million.

construct efficient *non-interactive* argument systems that also avoid short PCPs. This work is the theoretical foundation of several of the built systems described below.

**SNARKs.** SNARKs are a kind of non-interactive argument. At a high level, there are four known techniques for constructing SNARKs. We break these down into two sub-classes:

Non-complexity preserving SNARKs. One can construct SNARKs by compiling them from short PCPs using extractable collision resistant hash functions [21, 32, 33, 41, 58]. However, this approach does not directly yield complexity preserving SNARKs because existing fast constructions of short PCPs do not preserve the space complexity of the prover. A second approach avoids short PCPs but requires a costly pre-processing stage for the verifier (see argument systems with pre-processing above) [24, 37, 43, 53].

Complexity preserving SNARKs. A third approach to constructing SNARKs is compiling them from MIPs of knowledge [23], as discussed in the introduction. If the original MIP is complexity preserving, the resulting SNARK is too (the resulting SNARK is designated-verifier). A fourth method, bootstrapping [22], uses an "inefficient" SNARK to produce one that is both publicly verifiable and complexity preserving. While bootstrapping yields remarkable asymptotic results, the approach is intrinsically indirect (roughly speaking, it requires running the inefficient SNARK on many sub-computations).

**Built systems.** CMT [31] implements the interactive proof of GKR [40]; Vu et al. incorporate refinements into a system called Allspice [76], and Thaler [74] accelerates the prover. In another line of work, Setty et al. [69–71] refine the argument protocol of Ishai et al. [46]; the best-performing in this line is called Zaatar.<sup>3</sup> Parno et al. realize the SNARKs of GGPR [37] in Pinocchio [61]. Ben-Sasson et al. [17, 18] borrow and optimize this SNARK and combine it with the RAM-to-circuit reductions described above [15]; we will refer to this work as BCTV. Pantry [26] builds on Zaatar [69] and Pinocchio; it compiles C to SNARKs (as does BCTV), handles programs that work with RAM (as does BCTV), and computations that work with external state (which BCTV does not handle). Finally, Buffet [77] incorporates the best features of Pantry and BCTV.

Each of these systems separates into a front-end (an algorithm that transforms a high-level program into a circuit) and a back-end (the "proof machinery"). The approaches built on GKR-CMT have the most efficient back-end when they apply, but their applicability is limited, as noted earlier. The back-ends of Zaatar and Pinocchio have the same rough efficiency as each other. However, Pinocchio provides non-interactivity and zero-knowledge (by definition), which Zaatar does not (neither does GKR-CMT). The remaining differences in the systems (Pinocchio, Pantry, BCTV, Buffet) concern the *front-ends*; this is because all of these systems are built on the same back-end, namely the protocol of Pinocchio (whose parameters are optimized by BCTV). Of these systems, Buffet's circuits are equal or better in efficiency than its predecessors (the differences approach two orders of magnitude for computations that interact with RAM), with almost no sacrifice of expressiveness relative to the most expressive system (which is BCTV).

#### 3 Preliminaries

# 3.1 Problem statement: multi-prover interactive proofs

We begin by defining multi-prover interactive proofs (MIPs). We primarily consider two-prover protocols and specialize the definition to this case.

**Definition 3.1.** A two-prover interactive proof protocol for a language  $\mathcal{L} \subseteq \{0,1\}^*$  involves three parties: a probabilistic *verifier* and two *provers*. The verifier exchanges a sequence of messages with each prover; each prover's message is a function of the input message and the messages that it has seen so far. At the end of the interaction, the verifier outputs 0 or 1.  $(\mathcal{V}, \mathcal{P}_1, \mathcal{P}_2)$  form a two-prover interactive protocol for  $\mathcal{L}$  if the following two conditions are satisfied, where the probabilities below are taken over  $\mathcal{V}$ 's internal randomness.

<sup>&</sup>lt;sup>3</sup>The argument protocol underlying [69–71] can also be modified to yield a two-prover MIP. The major advantage of our MIP over this alternative is that the latter inherently requires an expensive pre-processing phase for the verifier that we can avoid.

- Completeness: For any input  $x \in \mathcal{L}$ , the verifier  $\mathcal{V}$  outputs 1 with probability 1 when interacting with provers  $\mathcal{P}_1$  and  $\mathcal{P}_2$ .

- Soundness: For all  $x \notin \mathcal{L}$  and all provers  $\mathcal{P}_1^*$ ,  $\mathcal{P}_2^*$ , the probability that  $\mathcal{V}$  outputs 1 on input x when interacting with  $\mathcal{P}_1^*$  and  $\mathcal{P}_2^*$  is at most  $\epsilon$ , for some  $\epsilon < 1/3$ . The parameter  $\epsilon$  is called the soundness error of the protocol.

For simplicity, we will often refer to two-prover interactive proofs simply as MIPs. We also consider functions  $f: \{0,1\}^* \to \mathcal{R}$ , for a finite range  $\mathcal{R}$ , rather than languages. An *MIP for f* is an MIP for the language  $\{(x,f(x))\}$ . We will sometimes consider MIPs for functions f with k>1 outputs; to apply the definition above to such functions, we interpret a k-tuple of outputs over range  $\mathcal{R}$  as a single output over the larger range  $\mathcal{R}^k$ . Clearly an MIP for f is interesting only if it is cheaper for  $\mathcal{V}$  than computing f unaided. We remark that the requirement of  $\epsilon < 1/3$  is chosen for consistency with the MIP literature (see e.g. [7, Chapter 8]); in our implementation,  $\epsilon$  will be less than  $2^{-23}$ . Finally, a prover may in practice not be a single machine (e.g., a prover may be implemented on a compute cluster).

**Cost model.** Whenever we work over a finite field  $\mathbb{F}$ , we assume that a single field operation can be computed in a single machine operation.

#### 3.2 Other definitions

**Circuits and transcripts.** A *arithmetic circuit*  $\mathcal{C}$  is defined over a field  $\mathbb{F}$  and has input gates, output gates, intermediate gates, and directed wires between them. Each gate computes addition or multiplication over  $\mathbb{F}$ .  $\mathcal{C}$  can be *non-deterministic* (i.e., it can take auxiliary inputs). We will describe the gates in  $\mathcal{C}$  as having *values*: the value of an addition (multiplication) gate is set to be the sum (product) of its in-neighbors. We refer to the number of gates in  $\mathcal{C}$  as its *size*, and denote this quantity by  $|\mathcal{C}|$ . A fundamental notion used by our MIP is that of a *correct transcript* for a circuit  $\mathcal{C}$  given input  $x \in \{0, 1\}^n$  and output(s)  $y \in \mathcal{R}$ .

**Definition 3.2.** A *transcript* for an arithmetic circuit  $\mathcal{C}$  is an assignment of values to the circuit gates; a *correct* transcript for  $\{\mathcal{C}, x, y\}$  is a transcript in which the values assigned to the input gates are those of x, the intermediate values correspond to the correct operation of each gate in  $\mathcal{C}$ , and the values assigned to the output gates are y. Given a triple  $\{\mathcal{C}, x, y\}$ , we refer to the problem of determining whether there is a correct transcript for  $\{\mathcal{C}, x, y\}$  as the non-deterministic circuit evaluation problem.

**Low-degree extensions.** Let  $g: \{0,1\}^m \to \mathbb{F}$  be any function. We say that a polynomial  $\tilde{g}: \mathbb{F}^m \to \mathbb{F}$  is a *polynomial extension* of g if  $\tilde{g}$  agrees with g everywhere that g is defined; i.e., if  $\tilde{g}(x) = g(x)$  for all  $x \in \{0,1\}^m$ . Notice that  $\tilde{g}$  is defined over  $\mathbb{F}^m$  whereas g is defined only over  $\{0,1\}^m$ . We will often work with *multilinear extensions*, meaning that  $\tilde{g}$  has degree at most one in each of its m variables.

# 3.3 Technical background

Schwartz-Zippel lemma. We will often make use of the following basic property of polynomials.

**Lemma 3.1** ([79]). Let  $\mathbb{F}$  be any field, and let  $f: \mathbb{F}^m \to \mathbb{F}$  be a nonzero polynomial of total degree d. Then on any finite set  $S \subseteq \mathbb{F}$ ,  $\Pr_{x \leftarrow S^m}[f(x) = 0] \le d/|S|$ . In particular, any two distinct polynomials of total degree d can agree on at most d/|S| fraction of points in  $S^m$ .

**Sum-check protocol.** Our MIP makes essential use of two standard tools from the literature on IPs and MIPs: sum-check protocols [54, 72] (see also [7, §8.3.1] and [64, §3.2.3]), and low-degree tests [10, 12, 60]. We describe sum-check protocols here and low-degree tests in context (§4.4).

Sum-check protocols are interactive; there is a verifier  $\mathcal{V}_{SC}$  and a prover  $\mathcal{P}_{SC}$ , and  $\mathcal{V}_{SC}$  begins with an m-variate polynomial  $g: \mathbb{F}^m \to \mathbb{F}$  as well as with a claim K (which is often originated by  $\mathcal{P}_{SC}$ ). The protocol allows  $\mathcal{P}_{SC}$  to prove to  $\mathcal{V}_{SC}$  that K equals the sum of the evaluations of g over all  $2^m$  Boolean inputs, namely:

$K = \sum_{u_1 \in \{0,1\}} \sum_{u_2 \in \{0,1\}} \cdots \sum_{u_m \in \{0,1\}} g(u_1,\ldots,u_m)$ . If the true sum is K, then a correct  $\mathcal{P}_{SC}$  can convince  $\mathcal{V}_{SC}$ ; otherwise,  $\mathcal{V}_{SC}$  is highly unlikely to be convinced.

The power of this protocol is that  $\mathcal{V}_{SC}$  has to do far less work than the apparently exponential work that is required to compute the sum locally.  $\mathcal{V}_{SC}$ 's main burden is to perform a *single* evaluation of  $g(r_1, \ldots, r_m)$ , for a point  $(r_1, \ldots, r_m)$  chosen uniformly at random from  $\mathbb{F}^m$ . Moreover, the protocol requires only 2m-1 messages to be exchanged over m rounds, with each message consisting of a small number of field elements.

#### 3.4 Framework

Here we introduce the framework around which our MIP is designed. This high-level description also loosely applies to many of the recently implemented systems for proof-based verifiable computation [17, 18, 26, 31, 61, 69–71, 75, 76]; the primary difference is our use of two provers.

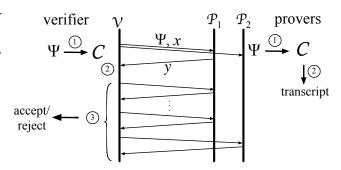

Our MIP has three steps, depicted in Figure 1. In Step 1,  $\mathcal{V}$  starts with a specification  $\Psi$  of a Random Access Machine computing a function f, and sends  $\Psi$  to the provers. In practice,  $\Psi$  will typically be a program expressed in a high-level language (in our prototype implementation, a subset of C). The provers and the verifier compile  $\Psi$  into a (non-deterministic) arithmetic circuit  $\mathcal{C}$ .

In Step 2,  $\mathcal{P}_1$  and  $\mathcal{P}_2$  execute the computation  $\Psi$  on input x, and  $\mathcal{P}_1$  returns output y. In performing this step, the provers are expected to obtain a correct transcript for  $\{\mathcal{C}, x, y\}$ . Notice that if the claimed output is incorrect—that is, if  $y \neq f(x)$ —then a correct transcript for  $\{\mathcal{C}, x, y\}$  simply does not exist: in any transcript that represents the inputs and the computation of each gate correctly, the output wires would not be y.

Figure 1—Our high-level framework. In step ①, a verifier  $\mathcal V$  and two provers  $\mathcal P_1, \mathcal P_2$  compile a computation  $\Psi$  to an arithmetic circuit,  $\mathcal C$ . In step ②,  $\mathcal V$  requests evaluation of  $\Psi$  on input x;  $\mathcal P_1$  returns purported output y, and both provers obtain a transcript for the execution of  $\mathcal C$  on x. In step ③,  $\mathcal V$  queries  $\mathcal P_1$  in rounds and submits a final query to  $\mathcal P_2$ ; if  $y{\neq}\Psi(x)$ , then the responses from non-colluding  $\mathcal P_1, \mathcal P_2$  do not, except with very low probability, convince  $\mathcal V$  that  $\Psi$  was executed correctly.

In Step 3,  $\mathcal{P}_1$  and  $\mathcal{P}_2$  want to prove to  $\mathcal{V}$  that a correct transcript for  $\{\mathcal{C}, x, y\}$  exists. Of course, there is a simple proof that a correct transcript exists: the transcript itself. Unfortunately,  $\mathcal{V}$  can check this transcript for correctness only by examining all of it, which would be as much work as having executed  $\Psi$  in the first place. Instead,  $\mathcal{P}_1$  and  $\mathcal{P}_2$  use low-degree extensions to *encode* the transcript (as a much longer string) in such a way that a transcript's correctness (or lack thereof) can be determined by inspecting only a few of the locations in the encoded version; this "inspection" will take the form of queries from the verifier to the provers.

Herein, our primary focus will be on Step 3, i.e., on giving a novel two-prover protocol for (non-deterministic) circuit evaluation.

#### 4 An MIP for non-deterministic circuit evaluation

#### 4.1 Overview of the ideas

Given an arithmetic circuit C, input x, and claimed outputs y, our protocol *encodes* a purported transcript W (Defn. 3.2) as a polynomial  $\widetilde{G}_{x,y}$  in such a way that  $\widetilde{G}_{x,y}$  evaluates to 0 on a particular subset of its domain if and only if W is correct for  $\{C, x, y\}$ . Omitting many details, our MIP then uses a sum-check protocol (§3.3), run with  $\mathcal{P}_1$ , to check that  $\widetilde{G}_{x,y}$  in fact evaluates to 0 all over the subset in question. At the end of this sum-check protocol,  $\mathcal{P}_1$  is forced to make a claim about  $\widetilde{W}(w_4)$  for a point  $w_4$  chosen at random by the

<sup>&</sup>lt;sup>4</sup>If  $\mathcal C$  satisfies certain regularity conditions (made formal in §4.5.3), our protocol will allow  $\mathcal V$  to avoid materializing the full circuit  $\mathcal C$  during this step, enabling  $\mathcal V$  to run in time sub-linear in  $|\mathcal C|$ .

verifier, where  $\widetilde{W}$  is the multilinear extension of W. Even checking this claim is too expensive for V, so Voutsources it to  $\mathcal{P}_2$ , using a low-degree test (§4.4).

In many respects, our approach can be seen as a careful adaptation of the ideas underlying the GKR protocol [40] to the multi-prover setting. While GKR verifies the correctness of a transcript for  $\{C, x, y\}$  layer by layer, with a a different instance of the sum-check protocol required for each layer of  $\mathcal{C}$ , our MIP verifies the whole computation in one shot, using a single invocation of the sum-check protocol.

While this "sum-check protocol + low-degree test" paradigm for constructing two-prover MIPs is not new [12], several aspects of our protocol require new ideas. One is the choice of the polynomial  $G_{x,y}$ , which is meant to vanish at all Boolean inputs if and only  $\mathcal{P}_1$ 's answers are consistent with a correct transcript W. The difficulty in defining a suitable polynomial is that, for each output gate a,  $G_{x,y}$  must ensure both that W(a)is consistent with claimed output y and that W(a) is correct, given the values of a's in-neighbors. Though our definition of  $G_{x,y}$  may appear obvious in hindsight, it carefully exploits cancellation to achieve this property (Lemma 4.1 has details).

To the best of our knowledge, some aspects of our soundness analysis are also novel. In particular, in standard analyses of low-degree tests, the assumption is that a prover is a function only of the queries issued by the verifier within the test. However, recall that in our context  $\mathcal{V}$  uses a low-degree test to check  $\mathcal{P}_1$ 's claim about  $W(w_4)$ , and  $\mathcal{P}_1$ 's claim can depend not just on  $w_4$ , but instead on the entire sequence of messages exchanged with V over the course of the protocol. This makes it non-trivial to apply existing analyses of low-degree tests to our setting, without resorting to expensive generic reductions or the use of additional provers to force  $\mathcal{P}_1$  to be non-adaptive.

## 4.2 Details of the MIP

We imagine a single input vector x and a claimed output y (which may be a vector), for a given computation  $\Psi$ , compiled to an arithmetic circuit  $\mathcal C$  of fan-in two. We stress that  $\mathcal C$  may be non-deterministic. Each entry in x, y, and all intermediate values, are contained in a finite field  $\mathbb{F} = \mathbb{F}_p$  (the integers mod a large prime p). In our built system, p will always be 300 or 400 bits (§5).

Denote the number of gates in  $\mathcal{C}$ , or its size, as  $|\mathcal{C}|$ , and take  $s = \lceil \log |\mathcal{C}| \rceil$ . Now, assume we have fixed an ordering of the gates. Associate with every gate in C a label of s bits, in the natural way: the zero'th gate gets the label 0, the next gate gets the label 1, etc. We will move back and forth between representing a label as an integer (for example, 0, 1, etc.) and as a bit vector:  $(0,0,\ldots,0)$ ,  $(0,0,\ldots,1)$ , etc.

Now, we will model a transcript of C as a list of every gate in C (including the input gates) together with a purported value for that gate. It is convenient to represent that list as a function  $W: \{0,1\}^s \to \mathbb{F}$  that maps a gate's label to the gate's purported value; it is also convenient to imagine that  $\mathcal{P}_1$  is holding such a function W. At this point, V wants to know whether W is a correct transcript (Defn. 3.2).

How can V check W for correctness? If V asks  $P_1$  only for the values of W for the input and output gates,  $\mathcal{V}$  has no way of knowing if the answers are correct. If  $\mathcal{V}$  asks  $\mathcal{P}_1$  for all of W, then  $\mathcal{V}$  does not save work. Instead,  $\mathcal{V}$  translates the claim that W is correct into an equivalent algebraic claim that is amenable to probabilistic checking. This algebraic claim concerns the properties of a carefully constructed polynomial.

To present this polynomial, we must introduce some functions that capture C's structure: add, mult, and

io. Let add:

$$\{0,1\}^{3s} \to \{0,1\}$$

denote a function that takes as input three gate labels:

$$\operatorname{add}(a,b,c) = \begin{cases} 1 & \text{if gate $a$ adds the outputs of gates $b$ and $c$} \\ 0 & \text{otherwise} \end{cases}$$

Likewise, mult:  $\{0,1\}^{3s} \to \{0,1\}$  returns 1 when gate a is the product of gates b and c, and 0 otherwise. These two functions, add $(\cdot, \cdot, \cdot)$  and mult $(\cdot, \cdot, \cdot)$ , are used in GKR [40], and are called *wiring predicates* by CMT [31].<sup>5</sup> We add a third wiring predicate: let io:  $\{0,1\}^{3s} \to \{0,1\}$  denote a function that takes as input

<sup>&</sup>lt;sup>5</sup>A difference is that in those works, a circuit must be layered, and there are separate wiring predicates for each layer.

gate labels (a, b, c) and returns 1 when gate a is a (non-auxiliary) input gate or one of the output gates, and b and c are the in-neighbors of a (input gates have in-neighbors b = c = 0); otherwise, io returns 0.

Notice that add, mult, and io are independent of the inputs and purported outputs. Our last function, however, depends on the inputs and purported outputs. Define  $I_{x,y}$ :  $\{0,1\}^s \to \mathbb{F}$  such that  $I_{x,y}(a) = x_a$  if a is the label of an input gate,  $I_{x,y}(a) = y_a$  if a is the label of an output gate, and  $I_{x,y}(a) = 0$  otherwise.

We now use add, mult, io, and  $I_{x,y}$  to write a function that captures whether a transcript W is correct for  $\{C, x, y\}$ .

**Lemma 4.1.** For  $G_{x,y}(a,b,c)$  defined as below,  $G_{x,y}(a,b,c) = 0$  for all  $(a,b,c) \in \{0,1\}^{3s}$  if and only if W is a correct transcript for  $\{C,x,y\}$ :

$$G_{x,y}(a,b,c) = io(a,b,c) \cdot (I_{x,y}(a) - W(a)) + add(a,b,c) \cdot (W(a) - (W(b) + W(c))) + mult(a,b,c) \cdot (W(a) - W(b) \cdot W(c)).$$

*Proof.* If W is not a correct transcript, there are five cases:

- 1. Suppose  $a \in \{0, 1\}^s$  is the label of an input gate. If  $W(a) \neq x_a$ , then  $G_{x,y}(a, 0, 0) = I_{x,y}(a) W(a) = x_a W(a) \neq 0$ .

- 2. Suppose  $a \in \{0,1\}^s$  is the label of a non-output addition gate with in-neighbors b and c. If  $W(a) \neq W(b) + W(c)$ , then  $G_{x,y}(a,b,c) = W(a) (W(b) + W(c)) \neq 0$ .

- 3. Suppose  $a \in \{0,1\}^s$  is the label of a non-output multiplication gate with in-neighbors b and c. If  $W(a) \neq W(b) \cdot W(c)$ , then  $G_{x,v}(a,b,c) = W(a) (W(b) \cdot W(c)) \neq 0$ .

- 4. Suppose  $a \in \{0, 1\}^s$  is the label of an output addition gate with in-neighbors b and c. If  $y_a \neq W(b) + W(c)$ , then  $G_{x,y}(a,b,c) = I_{x,y}(a) W(a) + (W(a) (W(b) + W(c))) = y_a (W(b) + W(c)) \neq 0$ .

- 5. Suppose  $a \in \{0,1\}^s$  is the label of an output multiplication gate with in-neighbors b and c. If  $y_a \neq W(b) \cdot W(c)$ , then  $G_{x,y}(a,b,c) = I_{x,y}(a) W(a) + (W(a) (W(b) \cdot W(c))) = y_a (W(b) \cdot W(c)) \neq 0$ . On the other hand, if W is a correct transcript then it is immediate from the definition of  $G_{x,y}$  that  $G_{x,y}(a,b,c) = 0$  for all  $(a,b,c) \in \{0,1\}^{3s}$ .

The lemma implies that in order for  $\mathcal{V}$  to check that W is a correct transcript, it suffices for  $\mathcal{V}$  to check that  $G_{x,y}$  vanishes on all inputs in the Boolean hypercube. However, this check must be "outsourced" because  $\mathcal{V}$  cannot handle all of  $G_{x,y}$ . We briefly consider a straw man approach to such outsourcing: use a sum-check protocol (§3.3) to check whether  $0 \stackrel{?}{=} \sum_{a,b,c \in \{0,1\}^s} G_{x,y}(a,b,c)$ . This is a straw man because, first, the sum-check protocol works with a polynomial (and  $G_{x,y}$  is not a polynomial), and, second, a sum of zero does not actually imply that  $G_{x,y}$  vanishes on the desired subspace (the evaluations of  $G_{x,y}(a,b,c)$  could "cancel out").

As a next step, consider the following polynomial extension  $\widetilde{G}_{x,y} \colon \mathbb{F}^{3s} \to \mathbb{F}$  of  $G_{x,y}$ :

$$\widetilde{G}_{x,y}(u_1, u_2, u_3) = \widetilde{\text{io}}(u_1, u_2, u_3) \cdot (\widetilde{I}_{x,y}(u_1) - \widetilde{W}(u_1))

+ \widetilde{\text{add}}(u_1, u_2, u_3) \cdot (\widetilde{W}(u_1) - (\widetilde{W}(u_2) + \widetilde{W}(u_3)))

+ \widetilde{\text{mult}}(u_1, u_2, u_3) \cdot (\widetilde{W}(u_1) - \widetilde{W}(u_2) \cdot \widetilde{W}(u_3)).$$

(1)

Here, io,  $I_{x,y}$ ,  $\widetilde{W}$ , add, and mult respectively denote polynomial extensions of io,  $I_{x,y}$ , W, add, and mult. For efficiency, all of the polynomial extensions appearing in Equation (1) must be low-degree. We will always use the *multilinear* extension  $\widetilde{W}$  of W, and we will always use multilinear or carefully chosen *cubic* extensions io, add and mult of io, add, and mult (these choices are essential for practical efficiency, as discussed in Section 4.5.2). At this point, we have a polynomial (in 3s variables) over  $\mathbb{F}$ , and we want to use the sum-check protocol directly to prove to  $\mathcal{V}$  that  $0 = \sum_{a,b,c \in \{0,1\}^s} \widetilde{G}_{x,y}(a,b,c)$ . However, as noted above, cancellations mean that a sum of zero does not guarantee that  $\widetilde{G}_{x,y}(a,b,c)$  evaluates to 0 over all  $(a,b,c) \in \{0,1\}^{3s}$ , which was the algebraic property that we were trying to establish. This brings us to the actual protocol.

We consider a polynomial  $F_{x,y}$  whose *coefficients* are given by the evaluations of  $G_{x,y}$  on  $\{0,1\}^{3s}$ .

Specifically, define

$$F_{x,y}(t) = \sum_{u \in \{0,1\}^{3s}} \widetilde{G}_{x,y}(u) \cdot t^{u}.$$

(2)

Here, the bit string  $u \in \{0,1\}^{3s}$  in the exponent denotes the integer  $\sum_{i=0}^{3s-1} u_i \cdot 2^i$  (i.e., the integer whose binary representation is u). Notice that  $F_{x,y}$  is the zero polynomial if and only if  $\widetilde{G}_{x,y}$  vanishes on  $\{0,1\}^{3s}$  (and hence if and only if  $\widetilde{G}_{x,y}$  encodes a correct transcript, and hence if and only if y is the correct output). But by the Schwartz-Zippel lemma, any non-zero low-degree polynomial has few roots, so if  $\mathcal{V}$  picks a random point  $q \in \mathbb{F}$  and determines that  $F_{x,y}(q) = 0$ , it is safe for  $\mathcal{V}$  to believe that  $F_{x,y}$  is the zero polynomial and hence that  $\widetilde{G}_{x,y}$  vanishes on  $\{0,1\}^{3s}$  as claimed by  $\mathcal{P}_1$  (our soundness analysis is made formal in Appendix A).

Thus, in our MIP,  $\mathcal{V}$  chooses q uniformly at random from  $\mathbb{F}$ , and is convinced that W is a correct transcript for  $(\mathcal{C}, x, y)$  as long as  $F_{x,y}(q) = 0$ . As explained below,  $\mathcal{V}$  will outsource the computation of  $F_{x,y}(q)$  by writing  $F_{x,y}(q)$  in a form that is amenable to checking via the sum-check protocol (this approach was first proposed by Babai et al. in the original MIP=NEXP proof [12]).

To this end, notice that for any  $q \in \mathbb{F}$  and  $u \in \{0,1\}^{3s}$ , we can write  $q^u$  as a multilinear polynomial  $g_q$  in the coordinates of u as follows. Define  $q^{(i)} = q^{2^i}$ . Then it holds that  $q^u = \prod_{i=0}^{3s-1} q^{(i)^{u_i}} = \prod_{i=0}^{3s-1} \left(1 + (q^{(i)} - 1)u_i\right) := g_q(u)$ . Defining the polynomial  $h_q$  as  $\widetilde{G}_{x,y} \cdot g_q$ , we obtain the following identity:

$$F_{x,y}(q) = \sum_{u \in \{0,1\}^{3s}} \widetilde{G}_{x,y}(u) \cdot g_q(u) = \sum_{u \in \{0,1\}^{3s}} h_q(u).$$

(3)

Notice that  $h_q$  is a low-degree polynomial in the coordinates of u ( $h_q$  has degree at most 3 in each variable, if the multilinear extensions of add, mult and io are used in the definition of  $\widetilde{G}_{x,y}$ ). We now describe how  $\mathcal{V}$  outsources computation of  $\sum_{u \in \{0,1\}^{3s}} h_q(u)$  to  $\mathcal{P}_1$  using a sum-check protocol.

## 4.3 Interaction with the first prover

The full protocol is given in Figure 5 (in Appendix E) and proceeds as follows.  $\mathcal{V}$  picks a random  $q \in \mathbb{F}$  (see above for motivation) and sends it to the prover  $\mathcal{P}_1$ . The two parties then run the sum-check protocol over the polynomial  $h_q$  to prove to  $\mathcal{V}$  that  $0 = \sum_{u \in \{0,1\}^{3s}} h_q(u) = F_{x,y}(q)$ .

Now, the final check in the sum-check protocol requires  $\mathcal{V}$  to evaluate  $h_q(\cdot)$  at a randomly selected point  $(w_1, w_2, w_3)$  (see Section 3.3). If  $\mathcal{V}$  could do this efficiently, we would be done. However, in our setting  $\mathcal{V}$  cannot evaluate  $h_q(w_1, w_2, w_3)$ : doing so would require evaluating  $\widetilde{G}_{x,y}(w_1, w_2, w_3)$  and hence (by the definition of  $\widetilde{G}_{x,y}$ ) evaluating  $\widetilde{W}(w_1)$ ,  $\widetilde{W}(w_2)$ , and  $\widetilde{W}(w_3)$ , which in turn would require constructing  $\widetilde{W}(\cdot)$ , which would be at least as much work as handling the unencoded transcript W.

Instead,  $\mathcal{V}$  asks  $\mathcal{P}_1$  for help:  $\mathcal{P}_1$  gives  $\mathcal{V}$  three field elements that are purported to be  $\widetilde{W}(w_1)$ ,  $\widetilde{W}(w_2)$ , and  $\widetilde{W}(w_3)$ . Then, using a now-standard technique (see, e.g. [40]) the protocol reduces the uncertainty surrounding the correctness of these values to a claim:  $v_4 \stackrel{?}{=} \widetilde{W}(w_4)$ . This reduction is the content of lines 7–21 in Figure 5, and occurs as follows. Let  $\ell(t)$  be the degree-two curve passing through the points  $w_1, w_2$ , and  $w_3$  defined via  $\ell(0) = w_1, \ell(1) = w_2$ , and  $\ell(2) = w_3$ .  $\mathcal{V}$  asks  $\mathcal{P}_1$  to send her a degree 2s univariate polynomial  $H^*$  claimed to equal  $\widetilde{W} \circ \ell$ , i.e.,  $\widetilde{W}$  restricted to the curve  $\ell$ .  $\mathcal{V}$  checks that  $H^*(0), H^*(1)$ , and  $H^*(2)$  equal  $v_1, v_2$ , and  $v_3$  respectively.  $\mathcal{V}$  then picks a random point  $\tau \in \mathbb{F}$ , chooses  $w_4$  as  $\ell(\tau)$ , evaluates  $H(\tau)$ , and treats  $H(\tau)$  as an implicit claim by  $\mathcal{P}_1$  about the value of  $\widetilde{W}(w_4)$ . The Schwartz-Zippel lemma implies that if  $H^* \neq \widetilde{W} \circ \ell$ , then  $H^*(\tau) \neq \widetilde{W}(\ell(\tau))$  with probability  $1 - 2s/\mathbb{F}$  over  $\tau \stackrel{R}{\leftarrow} \mathbb{F}$ . Hence,  $\mathcal{V}$  chooses  $\tau$  at random from  $\mathbb{F}$ , and is convinced that  $H^* = \widetilde{W} \circ \ell$  (and hence that  $v_i = \widetilde{W}(w_i)$  for  $i \in \{1, 2, 3\}$ ) as long as  $H^*(\tau) = \widetilde{W}(w_4)$  (again, our formal proof of soundness appears in Appendix A).

At this point, the protocol has provided the following guarantee to V, which we state loosely. V should believe that  $0 = F_{x,y}(q)$ —and hence that a correct transcript exists and hence that the computation was done correctly—if and only if V can establish that  $v_4 = \widetilde{W}(w_4)$  for some low-degree polynomial  $\widetilde{W}$ . But how can

$\mathcal{V}$  check this? As noted, it would be too expensive for  $\mathcal{V}$  to evaluate  $\widetilde{W}$ . For this purpose,  $\mathcal{V}$  turns to the second prover.

## 4.4 Interaction with the second prover

To validate  $\mathcal{P}_1$ 's claim that  $v_4 = \widetilde{W}(w_4)$ ,  $\mathcal{V}$  engages the second prover,  $\mathcal{P}_2$ , using a low-degree test [10, 60] (see Figure 5, lines 23–24). We use the point vs. plane low-degree test, as analyzed by Moshkovitz and Raz [60]. This test works by asking  $\mathcal{P}_2$  to send a very small "excerpt" of the encoded transcript  $\widetilde{W}$ ; to get this transcript,  $\mathcal{P}_2$  must execute the computation, just as  $\mathcal{P}_1$  does. The "excerpt" is a low-degree polynomial claimed to equal  $\widetilde{W}$  restricted to a low-dimensional subspace. In the test we use, this subspace is a plane that passes through  $w_4$ , and  $\mathcal{V}$  conceals which point in the subspace is  $w_4$ . Because  $\mathcal{V}$  obtains (a description of)  $\widetilde{W}$  over the entire subspace,  $\mathcal{V}$  extracts an implicit claim by  $\mathcal{P}_2$  about the value of  $\widetilde{W}(w_4)$ . At this point,  $\mathcal{V}$  rejects if there is a discrepancy in the two provers' claims about  $\widetilde{W}(w_4)$  (see Figure 5, line 24).

In more detail, in the point vs. plane test, V sends  $\mathcal{P}_2$  a random plane Q (i.e., a two-dimensional affine subspace of  $\mathbb{F}^s$ ) through the point  $w_4$ , parameterized in a way that reveals no information about the point  $w_4$  to  $\mathcal{P}_2$ , other than that  $w_4$  lies somewhere on Q.  $\mathcal{P}_2$  responds with a bivariate polynomial  $H_Q^*$  of degree s in each variable claimed to equal  $\widetilde{W} \circ Q$ . Let  $(t_1, t_2)$  be the point such that  $Q(t_1, t_2) = w_4$ . V considers  $H_Q^*(t_1, t_2)$  to be  $\mathcal{P}_2$ 's claim about the value of  $\widetilde{W}(w_4)$ .

Moshkovitz and Raz [60] have analyzed the point vs. plane test to be sound for reasonable field sizes (see Lemma A.1 in Appendix A for details). Note that Moshkovitz and Raz state explicitly that they made no attempt to optimize the constants appearing in their analysis, and even small improvements in the constants would yield substantial improvements to the soundness guarantee for our protocol. This would allow us to work over smaller fields; the current implementation works over a very large field so as to achieve low soundness error, and the field size is a substantial contributor to the costs of our implementation.

#### 4.5 Guarantees and costs

## 4.5.1 Correctness

Our MIP guarantees completeness and soundness, as defined in Section 3.1. An upper-bound on our MIP's soundness error,  $\epsilon$ , assuming  $|\mathbb{F}| > |\mathcal{C}|^8$ , is  $(2^9 \cdot \log |\mathcal{C}|)/|\mathbb{F}|^{1/8}$ . Thus, for a field size of 300 bits,  $\epsilon < 2^{-23}$  for any circuit  $\mathcal{C}$  with fewer than  $2^{40}$  gates, and for a field size of 400 bits,  $\epsilon < 2^{-35}$ . We establish this formally in Appendix A.

## 4.5.2 Overview of Costs

We now give a brief overview of the costs of our MIP, before formalizing them in Theorem 4.1.

$\mathcal{V}$ 's costs. The principal bottleneck in  $\mathcal{V}$ 's running time is that  $\mathcal{V}$ 's final check in the sum-check protocol requires evaluating the low-degree extensions add and mult at  $(w_1, w_2, w_3) \in \mathbb{F}^{3s}$ . We take two approaches. The first approach requires pre-processing but applies to arbitrary circuits; we use this approach in our prototype implementation (cf. §5). The second uses carefully generated circuits for which the verifier can evaluate add and mult in polylogarithmic time, and hence avoid a pre-processing phase. We have not yet implemented this circuit generator, leaving it to near-term future work. In more detail:

Approach 1. Our implemented compiler from high-level programs to circuits uses the multilinear extensions add and mult. While this leads to  $O(|\mathcal{C}|)$  pre-processing time for  $\mathcal{V}$ , the costs can be amortized (§5 gives details).

Approach 2. We adapt work of Ben-Sasson et al. [15] to turn arbitrary RAMs into small circuits with repeated structure. There are *cubic* extensions of the wiring predicate of these circuits that V can evaluate at any point in polylogarithmic time (and  $P_1$ 's costs can be controlled when using these extensions, using techniques of Thaler [74]; see below). Using this approach, V does not need to materialize the circuit, and thus does not

incur the cost of compiling the high-level program into the circuit. In this approach, the verifier processes the input in O(n) time, and the rest of the protocol requires polylogarithmic time in *total*.

$\mathcal{P}_1$ 's and  $\mathcal{P}_2$ 's costs. In both Approach 1 and Approach 2,  $\mathcal{P}_1$  in each round has to compute a univariate polynomial, defined as a sum of up to  $|\mathcal{C}|^3$  other univariate polynomials. However, techniques of CMT [31] and Thaler [74] show that under both approaches, each gate in  $\mathcal{C}$  contributes to O(1) terms in the sum, allowing  $\mathcal{P}_1$  to run in  $O(|\mathcal{C}|\log|\mathcal{C}|)$  time.  $\mathcal{P}_2$ 's computation is identical in both approaches: the point-vs-plane test requires  $\mathcal{P}_2$  to evaluate  $\widetilde{W}(\cdot)$  at  $(\log|\mathcal{C}|+1)^2$  points. This can be done with  $4|\mathcal{C}|$  field multiplications per point using a memoization idea from [76, §5.1]. In settings (such as our built system) in which  $\mathcal{V}$  wants to evaluate a circuit  $\mathcal{C}$  on many inputs, both  $\mathcal{P}_1$  and  $\mathcal{P}_2$  can reuse some work across instances. In §5, we describe such reusable work as *setup costs* for  $\mathcal{P}_1$  and  $\mathcal{P}_2$ .

*Remark*. Thaler [74] also shows how to reduce the prover's total work in the GKR-CMT protocol to be proportional to  $|\mathcal{C}|$  rather than  $|\mathcal{C}| \log |\mathcal{C}|$  for a large class of wiring patterns, and demonstrates experimentally that these techniques can reduce the prover's runtime by two orders of magnitude relative to the original CMT implementation that appeared in [31]. These techniques apply equally well to the first prover in our MIP protocol. However, we have not yet incorporated them into our prototype implementation (indeed, our prototype currently uses circuits that do not satisfy the conditions required by the optimizations of [74]).

The next subsection formalizes the costs and guarantees of Approach 2.

#### 4.5.3 A complexity preserving MIP

**Theorem 4.1.** There is a two-prover MIP protocol satisfying the following properties. In order to check that a T(n)-time S(n)-space Random-Access Machine M non-deterministically accepts an input x of length n, the MIP verifier runs in time  $O(n \cdot \operatorname{polylog}(T(n)))$ , and both MIP provers run in time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$  if given an (input, witness) pair (x ; w) for M. Moreover, each MIP prover can be computed "gate-by-gate" as a circuit by an evaluator algorithm in time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$ .

To clarify, Bitansky and Chiesa [23] obtained an identical result to Theorem 4.1 up to factors hidden by the polylog(T(n)) terms, using very different techniques from our own (their MIP uses  $m = \Theta(\log S(n)/\log\log(S(n)))$  many provers, but one can obtain a two-prover MIP from their construction using a generic reduction that "only" blows up the costs by logarithmic factors). We state Theorem 4.1 not for its novelty, but because it formalizes the costs and properties of our MIP.

We note, however, that our MIP has substantially improved quantitative costs compared to [23]. When instantiated on a particular circuit  $\mathcal{C}$ , both of our provers run in time  $O(|\mathcal{C}|\log^2|\mathcal{C}|)$ , whereas the provers in the MIP of [23] appear to require total time at least  $\tilde{\Omega}(|\mathcal{C}|\log^6|\mathcal{C}|)$ , even before invoking the reduction to two provers. There are two main reasons for their higher costs. First, their protocol requires running  $\Omega(\log |\mathcal{C}|/\log \log |\mathcal{C}|)$  low-degree tests, compared to our single low-degree test. Second, each of the polynomials to which they apply a low-degree test has total degree  $\tilde{\Omega}(\log^2|\mathcal{C}|)$ ; in comparison, the polynomial used in our MIP has total degree  $O(\log |\mathcal{C}|)$ . This means that each low-degree test in the MIP of [23] requires the prover to either evaluate the relevant polynomial at  $\tilde{\Omega}(\log^4|\mathcal{C}|)$  points or compute this many coefficients, and each such evaluation appears to require  $\tilde{\Omega}(|\mathcal{C}|\log |\mathcal{C}|)$  time.

Bitansky and Chiesa also showed how to transform any MIP with the properties guaranteed by Theorem 4.1 into a four-message complexity preserving argument system.

*Proof of Theorem 4.1.* The proof relies on the following lemma, which shows that it is possible to very efficiently transform an arbitrary RAM program into an arithmetic circuit  $\mathcal{C}$  for which there exist *cubic* extensions of add and mult can be evaluated in polylogarithmic time. Moreover, when applying the sum-check protocol to the polynomial  $h_q$  derived from these extensions, the prover  $\mathcal{P}_1$  can still be made to run in time  $O(|\mathcal{C}|\log|\mathcal{C}|)$ .

**Lemma 4.2.** Let M be an arbitrary (non-deterministic) Random Access Machine that on inputs of length n runs in time T(n) and space S(n). M can be transformed into an equivalent (non-deterministic) arithmetic circuit  $\mathcal{C}$  over a field  $\mathbb{F}$  of size polylog(T(n)). Moreover, there exist cubic extensions  $\widetilde{\text{add}}$  and  $\widetilde{\text{mult}}$  of the wiring predicates add and mult of  $\mathcal{C}$  that satisfy the following properties.

- 1. C has size  $O(T(n) \cdot \text{polylog}(T(n)))$ .

- 2. The cubic extensions add and mult of  $\mathcal{C}$  can each be evaluated in time  $O(\operatorname{polylog}(T(n)))$ .

- 3. An (input, witness) pair (x; w) that makes M accept can be mapped to a correct transcript W for C in time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$ . Furthermore, w is a substring of the transcript W, and any correct transcript W' for C possesses a witness w' for (M, x) as a substring.

- 4.  $\mathcal{P}_1$  can run in time  $O(|\mathcal{C}| \log |\mathcal{C}|)$  when applying the sum-check protocol to the polynomial  $h_q = \widetilde{G}_{x,y} \cdot g_q$  derived from  $\widetilde{\text{add}}$ ,  $\widetilde{\text{mult}}$ , and the transcript W (see Equation (1)).

- 5. C can be evaluated "gate-by-gate" in time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$ .

The proof of Lemma 4.2 adapts techniques for transforming RAMs into circuits pursued by Ben-Sasson et al. [15], combined with techniques of Thaler [74] for obtaining the appropriate cubic extensions. A detailed sketch of this result is in Appendix D.

Given a (non-deterministic) Random Access Machine M, let  $\mathcal C$  be the circuit whose existence is guaranteed by Lemma 4.2. Insights of CMT [31] show that each gate in the circuit  $\mathcal C$  contributes independently to each of  $\mathcal P_1$ 's messages. Thus,  $\mathcal P_1$  can compute each message in time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$  by evaluating the circuit gate-by-gate, computing the contribution of each gate to the current message, and "forgetting" the value of the gate immediately after. While this requires  $\mathcal P$  to reevaluate the circuit for every message,  $\mathcal P_1$  sends only  $3 \log |\mathcal C|$  many messages in total, and therefore revaluation of  $\mathcal C$  introduces only a  $O(\log |\mathcal C|)$  factor overhead in  $\mathcal P_1$ 's runtime. (To clarify, if we did not care about keeping the space complexity of  $\mathcal P_1$  small, then  $\mathcal P_1$  can store the value of each gate and avoid this overhead). We conclude that when applying our MIP protocol to  $\mathcal C$ ,  $\mathcal P_1$  runs in total time  $O(T(n) \cdot \operatorname{polylog}(T(n)))$  and space  $O(S(n) \cdot \operatorname{polylog}(T(n)))$ .

Similar observations imply that  $\mathcal{P}_2$  can be made to run within the same time and space bounds when applied to the circuit  $\mathcal{C}$ , completing the proof of the theorem.

**Proof-of-Knowledge.** Bitansky and Chiesa [23] also give a hardness assumption under which any complexity preserving MIP that satisfies a *proof-of-knowledge* (PoK) property can be transformed into a complexity preserving SNARK. In Appendix C, we show that our MIP satisfies this PoK property, and hence the transformation of [23] can turn it into a complexity-preserving SNARK.

## 5 Clover, the built system

As discussed earlier, Clover (the built system) does not yet incorporate complexity-preserving reductions from high-level programs into the circuits required by Theorem 4.1. Instead, Clover relies on an existing approach to circuit generation [26, 61, 70, 71, 76] that produces circuits for which the verifier cannot evaluate low-degree extensions add and mult in polylogarithmic time. However, even for these circuits, the multilinear extensions can be evaluated in time proportional to  $|\mathcal{C}|$  by iterating over every gate in  $\mathcal{C}$  and computing its contribution to the evaluation [31, 76]. Borrowing an idea from Allspice [76, §4.2], we move this computation to a setup phase and amortize its cost by reusing this work across a *batch* of inputs  $x^{(1)}, \ldots, x^{(\beta)}$ . Our built system includes some additional optimizations that require pre-processing (full details in Appendix B.2).

Costs of Clover. Figure 2 reports the concrete costs of our built system. To briefly compare these costs to those of built systems based on arguments with preprocessing [17, 18, 26, 61, 69], the costs for the prover and verifier in these systems are the same as, or lower than, Clover's—in *asymptotic* terms. However, in *concrete* terms, the argument systems require many expensive cryptographic operations. For instance, in Zaatar [69], each operation in the setup phase requires a modular exponentiation that costs two orders of magnitude more [69, §5.1] than a field operation—the only kind of operation required for Clover. Additional comparisons are in §2.

#### **6** Experimental evaluation

We are interested in two performance metrics: (1) the verifier's *break-even batch size*, i.e., the minimum number of computation instances that the verifier must outsource

| 222                                                                 | 6 (0   2  + 2 (    +       ))                                                                                                                                    |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V's setup costs V's per-instance costs                              | $f \cdot (9 \cdot  \mathcal{C}  + 3 \cdot ( x  +  y ))$<br>$f \cdot ((\log  \mathcal{C}  + 1)^2 + 11 \log  \mathcal{C}  +  x  +  y )$                            |

| $\frac{\mathcal{P}_1$ 's setup costs                                | $f \cdot (22.5 \mathcal{C} \log \mathcal{C}  + 3 \mathcal{C} )$                                                                                                  |

| $\mathcal{P}_1$ 's per-instance cost                                | $f \cdot (22.5 \mathcal{C} \log \mathcal{C}  + 5 \mathcal{C} )$ $f \cdot (18.5 \mathcal{C} \log \mathcal{C}  + 7 \mathcal{C} )$                                  |

| $\mathcal{P}_2$ 's setup costs $\mathcal{P}_2$ 's per-instance cost | $f \cdot 3 \mathcal{C}  \cdot (1 + \log  \mathcal{C} )^2$<br>$f \cdot  \mathcal{C}  \cdot (1 + \log  \mathcal{C} )^2$                                            |

| Network costs<br>Protocol rounds                                    | $ p  \cdot (\log^2  \mathcal{C}  + 15 \cdot \log  \mathcal{C}  + 5)$ $3 \cdot \log  \mathcal{C}  + 1 \text{ with } \mathcal{P}_1, 1 \text{ with } \mathcal{P}_2$ |

| Soundness error (§A)                                                | $\epsilon_{\text{Clover}} < 2^{-23} \text{ when }  p  \ge 300$<br>$\epsilon_{\text{Clover}} < 2^{-35} \text{ when }  p  \ge 400$                                 |

|x|, |y|: number of elements in input, output

$|\mathcal{C}|$ : number of gates in  $\mathcal{C}$

|p|: length of an element in  $\mathbb{F}$

Figure 2—Costs of Clover (the built system) for a computation represented as an arithmetic circuit  $\mathcal{C}$  with  $|\mathcal{C}|$  gates. f represents the cost of field multiplication.

in a batch before the cost of local execution exceeds the cost of verification, and (2) the prover's overhead, split into per-instance and setup costs (see Figure 2). We note that item (1) accounts for the verifier's per-instance verification time and per-computation setup cost (which is the dominant cost in all of the protocols in the literature).

**Points of comparison.** Besides local computation, our points of comparison are CMT-batching [76] (the refinement to CMT that is part of Allspice) and Zaatar [69]. To explain this choice of baseline, we give a ballpark comparison among three systems for verifiable computation: Zaatar [69], Pinocchio [61], and CMT-batching [76]. We choose these three because we are focused on the "back-end" in this paper. As noted in Section 2, the other systems for general-purpose verifiable computation—BCTV [17, 18], Pantry [26], and Buffet [77]—differ primarily in their "front-ends"; their back-end is Pinocchio or optimizations thereof.

For the verifier's costs, Zaatar's per-instance verification time is roughly three times Pinocchio's, but Pinocchio's setup costs are considerably larger [78, Figs. 2-3]; as a result, Pinocchio's break-even point is roughly twice Zaatar's [78, Fig. 4]. And when CMT is applicable, it has the best batch sizes in the literature, by several orders of magnitude [76]. For the prover's costs, Pinocchio's prover costs roughly twice Zaatar's; for details, see [78, Fig. 5][76, §8][76, Fig. 10][26, §2.3,§9]. Summarizing, CMT-batching and Zaatar do better on the key metrics (prover costs, verifier break-even points), so these are the comparison points for Clover.<sup>6,7</sup>

**Top-level summary of results.** Clover achieves break-even batch sizes that are competitive with CMT-batching (for computations for which CMT-batching even *has* a break-even batch size) and are significantly superior to Zaatar, while simultaneously yielding prover costs that are competitive to both.

**Method and setup.** We evaluate Clover on the following benchmark computations: (1)  $m \times m$  matrix multiplication (m=128), (2) evaluating a degree-2 polynomial in m variables (m=512), (3) finding the roots

<sup>&</sup>lt;sup>6</sup>An area where Zaatar is not the best is amortization behavior. Whereas Zaatar's setup costs amortize only over a batch, Pinocchio's set-up costs amortize over an indefinite number of instances of the same computation. And BCTV's amortize over an indefinite number of instances of all computations of the same length. Clover and Zaatar work under the same amortization model.

<sup>&</sup>lt;sup>7</sup>Our comparison here has considered the original version of Pinocchio. Very recently, BCTV [18] have released an optimized implementation of this protocol that achieves approximately a 5× performance improvement [2], which would imply a performance improvement over Zaatar of roughly 2.5×. Work is underway to incorporate this optimized protocol as a comparison point. In the meantime, our comparison to Zaatar provides a high-level illustration of Clover's costs compared to the systems based on arguments.

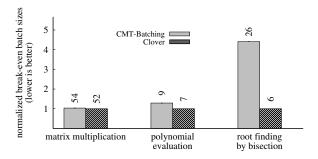

(a) Break-even batch sizes for matrix multiplication (m=128), polynomial evaluation (m=512), and root finding by bisection (m=256, L=8) under CMT-batching and Clover.

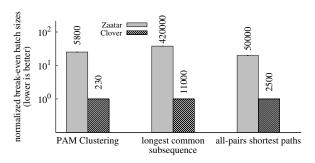

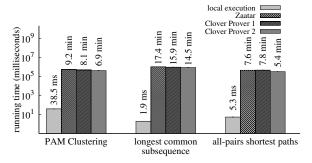

(b) Break-even batch sizes for PAM clustering (d=128, m=20), all-pairs shortest path (m=25), and longest common subsequence (m=300) under Zaatar and Clover. The y-axis is log-scaled.

Figure 3—Clover has a superior break-even size in all of our experiments.

of a degree-2 polynomial in m variables using bisection (m=256, L=8), (4) clustering a set of m data points, where each data points have d dimensions, using PAM clustering (d=128, m=20), (5) Floyd-Warshall all-pairs shortest paths in a graph with m vertices (m=25), and (6) finding the longest common subsequence of two length-m strings (m=300). These computations were expressed in a high-level language and automatically compiled into circuits. The sizes of the resulting circuits range from 1 million gates for polynomial evaluation to 12.6 million gates for longest common subsequence. We evaluated Clover against CMT-batching for the first three computations, and against Zaatar for the remaining ones.

We run CMT-batching and Zaatar over a finite field with a 128-bit prime modulus for computations that take integer inputs and a field with a 220-bit prime modulus for computations that take floating-point inputs. We run Clover with a 300-bit prime modulus field for all computations, corresponding to soundness error of at most  $2^{-23}$ . Costs grow roughly linearly with the bit length; for example, increasing the modulus to 400 bits to guarantee soundness error  $2^{-35}$  results in a 20–41% increase in the numbers reported below.

We run the verifier and provers on different machines in the same local cluster and use getrusage to measure their CPU usages. Each machine has two Intel Xeon E5-2680 2.7 GHz processors with 32GB of RAM (Clover required approximately 8GB of RAM in our largest experiment.) To compute the verifier's break-even batch size, we run one instance locally and one instance under verification (splitting the verifier's costs into setup and per-instance costs), then solve for the point  $\beta$  at which verification of  $\beta$  instances is cheaper running them locally.

Clover's break-even batch size. Figures 3(a) and 3(b) show Clover's break-even batch sizes in comparison to CMT-batching and Zaatar, respectively. Clover's break-even batch size is slightly smaller than CMT-batching's for matrix multiplication and polynomial evaluation and much smaller for root finding by bisection. Against Zaatar, Clover fared even better, achieving a break-even batch size that is  $20-40 \times$  smaller.

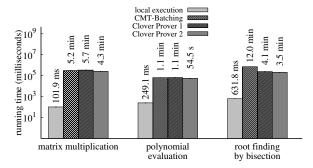

Clover's prover overhead. Figures 4(a) and 4(b) show the running time of Clover's two provers in comparison to the two baseline protocols' provers and to local execution of the computation. Clover's provers' per-instance costs are competitive with both baseline protocols' provers for all computations, despite having to work in a larger 300-bit modulus field. Its total per-instance prover overhead is no more than twice that of the baseline protocols, and it beats CMT-batching in the root finding computation. Clover's provers have setup costs that are not shown in the referenced figures. However, these costs are no more than  $3 \times$  each prover's per-instance costs; they can be easily amortized away at reasonable batch sizes.

In summary, while we have not yet implemented the full theory, we are encouraged by our results: Clover handles problems that existing interactive proofs cannot, and achieves performance comparable to, or better than, state of the art single-prover protocols that inherently require a pre-processing phase for the verifier.

(a) Per-instance running time of local executions and of the CMT-batching and Clover provers for matrix multiplication (m=128), polynomial evaluation (m=512), and root finding by bisection (m=256, L=8). The y-axis is log-scaled.

(b) Per-instance running time of local execution and of the Zaatar and Clover provers for PAM clustering (d=128, m=20), all-pairs shortest path (m=25), and longest common subsequence (m=300). The y-axis is log-scaled.

Figure 4—Clover's provers are competitive with both CMT-batching's and Zaatar's provers. Clover's first prover's setup costs (not shown) are  $1.5 \times$  its per-instance costs; Clover's second provers's setup costs are  $2-3 \times$  its per-instance costs; CMT-batching's prover's setup costs are  $0.3 \times$  its per-instance costs; and Zaatar's prover has no significant setup costs.

#### References

- [1] Open MPI (http://www.open-mpi.org).

- [2] https://github.com/scipr-lab/libsnark, 2014.

- [3] W. Aiello, S. N. Bhatt, R. Ostrovsky, and S. Rajagopalan. Fast verification of any remote procedure call: Short witness-indistinguishable one-round proofs for np. In U. Montanari, J. D. P. Rolim, and E. Welzl, editors, *ICALP*, volume 1853 of *Lecture Notes in Computer Science*, pages 463–474. Springer, 2000.

- [4] P. A. Alsberg and J. D. Day. A principle for resilient sharing of distributed resources. pages 562–570, 1976.

- [5] S. Alsouri, S. Katzenbeisser, and S. Biedermann. Trustable outsourcing of business processes to cloud computing environments. In *The Conference on Network and System Security (NSS)*, 2011.

- [6] D. P. Anderson, J. Cobb, E. Korpela, M. Lebofsky, and D. Werthimer. SETI@home: An experiment in public-resource computing. *CACM*, 45(11):56–61, Nov. 2002.

- [7] S. Arora and B. Barak. Computational Complexity: A modern approach. Cambridge University Press, 2009.

- [8] S. Arora, C. Lund, R. Motwani, M. Sudan, and M. Szegedy. Proof verification and the hardness of approximation problems. *J. of the ACM*, 45(3):501–555, May 1998.

- [9] S. Arora and S. Safra. Probabilistic checking of proofs: a new characterization of NP. *J. of the ACM*, 45(1):70–122, Jan. 1998.

- [10] S. Arora and M. Sudan. Improved low-degree testing and its applications. *Combinatorica*, 23(3):365–426, 2003.

- [11] L. Babai. Trading group theory for randomness. In STOC, 1985.

- [12] L. Babai, L. Fortnow, and C. Lund. Non-deterministic exponential time has two-prover interactive protocols. *Computational Complexity*, 1(1):3–40, 1991.

- [13] B. Barak and O. Goldreich. Universal arguments and their applications. SIAM J. Comput., 38(5):1661–1694, 2008.

- [14] M. Ben-Or, S. Goldwasser, J. Kilian, and A. Wigderson. Multi-prover interactive proofs: How to remove intractability assumptions. In J. Simon, editor, *STOC*, pages 113–131. ACM, 1988.

- [15] E. Ben-Sasson, A. Chiesa, D. Genkin, and E. Tromer. Fast reductions from RAMs to delegatable succinct constraint satisfaction problems. In *ITCS*, Jan. 2013.

- [16] E. Ben-Sasson, A. Chiesa, D. Genkin, and E. Tromer. On the concrete-efficiency threshold of probabilistically-checkable proofs. In *STOC*, June 2013.

- [17] E. Ben-Sasson, A. Chiesa, D. Genkin, E. Tromer, and M. Virza. SNARKs for C: Verifying program executions succinctly and in zero knowledge. In *CRYPTO*, pages 90–108, Aug. 2013.

- [18] E. Ben-Sasson, A. Chiesa, E. Tromer, and M. Virza. Succinct non-interactive zero knowledge for a von Neumann architecture. In *USENIX Security*, Aug. 2014.

- [19] E. Ben-Sasson, O. Goldreich, P. Harsha, M. Sudan, and S. Vadhan. Robust PCPs of proximity, shorter PCPs and applications to coding. *SIAM J. on Comp.*, 36(4):889–974, Dec. 2006.

- [20] E. Ben-Sasson and M. Sudan. Short PCPs with polylog query complexity. SIAM J. on Comp., 38(2):551–607,

- May 2008.

- [21] N. Bitansky, R. Canetti, A. Chiesa, and E. Tromer. From extractable collision resistance to succinct non-interactive arguments of knowledge, and back again. In *ITCS*, pages 326–349, Jan. 2012.

- [22] N. Bitansky, R. Canetti, A. Chiesa, and E. Tromer. Recursive composition and bootstrapping for SNARKs and proof-carrying data. In *STOC*, pages 111–120, June 2013.

- [23] N. Bitansky and A. Chiesa. Succinct arguments from multi-prover interactive proofs and their efficiency benefits. In *CRYPTO*, pages 255–272, 2012.

- [24] N. Bitansky, A. Chiesa, Y. Ishai, R. Ostrovsky, and O. Paneth. Succinct non-interactive arguments via linear interactive proofs. In *IACR TCC*, Mar. 2013.

- [25] G. Brassard, D. Chaum, and C. Crépeau. Minimum disclosure proofs of knowledge. *J. of Comp. and Sys. Sciences*, 37(2):156–189, 1988.

- [26] B. Braun, A. J. Feldman, Z. Ren, S. Setty, A. J. Blumberg, and M. Walfish. Verifying computations with state. In *SOSP*, 2013.

- [27] R. Canetti, B. Riva, and G. Rothblum. Practical delegation of computation using multiple servers. In *ACM CCS*, 2011.

- [28] R. Canetti, B. Riva, and G. N. Rothblum. Refereed delegation of computation. *Inf. Comput.*, 226:16–36, 2013.

- [29] M. Castro and B. Liskov. Practical Byzantine fault tolerance and proactive recovery. *ACM Trans. on Comp. Sys.*, 20(4):398–461, Nov. 2002.

- [30] A. Chiesa and E. Tromer. Proof-carrying data and hearsay arguments from signature cards. In ICS, 2010.

- [31] G. Cormode, M. Mitzenmacher, and J. Thaler. Practical verified computation with streaming interactive proofs. In *ITCS*, 2012.

- [32] G. D. Crescenzo and H. Lipmaa. Succinct NP proofs from an extractability assumption. In A. Beckmann, C. Dimitracopoulos, and B. Löwe, editors, *CiE*, volume 5028 of *Lecture Notes in Computer Science*, pages 175–185. Springer, 2008.

- [33] I. Damgård, S. Faust, and C. Hazay. Secure two-party computation with low communication. In R. Cramer, editor, *TCC*, volume 7194 of *Lecture Notes in Computer Science*, pages 54–74. Springer, 2012.

- [34] I. Dinur. The PCP theorem by gap amplification. J. of the ACM, 54(3):12:1–12:44, June 2007.

- [35] C. Dwork, M. Langberg, M. Naor, K. Nissim, and O. Reingold. Succinct proofs for NP and spooky interactions. Manuscript, available at http://www.cs.bgu.il/~kobbi/papers/spooky\_sub\_crypto.pdf, 2004.

- [36] L. Fortnow, J. Rompel, and M. Sipser. On the power of multi-power interactive protocols. In *Structure in Complexity Theory Conference*, pages 156–161. IEEE Computer Society, 1988.

- [37] R. Gennaro, C. Gentry, B. Parno, and M. Raykova. Quadratic span programs and succinct NIZKs without PCPs. In *EUROCRYPT*, May 2013.

- [38] C. Gentry. A fully homomorphic encryption scheme. PhD thesis, Stanford University, 2009.

- [39] C. Gentry and D. Wichs. Separating succinct non-interactive arguments from all falsifiable assumptions. In *STOC*, pages 99–108, June 2011.

- [40] S. Goldwasser, Y. T. Kalai, and G. N. Rothblum. Delegating computation: Interactive proofs for muggles. In *STOC*, 2008.

- [41] S. Goldwasser, H. Lin, and A. Rubinstein. Delegation of computation without rejection problem from designated verifier CS-proofs. *IACR Cryptology ePrint Archive*, 2011:456, 2011.

- [42] S. Goldwasser, S. Micali, and C. Rackoff. The knowledge complexity of interactive proof systems. *SIAM J. on Comp.*, 18(1):186–208, 1989.

- [43] J. Groth. Short pairing-based non-interactive zero-knowledge arguments. In ASIACRYPT, 2010.

- [44] Y. Gurevich and S. Shelah. Nearly linear time. In A. R. Meyer and M. A. Taitslin, editors, *Logic at Botik*, volume 363 of *Lecture Notes in Computer Science*, pages 108–118. Springer, 1989.

- [45] A. Haeberlen, P. Kouznetsov, and P. Druschel. PeerReview: Practical accountability for distributed systems. In *SOSP*, 2007.

- [46] Y. Ishai, E. Kushilevitz, and R. Ostrovsky. Efficient arguments without short PCPs. In *Conference on Computational Complexity (CCC)*, 2007.

- [47] S. Jha, S. Katzenbeisser, C. Schallhart, H. Veith, and S. Chenney. Semantic integrity in large-scale online simulations. *ACM Transactions on Internet Technology (TOIT)*, 10(1), Feb. 2010.

- [48] Y. T. Kalai, R. Raz, and R. Rothblum. How to delegate computations: The power of no-signaling proofs. *Electronic Colloquium on Computational Complexity (ECCC)*, 20:183, 2013.

- [49] Y. T. Kalai, R. Raz, and R. D. Rothblum. Delegation for bounded space. In D. Boneh, T. Roughgarden, and

- J. Feigenbaum, editors, STOC, pages 565–574. ACM, 2013.

- [50] G. O. Karame, M. Strasser, and S. Capkun. Secure remote execution of sequential computations. In *Intl. Conf. on Information and Communications Security*, 2009.

- [51] J. Kilian. A note on efficient zero-knowledge proofs and arguments (extended abstract). In STOC, 1992.

- [52] G. Kol and R. Raz. Competing provers protocols for circuit evaluation. In R. D. Kleinberg, editor, *ITCS*, pages 473–484. ACM, 2013.

- [53] H. Lipmaa. Progression-free sets and sublinear pairing-based non-interactive zero-knowledge arguments. In *IACR TCC*, 2011.

- [54] C. Lund, L. Fortnow, H. J. Karloff, and N. Nisan. Algebraic methods for interactive proof systems. *J. of the ACM*, 39(4):859–868, 1992.